David Andres 是 Marvell Semiconductor 公司的一位設(shè)計(jì)工程師,提出了一種可加快串行/解串器(SerDes)接收器 BER 測(cè)試的方法;Chung Wu 是 Maxim Integrated Products 公司的產(chǎn)品定義師,運(yùn)用眼圖模板來(lái)定義 SerDes 接收器的性能;Christopher J. Loberg 是 Tektronix 公司市場(chǎng)開(kāi)發(fā)高級(jí)經(jīng)理,利用波形發(fā)生器來(lái)創(chuàng)建測(cè)試信號(hào)。

Andres 花了數(shù)年時(shí)間來(lái)評(píng)估 SerDes 接收器。在那段時(shí)間,他開(kāi)發(fā)了一種技巧,使他在測(cè)試數(shù)十個(gè)器件時(shí),可以將接收器測(cè)試時(shí)間從數(shù)小時(shí)縮短至數(shù)分鐘。在為 Marvell 的其他工程師構(gòu)建其他評(píng)估系統(tǒng)時(shí),他還發(fā)現(xiàn)了一些簡(jiǎn)化測(cè)試設(shè)置和降低成本的方法。

一些客戶要求 Andres 針對(duì)低達(dá) 10–18 的 BER(每 1018 個(gè)比特的誤碼少于 1 個(gè))進(jìn)行測(cè)試,但大多數(shù)客戶均要求驗(yàn)證每 1012 個(gè)比特的 BER。在這些誤碼比率下,速度為 2.5Gbps 的完整 BER 測(cè)試可能需要 6 分 40 秒。為了獲得 99% 的“不會(huì)出現(xiàn)一個(gè)比特誤碼”置信度,Andres 需要對(duì)每個(gè)器件運(yùn)行至少 100 次 BER 測(cè)試,總測(cè)試時(shí)間超過(guò) 11 個(gè)小時(shí)。

由于 Andres 一般要為新設(shè)計(jì)、變更的設(shè)計(jì)、需要抽查的設(shè)計(jì)測(cè)試多達(dá) 50 個(gè)器件,因此需要縮短測(cè)試時(shí)間。通過(guò)設(shè)置一項(xiàng)提高誤碼出現(xiàn)概率的測(cè)試,Andres 可把每個(gè)器件的測(cè)試時(shí)間縮短至數(shù)秒。加快的測(cè)試為他帶來(lái)了足夠的“被測(cè)器件(DUT)將達(dá)到可接受的 BER 性能”的置信度。

添加時(shí)序變化

為了加快測(cè)試,Andres 為數(shù)據(jù)流添加了數(shù)量受控的時(shí)序變化(抖動(dòng)),使抖動(dòng)與眼圖模板規(guī)范重疊。在一項(xiàng)應(yīng)用中,他利用 7 比特偽隨機(jī)比特序列(PRBS7),在眼圖模板內(nèi)為每 127 個(gè)比特產(chǎn)生了 4 個(gè)邊沿。添加的抖動(dòng)產(chǎn)生了足夠的時(shí)序變化來(lái)預(yù)測(cè)接收器的性能。他還利用了 PRBS23、PRBS31 和其他比特模式。

Andres 結(jié)合兩種技巧為串行數(shù)據(jù)流添加受控的抖動(dòng):過(guò)采樣和混頻。過(guò)采樣需使用速度四倍于相關(guān)比特率的模式發(fā)生器。他使用 10Gbps 模式發(fā)生器來(lái)構(gòu)建 2.5Gbps PCI Express(PCIe)Generation 1 數(shù)據(jù)流。

為了從 10Gbps 信號(hào)得到穩(wěn)定的 2.5Gbps 數(shù)據(jù)流,Andres 用 4 個(gè)連續(xù)1(或十六進(jìn)制的單個(gè) F)得到了 2.5Gbps 的單個(gè)的1比特,2.5Gbps 的單個(gè) 0 比特則是由 10Gbps 的 4 個(gè)連續(xù)的 0 比特得到的。然后,他移動(dòng)邊沿時(shí)序來(lái)創(chuàng)建抖動(dòng)。

Andres 說(shuō):“借助 10Gbps 模式,就能把任何上升沿或下降沿的時(shí)序改變 0.25 個(gè)單位間隔(UI)。利用兩個(gè)邊沿,就能為信號(hào)添加 0.5 UI 的抖動(dòng)。還可以在模式中改變最差情形抖動(dòng)的位置。測(cè)試人員可以檢查許多不同位置,然后向設(shè)計(jì)師提供反饋,說(shuō)明模式中的弱點(diǎn)出現(xiàn)在何處。DUT 在一個(gè)方向能處理的抖動(dòng)比另一個(gè)方向高得多。”

圖 1 展現(xiàn)的是Andres 做法。上方的軌跡表明 2.5Gbps 的 4 個(gè)比特(1010),沒(méi)有添加抖動(dòng)(邊沿未移動(dòng))。在 10Gbps 時(shí),模式是由十六進(jìn)制 F0F0 表示的。下方的軌跡是 2.5Gbps 的一系列 4 比特(1,0,0,1),但 0 比特和隨后的 1 比特之間的上升沿提前 0.25 UI 出現(xiàn)了。

Andres 的實(shí)現(xiàn)方法是在 10Gbps 利用十六進(jìn)制 1(二進(jìn)制 0001)來(lái)代替二進(jìn)制 0000 后接十六進(jìn)制 F(二進(jìn)制 1111)。通過(guò)反復(fù)改變比特模式,Andres 能在 2.5Gbps 流中創(chuàng)建抖動(dòng)。

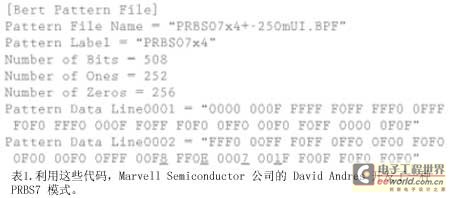

表 1 列出了 Andres 用于開(kāi)發(fā) PRBS7 模式的代碼。Pattern Data Line0002 中帶有下劃線的 4 個(gè)數(shù)字表示被縮短或延長(zhǎng) 0.25 UI 的比特。例如,“8”表示前一個(gè)比特的延遲下降沿,而“E”表示后一個(gè)比特的提前下降沿。

過(guò)采樣過(guò)程沒(méi)有為 Andres 提供足夠的抖動(dòng)以達(dá)到測(cè)試 PCIe 接收器所需的 0.65 UI 抖動(dòng)。圖 2 表明當(dāng)比特邊沿侵入眼圖模板(鉆石)時(shí),就會(huì)出現(xiàn)誤碼。Andres 利用混頻來(lái)添加正弦抖動(dòng)(Sj),以便覆蓋其余部分。事實(shí)上,他能產(chǎn)生足夠的時(shí)序變化來(lái)完全閉合眼圖。

圖 2 中標(biāo)明閉合眼圖寬度的光標(biāo)對(duì)應(yīng)于比特邊沿之間的 39 皮秒時(shí)間,并表示眼圖閉合。波形上方的直方圖表明邊沿時(shí)序的分布。抖動(dòng)覆蓋大約 53 皮秒的范圍,抖動(dòng)的其余 14 皮秒來(lái)自數(shù)據(jù)相關(guān)抖動(dòng)(DDj)和隨機(jī)抖動(dòng)(Rj)。Andres 說(shuō):“我不喜歡隨機(jī)抖動(dòng),因?yàn)樗茈y量化和調(diào)試。隨機(jī)抖動(dòng)隨著測(cè)量時(shí)間的延長(zhǎng)而增加。”