中頻采樣廣泛應(yīng)用于軟件無(wú)線電、數(shù)字中頻接收機(jī)、基站系統(tǒng)等通信領(lǐng)域。高性能的中頻采樣系統(tǒng)往往要求具備高信噪比、靈活可變的采樣頻率,支持高速高精度采樣。根據(jù)以上要求。這里設(shè)計(jì)并實(shí)現(xiàn)了一種高性能中頻采樣系統(tǒng)。

1 系統(tǒng)總體設(shè)計(jì)

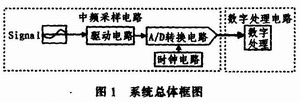

圖1為中頻采樣系統(tǒng)總體設(shè)計(jì)框圖。由圖1可知,該系統(tǒng)主要由驅(qū)動(dòng)電路、A/D轉(zhuǎn)換電路、時(shí)鐘電路3部分組成。

1.1 驅(qū)動(dòng)電路

信號(hào)A/D轉(zhuǎn)換前往往需要進(jìn)行以下處理:1)放大或衰減,使輸入信號(hào)的電平與A/D轉(zhuǎn)換器的所需電平相吻合;2)直流補(bǔ)償或電平轉(zhuǎn)換,通過(guò)補(bǔ)償提高或降低直流電平使之符合A/D轉(zhuǎn)換器的工作電平;3)濾波。濾除信號(hào)雜波使頻帶寬度符合A/D轉(zhuǎn)換器的要求。采用運(yùn)算放大器設(shè)計(jì)的驅(qū)動(dòng)電路可以很好的完成上述處理。

使用運(yùn)算放大器作A/D轉(zhuǎn)換器的接口還可作為緩存。大部分的A/D轉(zhuǎn)換器并不能獲得與輸入電壓范圍相符合的輸入信號(hào),只有極少的情況下是相符的,這時(shí)需要在輸入信號(hào)與A/D轉(zhuǎn)換器之間加入一個(gè)緩存運(yùn)放,這樣可以解決以下問(wèn)題:1)阻抗匹配,信號(hào)源往往并不是該系統(tǒng)設(shè)計(jì)所需的低阻抗,A/D轉(zhuǎn)換器的輸入將影響信號(hào)源。通常運(yùn)算放大器緩存具有高輸入阻抗,因此它不會(huì)對(duì)信號(hào)源產(chǎn)生影響。另外其低輸出阻抗有益于A/D轉(zhuǎn)換器的驅(qū)動(dòng);2)減小容性負(fù)載的影響。大多數(shù)的A/D轉(zhuǎn)換器除在輸入端具有電阻特性外,還具有電容效應(yīng)。因此需要額外的補(bǔ)償電路.通常用電阻或電容。運(yùn)算放大器的低輸出阻抗特性使其解決上述問(wèn)題;3)將單端信號(hào)轉(zhuǎn)換為差分信號(hào),許多A/D轉(zhuǎn)換器使用差分輸入,而大多數(shù)信號(hào)是單端的。運(yùn)算放大器可以完成這一轉(zhuǎn)換。

1.2 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換器的性能指標(biāo)主要分為靜態(tài)參數(shù)和動(dòng)態(tài)參數(shù)2種。靜態(tài)參數(shù)是指A/D轉(zhuǎn)換電路在低頻或直流下的性能參數(shù),而動(dòng)態(tài)參數(shù)則是指中頻或射頻信號(hào)輸入時(shí)的性能參數(shù)。對(duì)于中頻采樣系統(tǒng)來(lái)說(shuō),由于輸入信號(hào)頻率較高,其動(dòng)態(tài)特性對(duì)反映電路的性能具有更大意義。重要的動(dòng)態(tài)特性指標(biāo)包括:信噪比RSN、無(wú)雜散動(dòng)態(tài)范圍SFDR、有效比特位ENOB、積分非線性INL、微分非線性DNL等。

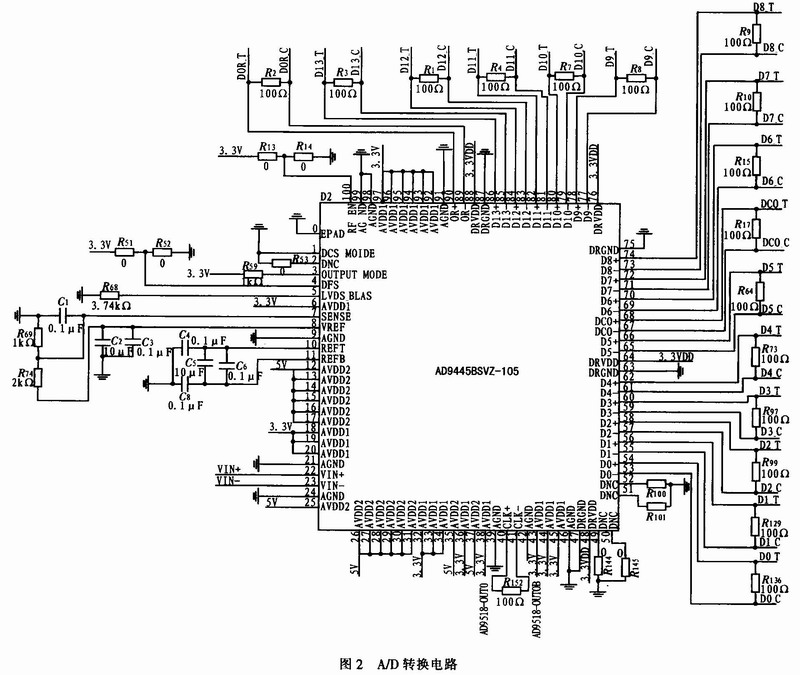

一個(gè)高性能的中頻采樣系統(tǒng)對(duì)噪聲性能的要求很高,A/D轉(zhuǎn)換器的噪聲來(lái)源通常有:A/D轉(zhuǎn)換器失真和量化噪聲,A/D轉(zhuǎn)換器等價(jià)輸入噪聲,內(nèi)部抽樣保持電路的孔徑抖動(dòng),不良的接地和退耦設(shè)計(jì),外部驅(qū)動(dòng)放大器的噪聲,不良的布局和信號(hào)走線設(shè)計(jì),采樣時(shí)鐘噪聲,外部電源噪聲。針對(duì)以上噪聲來(lái)源,該系統(tǒng)設(shè)計(jì)采用以下方法,力求減小噪聲的引入:所有芯片的電源部分都采用鉭電解電容與大面積,低阻抗的地層相退耦,用于去除低頻噪聲;使用鐵氧體磁珠去除電源的高頻噪聲;模擬地與數(shù)字地分離。A/D轉(zhuǎn)換電路如圖2所示。

1.3 時(shí)鐘電路

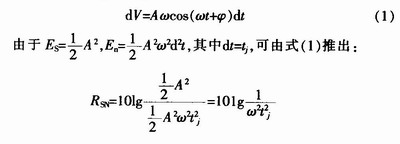

中頻采樣系統(tǒng)的時(shí)鐘抖動(dòng)會(huì)對(duì)系統(tǒng)性能產(chǎn)生很大影響,并且隨著輸入信號(hào)頻率的增加,這種影響越來(lái)越明顯。設(shè)輸入信號(hào)V=Asin(ωt+ψ),采樣時(shí)鐘抖動(dòng)為dt,信號(hào)能量為Es,噪聲能量為En,則有:

式(2)是在假設(shè)信號(hào)為正弦信號(hào)輸入的基礎(chǔ)上推導(dǎo)出來(lái)的。而對(duì)于任意信號(hào),都可以看成是單頻(正弦)信號(hào)的組合,所以,式(2)具有通用性。因此,在已知輸入信號(hào)頻率fin及采樣時(shí)鐘抖動(dòng)tj的情況下,A/D轉(zhuǎn)換器的信噪比被要求限制在-201g2πfintj以下,該信噪比與采樣時(shí)鐘fs無(wú)關(guān),卻與輸入信號(hào)的頻率fin相關(guān)。

2 系統(tǒng)硬件設(shè)計(jì)

2.1 A/D轉(zhuǎn)換電路設(shè)計(jì)

采用AD9445作為A/D轉(zhuǎn)換電路的核心器件.該器件是一款適用于中頻采樣的14位,單片集成A/D轉(zhuǎn)換器。它采用3.3 V和5.0 V雙電源供電,支持差分信號(hào)的時(shí)鐘輸入,支持CMOS、LVDS 2種數(shù)據(jù)輸出格式。其重要引腳功能如下:DCS MODE:時(shí)鐘占空周期穩(wěn)定器控制引腳,該引腳為低電平時(shí)可以起到穩(wěn)定時(shí)鐘周期占空比的作用。

OUTPUT MODE:將輸出數(shù)據(jù)電平選擇為CMOS電平,或者LVDS電平,為了獲取更高的性能,采用LVDS電平。

DFS:數(shù)據(jù)格式選擇。可以將輸出數(shù)據(jù)格式設(shè)置為二進(jìn)制補(bǔ)碼或者偏置二級(jí)制格式。

VREF:配置該引腳可設(shè)置其內(nèi)部參考電壓。

SENCE:配合VREF引腳完成內(nèi)部參考電壓的設(shè)置。

REFT,REFB:差分參考輸出引腳。

VIN+,VIN-:輸入電壓引腳。

CLK+,CLK-:采樣時(shí)鐘輸入引腳。

D0~D13:輸出引腳。

DC0:數(shù)據(jù)時(shí)鐘輸出引腳。

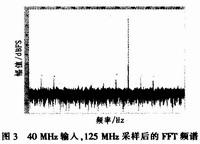

目前,主流中頻采樣A/D轉(zhuǎn)換器都采用差分信號(hào)輸入。差分信號(hào)能有效地去除共模噪聲。提高系統(tǒng)的抗噪聲性能。這里采用LVDS模式的差分信號(hào)輸入。電路設(shè)計(jì)如圖2所示。經(jīng)過(guò)調(diào)試。本系統(tǒng)在輸入中頻單頻信號(hào)頻率為40 MHz的情況下。信噪比可達(dá)77.4 dB,,其頻譜如圖3所示。

2.2 A/D轉(zhuǎn)換器前端運(yùn)放電路

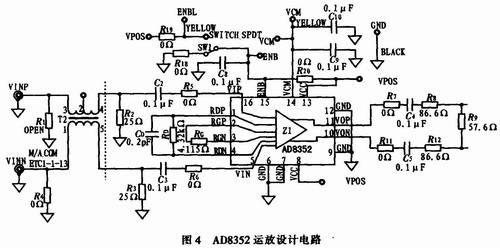

該系統(tǒng)設(shè)計(jì)采用AD8352型超低失真差分中頻放大器作為A/D轉(zhuǎn)換器的驅(qū)動(dòng)器件。其電路設(shè)計(jì)如圖4所示。

通過(guò)設(shè)置電阻RG的大小,可調(diào)節(jié)AD8352的放大倍數(shù),其范圍為:3~25 dB。CD和RD用于消除失真。通過(guò)前端的變壓器,可以將單端信號(hào)轉(zhuǎn)換為差分信號(hào),為AD8352提供差分信號(hào),使其具有更高的性能。

2.3 采樣時(shí)鐘電路

AD9445的采樣時(shí)鐘必須是一個(gè)高質(zhì)量,超低相位噪聲的時(shí)鐘源。根據(jù)上述理論分析可知,時(shí)鐘抖動(dòng)會(huì)對(duì)A/D轉(zhuǎn)換器的性能造成很大影響:

![]()

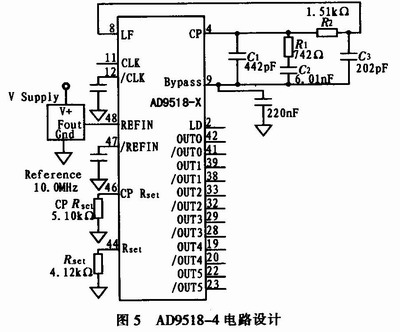

假設(shè)一個(gè)中頻輸入信號(hào)的頻率為70 MHz。采樣時(shí)鐘的抖動(dòng)為1 ps,則RSN=-201g(2πx70x106x10-12)=67.13 dB。結(jié)果說(shuō)明,時(shí)鐘的抖動(dòng)已經(jīng)將A/D轉(zhuǎn)換器的信噪比限制在67.13 dB以下。在輸入70 MHz時(shí)。如果使用一個(gè)高抖動(dòng)的時(shí)鐘源,則RSN性能很容易被降低3~4 dB。這里采用高性能時(shí)鐘分配芯片AD9518-4作為采樣時(shí)鐘,電路設(shè)計(jì)如圖5所示。

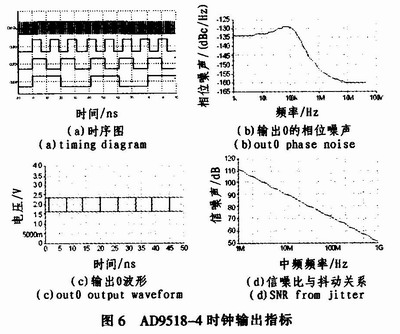

AD9518具有6路時(shí)鐘輸出,可分為3組,即同時(shí)可輸出3種不同頻率,并且每路的頻率輸出都可以通過(guò)軟件進(jìn)行配置調(diào)節(jié)。AD9518具有內(nèi)部鎖相環(huán)和壓控振蕩器電路,時(shí)鐘輸出范圍寬,時(shí)鐘抖動(dòng)小,輸出頻率靈活。AD9518,我們可以獲得高性能的采樣時(shí)鐘,同時(shí),通過(guò)對(duì)AD9518內(nèi)部寄存器的操作,改變采樣時(shí)鐘的頻率,從而方便地進(jìn)行中頻欠采樣或過(guò)采樣等信號(hào)處理工作。圖6顯示了本設(shè)計(jì)中時(shí)鐘采樣電路的主要性能指標(biāo)。

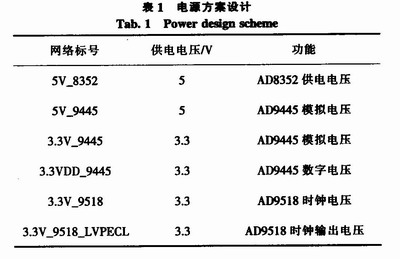

2.4 系統(tǒng)電源電路

電源噪聲是板級(jí)設(shè)計(jì)中的主要噪聲來(lái)源。為了盡量減小電源噪聲,使用低壓差線性穩(wěn)壓器(LDO)LT1763作為電源器件。針對(duì)運(yùn)放、A/D轉(zhuǎn)換器以及時(shí)鐘電路都要嚴(yán)格滿足模擬與數(shù)字電源分離的要求。本設(shè)計(jì)中的電源方案如表1所示,每種電壓都使用1片LT1763單獨(dú)供電,從而最大限度地防止數(shù)字電壓與模擬電壓之間的串?dāng)_以及不同供電電壓之間的串?dāng)_。

3 系統(tǒng)軟件設(shè)計(jì)

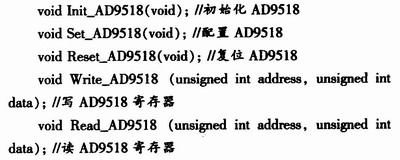

本系統(tǒng)軟件設(shè)計(jì)是采樣系統(tǒng)的時(shí)鐘芯片AD9518的軟件配置,AD9518是一款可調(diào)時(shí)鐘輸出頻率的多路時(shí)鐘輸出芯片。其輸出時(shí)鐘可以通過(guò)對(duì)其內(nèi)部寄存器的配置完成。配置軟件中的主要功能函數(shù)包括:

通過(guò)以上函數(shù)即可完成時(shí)鐘芯片的配置,達(dá)到在采樣過(guò)程中靈活變換時(shí)鐘的目的。

4 結(jié)束語(yǔ)

中頻采樣系統(tǒng)應(yīng)用廣泛,但由于前端驅(qū)動(dòng)設(shè)計(jì)問(wèn)題或采樣時(shí)鐘抖動(dòng)過(guò)大而限制采樣系統(tǒng)的整體性能。該設(shè)計(jì)方案已成功實(shí)現(xiàn),配合后端的數(shù)字處理電路,可以獲得高性能的中頻采樣信號(hào)。