電路功能與優(yōu)勢(shì)

圖1所示電路提供18位可編程電壓,其輸出范圍為−10 V至+10 V ,同時(shí)積分非線性為±0.5 LSB、微分非線性為±0.5 LSB,并且具有低噪聲特性。

該電路的數(shù)字輸入采用串行輸入,并與標(biāo)準(zhǔn)SPI、QSPI、MICROWIRE®和DSP接口標(biāo)準(zhǔn)兼容。對(duì)于高精度應(yīng)用,通過(guò)結(jié)合使用AD5781、ADR445 和 AD8676 等精密器件,該電路可以提供高精度和低噪聲性能。

基準(zhǔn)電壓緩沖對(duì)于設(shè)計(jì)至關(guān)重要,因?yàn)?a class="innerlink" href="http://forexkbc.com/tags/DAC" title="DAC" target="_blank">DAC基準(zhǔn)輸入的輸入阻抗與碼高度相關(guān),如果DAC基準(zhǔn)電壓源未經(jīng)充分緩沖,將導(dǎo)致線性誤差。AD8676開(kāi)環(huán)增益高達(dá)120 dB,經(jīng)過(guò)驗(yàn)證和測(cè)試,符合本電路應(yīng)用關(guān)于建立時(shí)間、失調(diào)電壓和低阻抗驅(qū)動(dòng)能力的要求。而AD5781經(jīng)過(guò)表征和工廠校準(zhǔn),可使用雙通道運(yùn)算放大器AD8676對(duì)其電壓基準(zhǔn)輸入進(jìn)行緩沖,從而進(jìn)一步增強(qiáng)配套器件的可靠性。

這一器件組合可以提供業(yè)界領(lǐng)先的18位分辨率、±0.5 LSB積分非線性(INL)和±0.5 LSB微分非線性(DNL),可以確保單調(diào)性,并且具有低功耗、小尺寸PCB和高性價(jià)比等特性。

圖1. 18位精密、±10 V電壓源(原理示意圖:未顯示去耦和所有連接)

電路描述

圖1所示數(shù)模轉(zhuǎn)換器(DAC)為AD5781,這是一款SPI接口的18位高壓轉(zhuǎn)換器,提供±0.5 LSB INL、±0.5 LSB DNL和7.5 nV/√Hz噪聲頻譜密度。另外,AD5781還具有極低的溫漂 (0.05 ppm/°C)特性。AD5781采用的精密架構(gòu)要求強(qiáng)制檢測(cè)緩沖其電壓基準(zhǔn)輸入,從而確保達(dá)到規(guī)定的線性度。選擇用于緩沖基準(zhǔn)輸入的放大器(B1和B2)應(yīng)具有低噪聲、低溫漂和低輸入偏置電流特性。針對(duì)此功能推薦用AD8676放大器,這是一款超精密、36 V、2.8 nV/√Hz雙通道運(yùn)算放大器,具有0.6 μV/°C低失調(diào)漂移和2 nA輸入偏置電流。此外,AD5781經(jīng)過(guò)表征和工廠校準(zhǔn),可使用該雙通道運(yùn)算放大器來(lái)緩沖其電壓基準(zhǔn)輸入,從而進(jìn)一步增強(qiáng)配套器件的可靠性。

在圖1中,AD5781配置為增益為2的模式,這樣便可以用單基準(zhǔn)電壓源來(lái)產(chǎn)生對(duì)稱的雙極性輸出電壓范圍。此工作模式采用外部運(yùn)算放大器(A2)和片內(nèi)電阻(參見(jiàn)AD5781數(shù)據(jù)手冊(cè))來(lái)提供大小為2的增益。這些內(nèi)部電阻相互之間以及與DAC梯形電阻之間均熱匹配,因而可實(shí)現(xiàn)比率熱跟蹤。輸出緩沖器同樣采用AD8676,其具有低噪聲和低漂移特性。該放大器(A1)還用于將低噪聲ADR445的+5 V基準(zhǔn)電壓放大至+10 V。此增益電路中的R2和R3為精密金屬薄片電阻,其容差和溫度系數(shù)電阻分別為0.01%和0.6 ppm/°C。要在整個(gè)溫度范圍內(nèi)達(dá)到最佳性能,R1和R2應(yīng)處于單個(gè)封裝內(nèi),如Vishay 300144或VSR144系列。R2和R3均選用1 kΩ,以便將系統(tǒng)噪聲保持在較低水平。R1和C1構(gòu)成低通濾波器,截止頻率大約為10 Hz。該濾波器用于衰減基準(zhǔn)電壓源噪聲。

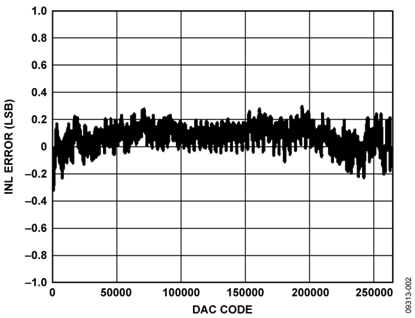

圖2. 積分非線性與DAC碼的關(guān)系

線性度測(cè)量

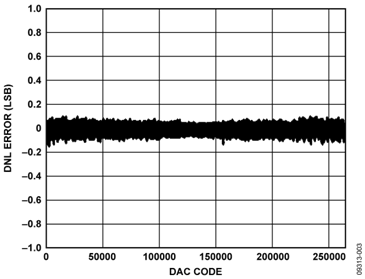

圖1所示電路的精密性能如圖2和圖3中的數(shù)據(jù)所示,這兩幅圖顯示了積分非線性和微分非線性隨DAC碼的變化情況。從圖中可以明顯看出,這兩種特性分別位于±0.5 LSB和±0.5 LSB的規(guī)格范圍內(nèi)。

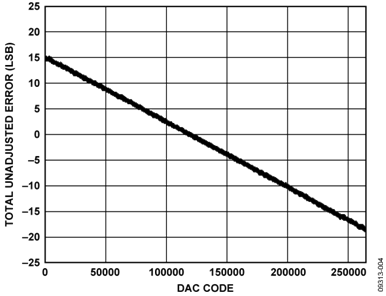

該電路的總非調(diào)整誤差由各種直流誤差共同組成,即INL誤差、失調(diào)誤差和增益誤差。圖4所示為總非調(diào)整誤差與DAC碼的關(guān)系圖。DAC碼為0和262,143時(shí)誤差最大。這是預(yù)期結(jié)果,具體是由基準(zhǔn)電壓輸出的絕對(duì)誤差、外部電阻R2和R3(見(jiàn)圖1)的不匹配以及AD5781內(nèi)部電阻RFB和R1(見(jiàn)圖5)的不匹配引起的。

圖3. 微分非線性與DAC碼的關(guān)系

圖4. 總非調(diào)整誤差與DAC碼的關(guān)系

圖5. 內(nèi)部增益為2的電路(原理示意圖)

基準(zhǔn)電壓絕對(duì)誤差的額定值為0.04%;本例中電阻R2和R3之間的不匹配度額定值為0.02%;內(nèi)部電阻R1和RFB之間的不匹配度額定值為0.01%。因此,總增益誤差為滿量程范圍的0.07%,即184 LSB。圖4顯示實(shí)測(cè)值為20 LSB(即滿量程范圍的0.007%),表明所有器件的性能都明顯優(yōu)于其額定容差。

噪聲測(cè)量

要實(shí)現(xiàn)高精度,電路輸出端的峰峰值噪聲必須維持在1 LSB以下,對(duì)于18位分辨率和20 V峰峰值電壓范圍則為76.29 μV。圖6所示為10秒內(nèi)在0.1 Hz至10 Hz帶寬內(nèi)測(cè)得的峰峰值噪聲。三種條件下的峰峰值分別為1.34 μV(中間電平輸出)、12.92 μV(滿量程輸出)和15.02 μV(零電平輸出)。中間電平輸出的噪聲最低,此時(shí)噪聲僅來(lái)自DAC內(nèi)核。選擇中間電平碼時(shí),DAC會(huì)衰減各基準(zhǔn)電壓路徑的噪聲貢獻(xiàn)。

圖6. 電壓噪聲(0.1 Hz至10 Hz帶寬)

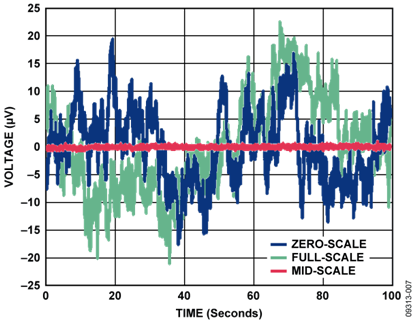

不過(guò),實(shí)際應(yīng)用中不會(huì)在0.1 Hz處有高通截止頻率來(lái)衰減1/f噪聲,但會(huì)在其通帶中包含低至DC的頻率;因此,測(cè)得的峰峰值噪聲更為實(shí)際,如圖7所示。本例中,電路輸出端的噪聲是100秒內(nèi)測(cè)得的,測(cè)量充分涵蓋低至0.01 Hz的頻率。截止頻率上限大約為14 Hz并受限于測(cè)量設(shè)置。對(duì)于圖7所示的三種條件,對(duì)應(yīng)峰峰值分別為1.61 μV(中間電平輸出)、43.33 μV(滿量程輸出)和36.89 μV(零電平輸出)。最差情況下的峰峰值 (43.33 μV)大致相當(dāng)于½ LSB。

圖7. 100秒內(nèi)測(cè)得的電壓噪聲

隨著測(cè)量時(shí)間變長(zhǎng),將包括較低頻率,而峰峰值將變大。頻率較低時(shí),溫度漂移和熱電偶效應(yīng)會(huì)變成誤差源。通過(guò)選擇熱系數(shù)較小的器件可以將上述效應(yīng)降至最小。在此電路中,低頻1/f噪聲的主要來(lái)源是基準(zhǔn)電壓源。另外,基準(zhǔn)電壓源的溫度系數(shù)值也是電路中最大的,為3 ppm/°C。

常見(jiàn)變化

AD5781支持各種不同的輸出范圍,從0 V至+5 V、最高±10 V以及該范圍內(nèi)的任意值。如果需要對(duì)稱輸出范圍,則可以使用增益為2的配置,如圖1所示。通過(guò)將AD5781內(nèi)部控制寄存器的RBUF位設(shè)為邏輯0,即可選中此模式。如果需要非對(duì)稱范圍,則可以在 VREFP和VREFN上施加單獨(dú)的基準(zhǔn)電壓源;而輸出緩沖器應(yīng)該如AD5781數(shù)據(jù)手冊(cè)中所述配置為提供單位增益。這可以通過(guò)將AD5781內(nèi)部控制寄存器的RBUF位設(shè)為邏輯1來(lái)實(shí)現(xiàn)。

電路評(píng)估與測(cè)試

圖1所示電路在經(jīng)過(guò)修改的AD5781評(píng)估板上構(gòu)建。有關(guān)AD5781評(píng)估板和測(cè)試方法的詳細(xì)信息,請(qǐng)參見(jiàn)“評(píng)估板用戶指南UG-184”。