0 引言

曼徹斯特" title="曼徹斯特">曼徹斯特碼是一種總線數(shù)據(jù)傳輸雙極性碼。在數(shù)字信號基帶傳輸中,通過這種信道編碼技術可使傳送數(shù)據(jù)同時攜帶時鐘信息,故也稱其為自同步曼徹斯特碼。在信道傳輸中曼徹斯特碼有很好的抗干擾能力。接收端可以將分離出的時鐘用于解碼,從而簡化了解碼過程。

針對曼徹斯特碼特點,可采用位同步方法提取時鐘,常采用濾波法和數(shù)字鎖相環(huán)法。濾波法采用的窄帶濾波器不適合數(shù)字電路使用。數(shù)字鎖相環(huán)法通過比較接收碼元和本地碼元為定時時鐘的相位來添加扣除時鐘脈沖,以達到調整相位的目的,但電路實現(xiàn)過于復雜。本文提出的時鐘分離電路比數(shù)字鎖相環(huán)簡單,而且提取出來的時鐘可以準確地采樣到曼徹斯特碼信號。

1 曼徹斯特碼

曼徹斯特碼是一種廣泛用于以太網(wǎng)、短距離無線通信、航空電子綜合系統(tǒng)中總線數(shù)據(jù)傳輸?shù)碾p極性碼。它的每個碼元中點都存在一個電平跳變,1信號為一個從1到0的負跳變;0信號為一個從0到1的正跳變。由于曼徹斯特碼在頻譜中存在很強的定式分量,解碼時可將分離出的時鐘用來解碼。另一方面,1553B" title="1553B">1553B傳輸電纜呈容性負載特性,所以在信號傳輸中,直流和低頻分量將受到很大的衰減。曼徹斯特碼頻譜中不存在直流分量,而且低頻分量也大大減小,很適合在1553B電纜中傳輸。

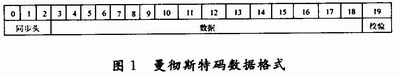

MIL-STD-1553B協(xié)議中采用的曼徹斯特碼數(shù)據(jù)格式如圖1所示。

同步頭:占三位碼元長度。命令字或狀態(tài)字同步頭的前1.5倍碼元長度為高電平;后1.5倍碼元長度為低電平,數(shù)據(jù)字同步頭剛好相反。同步頭用于區(qū)分字的類型以及標識字傳輸開始。

數(shù)據(jù):16位數(shù)據(jù)位。圖中bit3為數(shù)據(jù)最高位,依次遞減,bit18為數(shù)據(jù)最低位。

奇偶校驗位:這里采用奇校驗。將16位數(shù)據(jù)按位同或的結果作為奇校驗位。

2 曼徹斯特編碼器的設計" title="設計">設計

由于曼徹斯特碼的每個碼元在其中心存在電平跳變,所以編碼器的發(fā)送時鐘頻率至少應選擇信息傳輸速率的2倍頻。

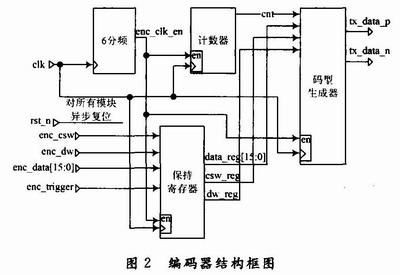

通常編碼器的實現(xiàn)方式有2種,基于移位寄存器,或者數(shù)據(jù)選擇器。移位寄存器型編碼器需要在編碼開始后將同步頭位、數(shù)據(jù)位、奇偶校驗位通過字符格式編排器編排成一個并行數(shù)據(jù),然后在發(fā)送時鐘的控制下串行移位輸出;數(shù)據(jù)選擇器型編碼器需要在編碼開始后啟動一個計數(shù)器,在計數(shù)器的控制下分別送出同步頭、數(shù)據(jù)位、奇偶效驗位。本文的編碼器采用后者,其結構框圖如圖2所示。

2.1 編碼過程

編碼過程如下:

(1)檢測編碼周期是否開始,編碼周期開始后將同步頭類型、16位并行數(shù)據(jù)存儲到內部寄存器中,與此同時計數(shù)器cnt開始計數(shù)。

(2)在計數(shù)器cnt的控制下通過碼型生成器發(fā)出同步頭、數(shù)據(jù)位、奇偶校驗位。

(3)在當前字的曼徹斯特碼發(fā)送完成后回到過程(1)等待發(fā)送下一個字

2.2 端口說明

rst_n為異步復位信號;clk為系統(tǒng)時鐘,頻率為信息傳輸速率的12倍;enc_trigger(輸入,高有效)的編碼開始的觸發(fā)信號;enc_csw(輸

入,高有效)表示要發(fā)送的字為命令字或狀態(tài)字;enc_dw(輸入,高有效)表示要發(fā)送的字為數(shù)據(jù)字;enc_data(輸入)表示16位要發(fā)送的并行數(shù)據(jù);tx_data_p(輸出)表示發(fā)出的曼徹斯特原碼;tx_data_n(輸出)表示發(fā)出的曼徹斯特反碼。

2.3 子模塊說明

(1)6分頻電路

將系統(tǒng)時鐘6分頻輸出占空比為1/6的編碼時鐘使能信號enc_clk_en,該信號的頻率為信息傳輸速率的2倍,其他3個模塊只有在采樣到該信號高電平后才會觸發(fā)。在復雜時序電路設計中通過引入時鐘使能信號可減少設計中的時鐘信號,提高電路的可靠性。

(2)保持寄存器

在enc_clk_en有效且采樣到enc_trigger為1時,將enc_csw,enc_dw,enc_data存入內部寄存器csw_reg,dw_reg,data_reg中。

(3)計數(shù)器

在enc_clk_en有效時采樣到enc_trigger為1時,將計數(shù)使能信號置為1,并在其控制下開始計數(shù),計數(shù)范圍為0~39。

(4)碼型生成器

碼型生成器通過對16位并行數(shù)據(jù)data_reg做同或運算產生奇偶校驗結果。在計數(shù)器cnt的控制下發(fā)送出曼徹斯特碼。發(fā)送過程如下(以tx_data_p說明):

cnt(0~5):根據(jù)同步頭類型,依次發(fā)送111000(csw_reg有效)或000111(dw_reg有效)。

cnt(6~37):發(fā)送數(shù)據(jù)位,在碼元前半個周期發(fā)送原碼,后半個周期發(fā)出反碼。

cnt(38~39):發(fā)送奇偶校驗位,計數(shù)到38時,發(fā)送奇偶校驗位原碼,39時發(fā)送其反碼。

3 曼徹斯特解碼器" title="解碼器">解碼器的設計

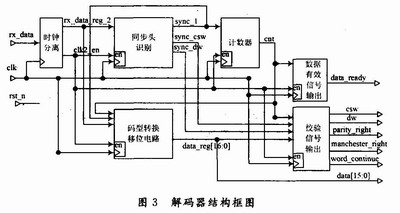

解碼器需要將收到的曼徹斯特碼解碼,得出16位并行數(shù)據(jù),并給出各種校驗結果。本文設計的解碼器邏輯結構如圖3所示。

3.1 解碼過程

(1)同步頭檢測,當檢測到同步頭后觸發(fā)整個解碼過程開始,并給出同步頭類型。

(2)檢測到同步頭后,計數(shù)器cnt開始計數(shù),在cnt的控制下進行解碼。包括碼型轉換與移位操作,同步頭類型輸出、曼徹斯特碼型校驗、奇偶校驗、字連續(xù)性校驗等。

(3)當碼的串并轉換以及各種校驗都完成后,給出并行數(shù)據(jù)和校驗結果信號,在cnt的控制下最終給出數(shù)據(jù)有效信號data_ready。協(xié)議模塊可在該信號有效(高電平)時檢測其他校驗信號,并決定是否取走并行數(shù)據(jù)。

3.2 端口說明

rst_n為異步復位信號;clk為系統(tǒng)時鐘,頻率是信息傳輸速率的12倍;rx_data(輸入)為收到的曼徹斯特原碼;data_ready(輸出,高有效)為數(shù)據(jù)有效信號,該信號有效期間可檢測其他校驗輸出信號,若數(shù)據(jù)有效可取走16位并行數(shù)據(jù);csw(輸出,高有效)為收到字類型為命令字或狀態(tài)字;dw(輸出,高有效)表示收到字類型為數(shù)據(jù)字;data(輸出)表示解碼輸出的16位并行數(shù)據(jù);parity_right(輸出,高有效)為奇偶校驗結果;manchester_right(輸出,高有效)為曼徹斯特碼型校驗結果;word_continue(輸出,高有效)為字連續(xù)性校驗結果,有效時表示當前收到的字與上一次收到字之間是連續(xù)的。

3.3 子模塊說明

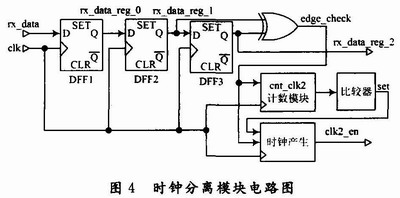

(1)時鐘分離模塊

時鐘分離模塊如圖4所示。

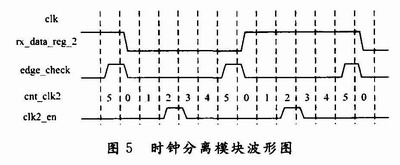

該模塊將曼徹斯特碼自帶的時鐘信號分離,得到clk2_en,并在該信號有效(高電平)時采樣,經(jīng)過三級寄存器保持輸出的曼徹斯特碼信號rx_data_reg_2。采樣時刻總出現(xiàn)在每個碼元正負電平的中點處,而這也是曼徹斯特碼采樣的最佳時刻,如圖5所示。

時鐘分離電路結構如圖4所示,收到的曼徹斯特碼rx_data為異步信號,通過DFF1,DFF2,DFF3三級采樣保持電路可消除亞穩(wěn)態(tài)。edge_ check在每個曼碼電平跳變后產生一個脈沖,該信號將對cnt_clk2和clk2_en同步清零,以達到調整相位的目的。cnt_clk2是一個6進制計數(shù)器,當計數(shù)到1時通過比較器給出同步置位脈沖set,它將對clk2_en同步置1。

(2)同步頭識別模塊

該模塊始終檢測同步頭,并給出同步頭類型。檢測方法如下,在采樣到時鐘使能信號clk2_en有效時,將rx_data_reg_2存入移位寄存器sync_reg[9:0]中,當檢測到sync_reg[5:0]為“111000”或“000111”時,給出同步頭有效信號sync_1,用于觸發(fā)計數(shù)器和碼型轉換移位模塊工作。

(3)計數(shù)模塊

計數(shù)器cnt是一個40進制計數(shù)器,在cnt的控制下完成整個解碼過程。當收到同步頭有效信號sync_1時,將計數(shù)器使能信號cnt_enb置為有效(高電平),并在其控制下開始計數(shù)。

(4)碼型轉換與移位電路

該模塊在移位使能信號data_sample有效,且采樣到采樣使能信號clk2_en時,將rx_data_reg_2移入一個17位寄存器data_reg[16:O]中,移位完成后,將得到一個16位并行數(shù)據(jù)data_reg[16:1]和一個奇偶校驗位data_reg[0]。

(5)校驗模塊

該電路將檢測并輸出同步頭類型、奇偶校驗結果、曼徹斯特碼檢測結果、字連續(xù)性檢測結果。

同步頭類型檢測:當cnt計數(shù)到3時,將同步頭檢測結果sync_csw和syn_dw分別寄存輸出給csw和dw。

奇偶校驗:將17位并行數(shù)據(jù)data_reg[16:O]按位同或后在cnt計數(shù)到33時將效驗結果輸出給parity_right。

曼徹斯特碼型的有效性校驗:對16位曼徹斯特碼和1位奇偶校驗碼的碼型進行檢測。當收到同步頭有效信號sync_1時將mangchester_rig-ht信號置為1,之后將每個碼元曼徹斯特檢測結果與mangchester_right做與運算,再寄存輸出到mangchester_right。當中間某個碼元曼徹斯特碼出錯時,mangchester_right將變?yōu)?,并在之后的檢測中一直保持為0,直到收到下一個字的sync_1信號。

字連續(xù)性檢測:若前一個字與當前字連續(xù),則在前一個字cnt計數(shù)到39時,當前字的同步頭有效信號sync_1應為高電平,若不連續(xù),sync _1為低電平。所以在cnt=39時將sync_1寄存輸出給word_continue可表征字的連續(xù)性。

(6)數(shù)據(jù)有效輸出模塊

當所有校驗和移位都完成時,在cnt為34~38之間輸出數(shù)據(jù)有效信號data_ready。

4 仿真及FPGA實現(xiàn)

在TESTBENCH中將編碼器曼徹斯特碼的輸出直接連到解碼器曼徹斯特碼的輸入端。圖6為正確曼徹斯特碼的時序仿真波形圖,傳輸速率為10 Mb/s,系統(tǒng)時鐘為120 MHz。圖6的上半部分為編碼器信號波形,下半部分為解碼器信號波形。發(fā)送消息為連續(xù)的4個字:第1個為命令字,后3個為數(shù)據(jù)字。

為了全面驗證設計功能,需要注入不同類型的錯誤來檢測解碼器的查錯能力。其中,包括同步頭類型錯,曼徹斯特碼型錯,奇偶校驗錯,字不連續(xù)錯等。測試過程完全按照GJB5186相關要求進行。

該設計在XlLINX公司Spartan3E系列的XC3S500E型號FPGA上進行了實現(xiàn)。當編解碼器時鐘約束為7 ns時,編碼器最高跑到143 MHz,解碼器最高到157 MHz。

5 結語

根據(jù)曼徹斯特碼型特點,設計出一種符合MIL-STD-1553B協(xié)議的曼徹斯特編解碼器,并兼容1 Mb/s和10 Mb/s兩種傳輸速率的協(xié)議。該設計通過了GJB5186規(guī)定的測試點驗證,實驗結果證明所設計的曼徹斯特編解碼器具有高速、高可靠性的特點。