0 引言

高速、寬分頻范圍的可編程頻率分頻器設(shè)計一直是射頻頻率綜合器設(shè)計中的難點,它的工作速度限制了頻率合成器輸出信號的最高頻率,它的相位噪聲影響頻率合成器的帶內(nèi)相位噪聲。文中設(shè)計的可編程分頻器應(yīng)用于移動數(shù)字電視接收機調(diào)諧芯片,該芯片兼容了DVB-H、DAB標(biāo)準,接收的頻段覆蓋了460~900 MHz,1 400~1 500 MHz這兩個頻段。根據(jù)整個芯片的系統(tǒng)方案設(shè)計,可編程分頻器的工作頻率為2.4~4.0 GHz,實現(xiàn)的分頻比范圍為240~400,且為連續(xù)的。目前高速可編程分頻器主要包括基于雙模預(yù)分頻的吞脈沖分頻器和基于基本分頻單元的多模分頻器兩種結(jié)構(gòu),前者因高速、結(jié)構(gòu)簡單等特點,被廣泛應(yīng)用在射頻頻率綜合器當(dāng)中,同時,整個可編程分頻器單元模塊都采用基于源極耦合(SCL)結(jié)構(gòu)的模擬電路實現(xiàn),相對于在低頻分頻部分采用數(shù)字標(biāo)準單元具有噪聲低、版圖面積小等優(yōu)點。檢測和置數(shù)邏輯時序的設(shè)計是可編程分頻器設(shè)計的重點,它直接影響到分頻器的工作頻率。本文中提出一種新的檢測和置數(shù)邏輯及電路實現(xiàn),使得整個可編程分頻器的工作頻率提高了1倍。本文首先給出r可編程分頻器設(shè)計的整體結(jié)構(gòu),著重描述了可編程分頻器檢測和置數(shù)邏輯電路的改進方案;最后,給出了版圖設(shè)計以及電路后仿真結(jié)果。

1 可編程分頻器的結(jié)構(gòu)

1.1 整體結(jié)構(gòu)設(shè)計

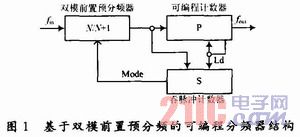

基于雙模預(yù)分頻器的可編程分頻器結(jié)構(gòu)如圖1所示,它由3部分構(gòu)成:N/N+1雙模前置預(yù)分頻器、可編程計數(shù)器、吞脈沖計數(shù)器。

輸入的頻率首先經(jīng)過預(yù)分頻器進行分頻,分頻比由吞脈沖計數(shù)器S給出一個信號Mode進行控制。可編程計數(shù)器P和吞脈沖計數(shù)器S同時開始減計數(shù),當(dāng)S計數(shù)器減計數(shù)減為0時,雙模預(yù)分頻器分頻比由N+1變?yōu)镹,S計數(shù)器停止計數(shù),P計數(shù)器繼續(xù)減計數(shù);當(dāng)P計數(shù)器減計數(shù)到0時,通過反饋回路使P,S計數(shù)器重新置數(shù),開始新一輪的計數(shù)。因此在每一次計數(shù)過程中首先進行了S次N+1分頻,再進行了P-S次N分頻,故輸出信號為:

![]()

分頻比M=PN+S。

根據(jù)調(diào)諧器芯片系統(tǒng)所需要的頻率合成范圍及精度要求以及采用的TSMC 0.13/μm工藝,該設(shè)計將雙模前置分頻器設(shè)計為4/5雙模分頻器,P計數(shù)器為7位、S計數(shù)器為2位。因此該可編程分頻器可實現(xiàn)的最大分頻比為515。

1.2 4/5預(yù)分頻器結(jié)構(gòu)

4/5預(yù)分頻器采用同步計數(shù)結(jié)構(gòu),其結(jié)構(gòu)如圖2所示,由3個SCL結(jié)構(gòu)的D觸發(fā)器和兩個與非門構(gòu)成。Mode信號為分頻比控制信號,當(dāng)Mode為“1”時,預(yù)分頻器分頻比為5,當(dāng)Mode為“0”時,預(yù)分頻器分頻比為4。由于4/5預(yù)分頻器直接工作在VCO的輸出頻率下,是整個可編程分頻器工作頻率最高的部分,因此這部分的電路設(shè)計主要偏重于速度,其功耗是最高的。這部分電路采用SCL結(jié)構(gòu)的模擬電路來實現(xiàn),SCL結(jié)構(gòu)的電路由開關(guān)管對尾電流的導(dǎo)通控制來實現(xiàn)邏輯電平的轉(zhuǎn)換,其工作速度高,滿足設(shè)計的要求。D觸發(fā)器由時鐘反連的2個D鎖存器構(gòu)成,同時為了減少門延遲以提高工作速度以及降低功耗,將與非邏輯門集成于D觸發(fā)器內(nèi),帶有與非邏輯的D觸發(fā)器電路如圖3所示。

1.3 可編程計數(shù)器和吞脈沖計數(shù)器設(shè)計

可編程計數(shù)器P和吞脈沖計數(shù)器S工作在分頻器頻率較低的頻段,采用簡單的異步計數(shù)器結(jié)構(gòu)實現(xiàn)分頻功能。這部分的電路一般有兩種實現(xiàn)方式:模擬電路和數(shù)字電路,在該設(shè)計采用基于SCL的模擬電路來實現(xiàn),相對于數(shù)字電路實現(xiàn)雖然消耗了一定的靜態(tài)功耗,但電路噪聲很低,版圖面積小,性能更加好。整個可編程分頻器結(jié)構(gòu)如圖4所示。

其中P計數(shù)器部分由7個帶置數(shù)功能的D觸發(fā)器構(gòu)成;S計數(shù)器部分由2個相同的D觸發(fā)器構(gòu)成,另外包括2個與非門構(gòu)成反饋邏輯控制預(yù)分頻器的分頻比;檢測和置數(shù)邏輯電路由5個與門和1個或門構(gòu)成。D觸發(fā)器和邏輯門電路都是由基于SCL結(jié)構(gòu)的模擬電路實現(xiàn),全差分結(jié)構(gòu)。在P計數(shù)器和S計數(shù)器中,每個D觸發(fā)器構(gòu)成一個2分頻器,每個2分頻器再級聯(lián)。檢測和置數(shù)邏輯的功能是使得P計數(shù)器和S計數(shù)器計數(shù)完后自動置數(shù),這部分的設(shè)計很關(guān)鍵,直接影響了整個分頻器的工作頻率,在本文中提出了一種新的檢測和置數(shù)邏輯,提高了分頻器的工作性能和工作頻率。以下通過對比傳統(tǒng)的檢測置數(shù)邏輯和改進后的檢測與置數(shù)邏輯來說明改進后的優(yōu)勢。

1.3.1 傳統(tǒng)的檢測與置數(shù)邏輯設(shè)計

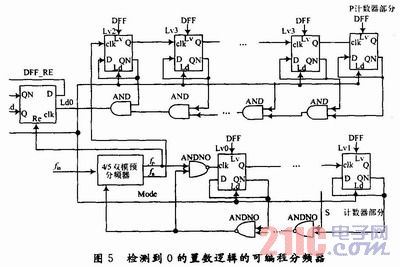

在傳統(tǒng)的基于雙模分頻器的可編程分頻器設(shè)計中,是對P計數(shù)器減計數(shù)到0時檢測,并通過一定的時序邏輯產(chǎn)生一個置數(shù)使能信號使得P計數(shù)器和S計數(shù)器進行置數(shù)。其檢測與置數(shù)邏輯電路如圖5所示,當(dāng)P計數(shù)器減計數(shù)到0時,P計數(shù)器中每個D觸發(fā)器Qn端輸出都為1,這時級聯(lián)的與門邏輯輸出從0跳變到1,形成一個上升沿(為一個檢測信號)。這個上升沿作為帶有復(fù)位功能的D觸發(fā)器(DFF-RE)時鐘輸入,DFF-RE的復(fù)位端由4/5預(yù)分頻器輸出控制,即在嚴格的時序控制下,當(dāng)檢測到P計數(shù)器減計數(shù)到0時產(chǎn)生一個上升沿信號,此時DFF-RE打開,這個上升沿信號使得DFF-RE輸出從0變?yōu)?,一段時間后DFF-RE關(guān)閉,故形成了一個置數(shù)脈沖,使得計數(shù)器重新置數(shù)。

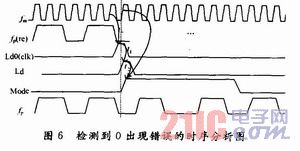

在這種結(jié)構(gòu)中,檢測和置數(shù)的整個過程必須在輸入信號的一個周期內(nèi)完成,從而限制了分頻器的工作頻率。下面通過對傳統(tǒng)檢測置數(shù)邏輯的時序分析來說明在輸入頻率較高時出現(xiàn)掉脈沖的現(xiàn)象,其時序圖如圖6所示,其中fin為分頻器的輸入信號,fp為4/5分頻器的輸出信號,同時作為DFF-RE的復(fù)位信號,Ld0為P計數(shù)器計數(shù)到0時的檢測組合邏輯電路輸出的信號,Ld為置數(shù)使能信號,即DFF-RE的輸出信號,Mode為控制4/5分頻器分頻數(shù)的信號。由圖中可知,在P計數(shù)器減計數(shù)到0時,檢測邏輯輸出一個脈沖(Ld0),從P計數(shù)到0到檢測脈沖信號產(chǎn)生有一個門延遲的t0,檢測脈沖到置數(shù)脈沖(Ld)的產(chǎn)生延遲時間為t1,Mode信號的產(chǎn)生延遲為t2。故從檢測到Mode信號上升沿的總延遲時間為t0+t1+t2,若這個總延遲時間大于了一個輸入信號的周期,如圖6所示,Mode信號控制的4/5預(yù)分頻器本該2次5分頻變?yōu)?次5分頻和1次4分

頻,從而出現(xiàn)了掉脈沖的現(xiàn)象,最終導(dǎo)致整個分頻比錯誤。

1.3.2 改進的檢測與置數(shù)邏輯設(shè)計

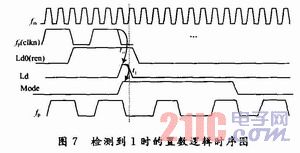

根據(jù)系統(tǒng)設(shè)計要求,分頻器工作的最高頻率需達到4.0 GHz,基于傳統(tǒng)的檢測置數(shù)邏輯的分頻器很難穩(wěn)定的工作在此頻率下。因此,在該設(shè)計采用在P計數(shù)器減計數(shù)到1檢測,通過一定的時序控制下,當(dāng)P計數(shù)器計數(shù)到0時置數(shù),這樣檢測和置數(shù)的過程在2個輸入脈沖周期內(nèi)完成,相對于計數(shù)到0檢測的分頻器,工作頻率可以提高2倍。以下具體分析改進后的檢測置數(shù)邏輯時序。在改進后的檢測置數(shù)邏輯中,如圖4所示,當(dāng)P計數(shù)器減計數(shù)到0000001時,P計數(shù)器中DFF3~DFF7的QN端輸出都為1,因此AND0輸出由0變?yōu)?,AND0輸出反相信號作為DFF-RE復(fù)位端信號,而4/5分頻器輸出的反相信號作為DFF-RE的時鐘信號。其檢測和置數(shù)時序邏輯圖如圖7所示,當(dāng)檢測到P計數(shù)到1后,DFF-RE便打開,置數(shù)脈沖的產(chǎn)生延遲為t0,Mode信號的產(chǎn)生延遲為t1,故由檢測到Mode上升沿信號的總延遲為t1+t2,相比圖6,少了一個門延遲,使得4/5預(yù)分頻器正確的進行了2次5分頻,避免了掉脈沖的現(xiàn)象。從對改進的檢測置數(shù)邏輯時序分析可知,改進后的設(shè)計使得可編程分頻器能夠工作在更高的頻率下。

2 電路版圖設(shè)計及仿真結(jié)果

2.1 可編程分頻器版圖設(shè)計

整體可編程分頻器的版圖如圖8所示,由于分頻器中各單元電路都是差分結(jié)構(gòu),需要考慮到器件的匹配設(shè)計,同時對單元電路需要合理布局,以減小關(guān)鍵路徑的連線延遲和節(jié)省版圖面積。

2.2 可編程分頻器仿真結(jié)果

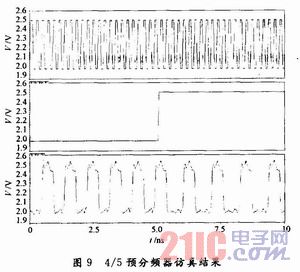

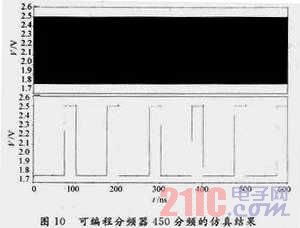

本文的仿真結(jié)果是在提取版圖寄生參數(shù)后,進行后仿真得到的結(jié)果。最高工作頻率可達4.5 GHz,在工作電壓2.5 V下消耗功率約為19 mW。圖9是工作頻率在4.5 GHz下,4/5分頻器的后仿真波形。圖10是可編程分頻器在4.5 GHz下,分頻比為450,P計數(shù)器預(yù)置數(shù)112,S計數(shù)器預(yù)置數(shù)2時的工作波形。從圖中可看出整個可編程分頻器能夠在4.5 GHz下實現(xiàn)正確的分頻。

3 結(jié)語

對于射頻頻段的頻率綜合器,分頻器成為了制約環(huán)路速度的一個瓶頸。本文通過對吞脈沖結(jié)構(gòu)的可編程分頻器的檢測和置數(shù)邏輯電路的改進,使得分頻器的工作速度可以達到4.5 GHz,滿足了多標(biāo)準移動數(shù)字電視接收機調(diào)諧芯片的系統(tǒng)設(shè)計指標(biāo),同時由于該分頻器具有連續(xù)的寬分頻比,使其也可應(yīng)用于其他射頻無線收發(fā)芯片中。同時,采用SCL結(jié)構(gòu)的模擬電路實現(xiàn)整個可編程分頻器使得芯片面積較小,約為106 μm×187μm。