目前,無線通信設備正朝著低電壓、低功耗、低噪聲和高線性度的趨勢發(fā)展。混頻器作為收發(fā)機中的關(guān)鍵模塊之一,對通信設備的上述性能產(chǎn)生直接的影響。隨著微電子工藝的發(fā)展, CMOS器件的柵長進一步縮小,MOS器件的過驅(qū)動電壓也進一步降低,這就為設計低壓低功耗的射頻電路提供了可能,但是依靠減小MOS器件的柵長降低工作電壓是有限的。因此,電路設計者把更多的注意力集中到電路拓撲結(jié)構(gòu)上,使設計具有低壓結(jié)構(gòu)的射頻電路成為了熱門課題。

傳統(tǒng)的Gilbert混頻器由跨導級、開關(guān)級、負載級堆疊組成,其結(jié)構(gòu)自下而上分別為跨導級、開關(guān)級、負載級。這種結(jié)構(gòu)中,所有的直流電流都流經(jīng)跨導級、開關(guān)級和負載級,跨導級與開關(guān)級電路都需要一個開啟電壓(VON ) ,負載級也會有一定的電壓降(VRL ) , 因此, 電源電壓的最小值Vdd,min = 2Von +VRL。如果采用低電源電壓,這種結(jié)構(gòu)不能保證所有的管子都工作在飽和區(qū)。也就是說, Gilbert混頻器不能滿足低電壓的要求, 需要對其做出改進, 如:文獻[2 - 3 ]提出省去尾電流管來減小電源電壓,文獻[ 4 - 11 ]用折疊結(jié)構(gòu)代替堆疊結(jié)構(gòu)來解決上述問題。

文獻[ 8 ]給出了折疊結(jié)構(gòu)和堆疊結(jié)構(gòu)的比較,折疊結(jié)構(gòu)增加了兩個射頻中斷電路和一個耦合電容。這樣對直流通道來說,跨導級與開關(guān)級、負載級的直流電路分開,兩條支路相互獨立,互不影響。電源電壓只需提供相當于一個開啟電壓(Von )的值就能使跨導管與開關(guān)管都工作在各自的飽和區(qū), 即電源電壓的最小值Vdd,min = Von + VRL 。達到了低電源電壓的目的。但是, 射頻中斷電路一般用LC 諧振網(wǎng)絡實現(xiàn),電感的使用增加了電路的版圖面積和噪聲。本文設計了一種新的折疊結(jié)構(gòu)混頻器,電路不使用具有大電感的LC諧振電路,工作于1. 2 V 電壓時,得到了低電壓、低功耗、低噪聲和高線性度的性能。

1 電路設計與分析

1. 1 電路拓撲結(jié)構(gòu)

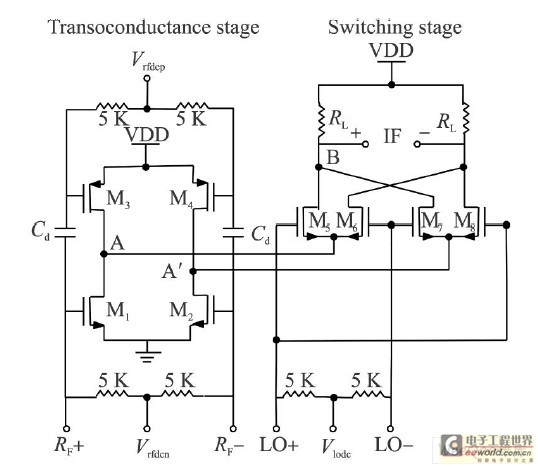

本文設計的折疊混頻器拓撲結(jié)構(gòu)如圖1所示,M1 ~M4 為跨導級,M5 ~M8 為開關(guān)級, RL 為負載電阻。RF輸入端接匹配網(wǎng)絡, IF輸出端接源跟隨器作為輸出緩沖電路( buffer) 。

圖1 交流耦合折疊混頻器拓撲結(jié)構(gòu)

該折疊混頻器電路的跨導級采用電流復用技術(shù),由NMOS管(M1、M2 ) 、PMOS管(M3、M4 )和隔直電容Cd 組成交流耦合互補跨導結(jié)構(gòu)。跨導級的輸出端(A、A′點)與開關(guān)管的源極相連。跨導級直接接于電源電壓,使得跨導管M1 和M2 的直流電流由兩部分組成,一部分來自M3 和M4 ,另一部分來自開關(guān)管和負載電阻,達到了低電源電壓的目的。

由于流經(jīng)開關(guān)級與負載級的電流很小,這樣一方面使得開關(guān)管產(chǎn)生的閃爍噪聲減小,另一方面負載電阻RL 值可以適當加大,從而提高了混頻器的轉(zhuǎn)換增益。所以該電路既滿足了低電壓的要求,又能保證混頻器在低電源電壓下有良好的性能。

1. 2 跨導電路設計

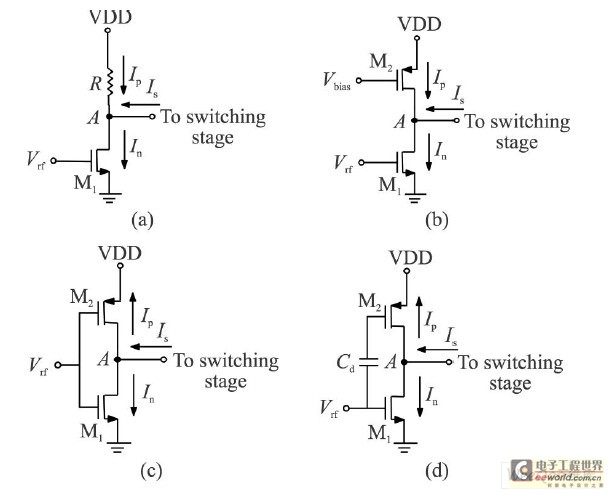

圖2是幾種折疊混頻器跨導電路。圖2 ( a)在跨導級NMOS管M1 漏端接負載電阻R ,M1 管的電流In 在A 點分流, 一部分流經(jīng)開關(guān)管( Is ) ,另一部分流經(jīng)負載電阻( Ir ) ,但是這種跨導電路的缺點是射頻信號一部分通過負載電阻R 泄露到交流地。

為了減少射頻信號的損失,必須增加電阻R,這樣又會使節(jié)點A 的直流電壓減小,在低電源電壓下,不能保證M1 管工作在飽和區(qū)。為了解決這個問題,用有源負載替代負載電阻R ,如圖2 ( b) 。但是,這里的PMOS管僅僅增大了節(jié)點A與電源電壓之間的阻抗,如果把M1 和M2 的柵極連起來,形成CMOS反相器結(jié)構(gòu),那么M2 在增加阻抗的同時還能跟M1共同放大射頻信號 ,如圖2 ( c) ,這樣就完全避免了射頻信號通過M2 泄露到交流地。由圖可知, Is =In + Ip ,總跨導gm = gm n + gm p ( gm n是NMOS管的跨導, gm p是PMOS管的跨導) ,所以CMOS反相器有效地提高了混頻器的轉(zhuǎn)換增益。

圖2 折疊混頻器的跨導級幾種結(jié)構(gòu)

再來分析一下該結(jié)構(gòu)的直流工作狀況,M1 和M2 的柵極加相同偏置電壓Vrfdc ,假設Vt 為MOS管的閾值電壓, Vovn為M1 的過驅(qū)動電壓, Vovp為M2 的過驅(qū)動電壓,則有: Vovn =Vrfdc - Vt , Vovp =Vdd - Vrfdc -Vt ,所以電源電壓最小值Vdd,min = Vovn + Vovp + 2Vt。

在0. 18μm CMOS工藝中, Vt 典型值為500 mV,因此用反相器作為跨導電路的混頻器只適用于1 V以上的電源電壓。為了使混頻器能滿足更低的電壓,在M1 和M2 之間增加隔直電容Cd ,M1 和M2 管偏置分開,如圖2 ( d) 。這種結(jié)構(gòu)稱為交流耦合互補跨導。假設Vrfdcn為M1 的偏置電壓, Vrfdcp為M2 的偏置電壓,則電源電壓的最小值Vdd,min = Vovn + Vovp + 2Vt+Vrfdcp - Vrfdcn ,可見,在Vrfdcn >Vrfdcp時, Vdd,min比常規(guī)反相器更小,適用于更低的工作電壓。

1. 3 性能分析

1. 3. 1 增益

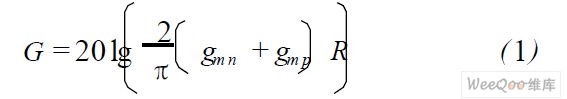

假設本振信號LO為理想方波信號, 則該混頻器(如圖1)的增益可表示為:

gm n是M1 和M2 的跨導, gm p是M3 和M4 的跨導, R 即負載電阻RL 的值。因為開關(guān)管的漏極電流很小,所以負載電阻值可以適當增加,由式( 1)知,混頻器的增益將隨之提高。值得注意的是, 增大負載電阻值的同時必須保證節(jié)點A 的直流電壓足夠使得M1 和M2 工作在飽和區(qū)。

1. 3. 2 噪聲系數(shù)

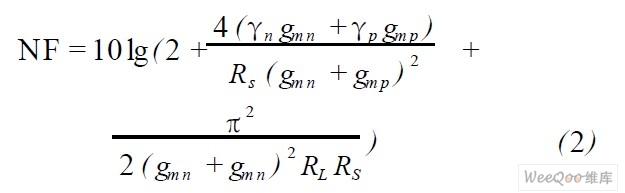

假設本振信號為理想方波信號,并考慮鏡像頻率的影響,噪聲系數(shù)的表達式為:

RS 為源阻抗, RL 為負載電阻值, 系數(shù)γn 對長溝道晶體管來說等于2 /3,對于亞微米MOSFET,γn 的值較大。由式(2)知,只要選擇合理的偏置電壓Vrfdcn、Vrfdcp和M1~M4的寬長比, 噪聲系數(shù)隨著跨導的增加而減小。

1. 3. 3 線性度

如果節(jié)點A (見圖1)的電壓過高,開關(guān)管將會關(guān)斷。也就是說,如果M1 和M3 的電流很大,M1 和M2的輸出端電壓也增大,這樣就會關(guān)斷開關(guān)管M7 和M6或者M5 和M8。開關(guān)管進入線性區(qū),影響混頻器的線性度,所以降低節(jié)點A 的電壓,并讓開關(guān)管遠離線性區(qū) ,即Vgs≈Vth ,能提高混頻器的線性度。

2 電路仿真

該混頻器設計基于SM IC 0. 18 μm標準CMOS工藝,用Advanced Design SySTem軟件進行電路設計與仿真。電源電壓1. 2 V; RF頻率為2. 5 GHz,功率為- 30 dbm; LO頻率為2. 6 GHz,本振信號的電壓擺幅VLO = 600 m Vpp。

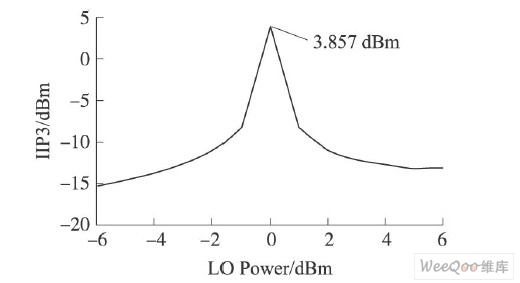

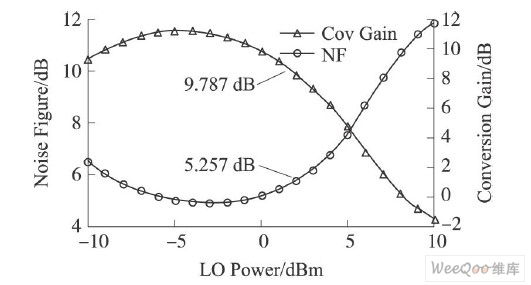

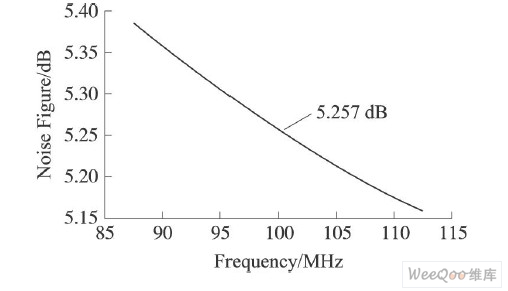

圖3是三階交調(diào)點( IIP3)隨本振功率變化曲線,在本振功率為0 dBm時, IIP3達到最大值3. 857dBm。當本振功率大于或小于0 dBm時, IIP3都會急劇下降。圖4是噪聲系數(shù)(NF)和轉(zhuǎn)換增益(Con2version Gain)隨本振功率變化曲線,本振功率為- 3dBm時,噪聲系數(shù)達最小值4. 982 dB,本振功率為- 5 dBm時,轉(zhuǎn)換增益達到最大值11. 23 dB。考慮到混頻器的整體性能,必須采取折衷,所以選擇本振功率為0 dBm,此時,噪聲系數(shù)為5. 257 dB,轉(zhuǎn)換增益為9. 787 dB。圖5是當本振功率為0 dBm時,噪聲系數(shù)隨輸出頻率變化曲線,噪聲系數(shù)隨著輸出頻率的增加不斷減小,在輸出頻率為100 MHz時,噪聲系數(shù)為5. 257 dB。

圖3 IIP3隨本振功率變化曲線。

圖4 NF與轉(zhuǎn)換增益隨本振功率變化曲線。

圖5 NF隨輸出頻率變化曲線。

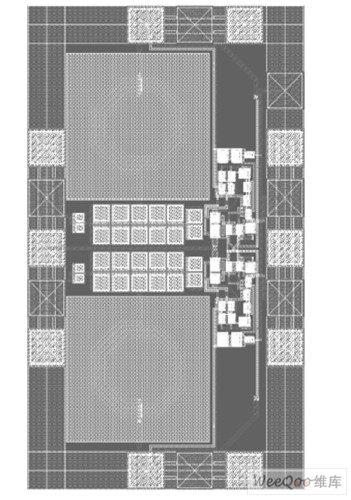

圖6是該折疊混頻器的版圖,該版圖用CadenceVirtuoso Layout editor進行設計及優(yōu)化。RF輸入端的匹配網(wǎng)絡與IF輸出端的buffer都集成在了片內(nèi),版圖面積556μm ×966μm。

圖6 折疊混頻器版圖。

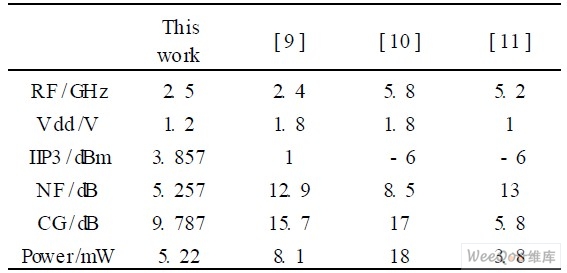

表1是本文設計的折疊混頻器整體性能的仿真結(jié)果,并與其他發(fā)表的論文做了比較,可以看出該混頻器具有高線性度,低噪聲的優(yōu)點。

表1 混頻器性能總結(jié)與比較

3 總結(jié)

本文采用交流耦合互補跨導級成功設計了一種適用于低電源電壓下工作的折疊混頻器。仿真結(jié)果表明,該混頻器具有高線性度、低噪聲的優(yōu)點。