本文針對(duì)實(shí)際需要,,設(shè)計(jì)了以FPGA為核心采集模塊,,以單片機(jī)為顯示控制核心,以TFT彩屏液晶為顯示器件的便攜數(shù)字存儲(chǔ)示波器,。FPGA與高速A/D獲取波形采樣數(shù)據(jù),,通過(guò)單片機(jī)完成彩屏的初始化,合理設(shè)計(jì)出單片機(jī)與FPGA通信的總線握手協(xié)議,,配合異步FIFO作為數(shù)據(jù)緩沖模塊,,實(shí)現(xiàn)了邊采集邊顯示的效果。該系統(tǒng)具有小型化,、操作簡(jiǎn)單,、采樣率高、動(dòng)態(tài)范圍大,、精度高,、實(shí)時(shí)性強(qiáng)和波形顯示效果連續(xù)穩(wěn)定的特點(diǎn),同時(shí)還具有自動(dòng)頻率控制和自動(dòng)增益控制的功能,,具有很廣闊的應(yīng)用空間,。

1 系統(tǒng)組成與工作原理

1.1 系統(tǒng)組成

系統(tǒng)主要由信號(hào)調(diào)理電路,、核心采集模塊,、單片機(jī)處理模塊和液晶外圍電路組成。信號(hào)調(diào)理電路由繼電器,、增益控制D/A,、兩級(jí)可變?cè)鲆娣糯笃鰽D603和保護(hù)電路組成,主要用于對(duì)輸入信號(hào)進(jìn)行程控的衰減與放大,,使信號(hào)在最佳的測(cè)量和顯示量程范圍內(nèi),。核心采集模塊以FPGA和高速A/D為核心,,實(shí)現(xiàn)對(duì)信號(hào)的高速采樣處理以及與單片機(jī)的通信。單片機(jī)處理模塊接收波形數(shù)據(jù)并控制LCD進(jìn)行譯碼顯示,。液晶外圍電路為L(zhǎng)CD提供合適的工作電壓,,并對(duì)液晶模塊與單片機(jī)的接口電路進(jìn)行設(shè)計(jì)。系統(tǒng)組成的總體框圖如圖1所示,。

1.2 系統(tǒng)工作原理

根據(jù)輸入信號(hào)電平的范圍,,F(xiàn)PGA發(fā)出控制信號(hào)控制調(diào)理電路的增益,將信號(hào)電平調(diào)整到最佳采集范圍,。在FPGA內(nèi)配置兩塊異步FIFO作為采集數(shù)據(jù)的緩存區(qū),,實(shí)現(xiàn)高速采集與單片機(jī)讀取速度之間的匹配。高速A/D在系統(tǒng)時(shí)鐘的驅(qū)動(dòng)下采集波形數(shù)據(jù),,并由FPGA測(cè)出信號(hào)的電壓和頻率,。根據(jù)信號(hào)頻率的不同,按照程序的預(yù)設(shè)選擇最佳的時(shí)基,,控制FIFO的寫(xiě)時(shí)鐘信號(hào),,而讀FIFO的時(shí)鐘信號(hào)則固定不變,這樣就可以在屏幕上得到最適合觀察的信號(hào)波形,。該系統(tǒng)的量程設(shè)置和時(shí)基選擇完全由程序控制,,不需要手動(dòng)設(shè)置就可以自動(dòng)將信號(hào)波形調(diào)整到最佳觀察狀態(tài)?! ?/p>

2 系統(tǒng)硬件設(shè)計(jì)

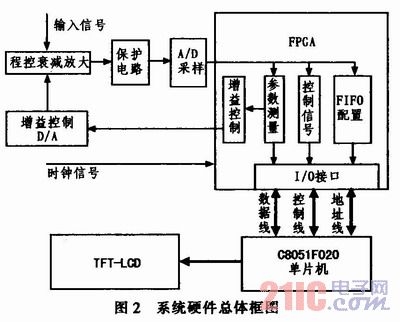

系統(tǒng)硬件主要實(shí)現(xiàn)對(duì)輸入信號(hào)的程控衰減放大,、過(guò)壓保護(hù),信號(hào)的采集處理,,采集數(shù)據(jù)的傳輸以及單片機(jī)與液晶模塊接口電路等,,系統(tǒng)硬件總體框圖如圖2所示。

2.1 信號(hào)調(diào)理電路

信號(hào)調(diào)理電路實(shí)現(xiàn)了對(duì)輸入信號(hào)的程控衰減放大,,它由增益變化范圍線性連續(xù)可調(diào)的可控增益放大器AD603組成,。通過(guò)FPGA,結(jié)合8位D/A轉(zhuǎn)換芯片CA3338E,,對(duì)兩片AD603引腳端的輸入電壓進(jìn)行控制,,增益和控制電壓關(guān)系為:

![]()

其中,Vc1,,Vc2分別表示兩片AD603的控制電壓,。

在工作時(shí),F(xiàn)PGA輸出控制信號(hào),,使繼電器對(duì)輸入信號(hào)進(jìn)行100倍衰減,。衰減后的信號(hào)經(jīng)A/D轉(zhuǎn)換后采集到FPGA中,根據(jù)預(yù)先設(shè)置的檔位判斷信號(hào)所屬的范圍,。如果信號(hào)幅度過(guò)低,,不在這些范圍之內(nèi),則FPGA重新發(fā)出控制信號(hào),,并減小對(duì)輸入信號(hào)的衰減倍數(shù),,直到衰減后的信號(hào)滿足最佳測(cè)量范圍為止。對(duì)應(yīng)于每個(gè)檔位的信號(hào),,輸出一個(gè)8位的數(shù)字信號(hào)至CA3338E芯片,,并將其輸出的模擬信號(hào)加到AD603的輸入端,得到不同的放大倍數(shù),,完成信號(hào)的程控衰減放大,。信號(hào)調(diào)理電路實(shí)現(xiàn)了自動(dòng)增益控制的功能,有效地提高了輸入信號(hào)的動(dòng)態(tài)范圍,。

2.2 FPGA核心板模塊

FPGA核心板是系統(tǒng)的核心,,一方面負(fù)責(zé)采集并緩存數(shù)據(jù),另一方面實(shí)現(xiàn)與單片機(jī)的通信,。FPGA最小系統(tǒng)板采用的是Xilinx公司SpartanII系列的XC2S200-PQ208型20萬(wàn)門芯片,,其配置芯片為Xilinx公司的專用配置PROM芯片XCF02S,以實(shí)現(xiàn)加電自動(dòng)配置,。核心板采用5 V輸入,,板上有兩塊LM317電源芯片分別輸出3.3 V和2.5 V電壓。板上采用40 MHz有源晶振,,滿足高速設(shè)計(jì)要求,。

2.3 高速A/D模塊

本系統(tǒng)選用ADI公司的12位高速模/數(shù)轉(zhuǎn)換芯片AD9224,完成對(duì)模擬信號(hào)的A/D采樣功能,,該芯片具有極佳的動(dòng)態(tài)無(wú)雜波失真范圍,。AD-9224的電源由+5 V的模擬電源和+3.3 V的數(shù)字電源組成。為減少A/D轉(zhuǎn)換結(jié)果的二次諧波,,提高信噪比(RSN),,A/D芯片前端采用AD8138組成信號(hào)調(diào)理電路將單端信號(hào)轉(zhuǎn)換成差分信號(hào)輸入。該放大器的輸入阻抗高達(dá)6 MΩ,,可以直接與輸入信號(hào)相連從而省略隔離放大器,,因而可大大精簡(jiǎn)了電路結(jié)構(gòu)。AD9224的外圍電路設(shè)計(jì)如圖3所示,。

2.4 單片機(jī)與液晶模塊接口

單片機(jī)使用C8051F020,,它是一種高集成度的混合信號(hào)片上系統(tǒng),有按8位端口組織的64個(gè)數(shù)字I/O引腳,。液晶模塊采用ILI9320片上系統(tǒng)(SoC)驅(qū)動(dòng)器,,支持26萬(wàn)色顯示,分辨率為240 RGBx320像素,圖像數(shù)據(jù)存儲(chǔ)區(qū)的大小為172 800字節(jié),。ILI9320與MCU之間有4種總線接口方法,,分別為i80系統(tǒng)總線、串行總線,、RGB總線和VSYNC總線,。本系統(tǒng)中采用i80總線進(jìn)行控制,通過(guò)讀使能(RDB)和寫(xiě)使能(WRB)2條控制線進(jìn)行讀寫(xiě)操作,,其中數(shù)據(jù)線的寬度為8位,,液晶模塊中的控制信號(hào)和數(shù)據(jù)信號(hào)均為標(biāo)準(zhǔn)的TTL電平,應(yīng)用時(shí)直接與單片機(jī)的GPIO總線相連,。

3 系統(tǒng)軟件設(shè)計(jì)

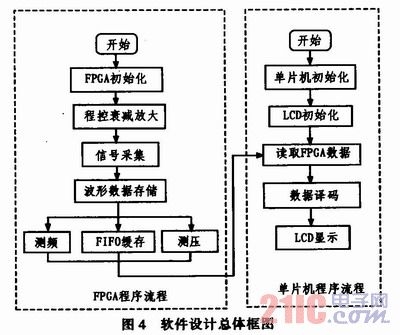

系統(tǒng)軟件設(shè)計(jì)主要完成對(duì)程控衰減放大電路的控制,,時(shí)基的選擇,異步FIFO設(shè)計(jì),,F(xiàn)PGA與單片機(jī)的通信協(xié)議設(shè)計(jì),,波形參數(shù)測(cè)量以及波形顯示中的觸發(fā)設(shè)置等。軟件設(shè)計(jì)總體框圖如圖4所示,。

3.1 異步FIFO設(shè)計(jì)

A/D采樣得到采樣數(shù)據(jù)的數(shù)據(jù)率很高,,為了保證單片機(jī)讀取數(shù)據(jù)的有效性和可靠性,系統(tǒng)中使用異步FIFO對(duì)數(shù)據(jù)進(jìn)行緩存,。FIFO的設(shè)計(jì)是通過(guò)配置FPGA內(nèi)部的BlockRAM資源實(shí)現(xiàn)的,。為了實(shí)現(xiàn)邊采集邊顯示的目的,配置兩塊相同的FIFO,,在讀寫(xiě)時(shí)鐘的控制下,,通過(guò)讀使能和寫(xiě)使能信號(hào)的設(shè)置,使得在同一時(shí)刻始終有一塊FIFO在進(jìn)行寫(xiě)操作,,而另一塊FIFO在將寫(xiě)滿的數(shù)據(jù)讀出,。而對(duì)于同一塊FIFO不允許讀寫(xiě)信號(hào)同時(shí)有效,這樣接收A/D數(shù)據(jù)和讀取數(shù)據(jù)并交給單片機(jī)處理可以同時(shí)進(jìn)行,,從而保證數(shù)據(jù)傳輸?shù)倪B續(xù)性,。

3.2 FPGA與單片機(jī)通信的實(shí)現(xiàn)

FPGA與單片機(jī)之間有效的通信是系統(tǒng)實(shí)現(xiàn)正常功能的重要前提,系統(tǒng)中通過(guò)數(shù)據(jù)總線,,地址總線和控制總線將兩個(gè)模塊聯(lián)系起來(lái),。在FPGA中,將不同類型的數(shù)據(jù)存放到不同的地址中,,這些數(shù)據(jù)包括實(shí)時(shí)采集到的波形數(shù)據(jù),,測(cè)量得到的信號(hào)參數(shù)(電壓和頻率),當(dāng)前的時(shí)基,、垂直分辨率以及一些控制參數(shù),。單片機(jī)通過(guò)地址總線對(duì)FPGA的內(nèi)存進(jìn)行訪問(wèn),并對(duì)讀取的數(shù)據(jù)做出相關(guān)的譯碼處理,并將處理結(jié)果實(shí)時(shí)顯示在液晶屏幕上,。

控制總線包括讀使能和寫(xiě)使能信號(hào),,分別控制異步FIFO的讀寫(xiě)操作。當(dāng)其中一塊FIFO中存夠指定數(shù)量的采樣數(shù)據(jù)以后,,讀使能信號(hào)有效,,單片機(jī)開(kāi)始接收數(shù)據(jù),,此時(shí)另一塊FIFO開(kāi)始寫(xiě)入采集數(shù)據(jù),。當(dāng)數(shù)據(jù)接收完畢后,單片機(jī)向FPGA發(fā)出寫(xiě)使能信號(hào),,此時(shí)兩塊FIFO交換功能,,單片機(jī)控制LCD將波形實(shí)時(shí)顯示出來(lái),并以此循環(huán)交替工作,。這種異步總線握手協(xié)議的設(shè)計(jì),,使得單片機(jī)的讀和FIFO的讀寫(xiě)協(xié)調(diào)工作,大大提高了數(shù)據(jù)傳輸?shù)目煽啃浴?/p>

3.3 波形參數(shù)的測(cè)量和觸發(fā)囂的軟件實(shí)現(xiàn)

對(duì)信號(hào)參數(shù)的測(cè)量是示波器的重要功能,,本系統(tǒng)可以測(cè)量輸入信號(hào)的頻率和電壓,。在FPGA內(nèi)利用等精度測(cè)頻技術(shù)和比較法分別進(jìn)行測(cè)頻和測(cè)壓,由單片機(jī)通過(guò)地址線讀取數(shù)據(jù)并完成數(shù)據(jù)的譯碼和顯示,。

觸發(fā)器是示波器的重要組成部分,,通過(guò)觸發(fā)器產(chǎn)生的控制信號(hào),控制示波器對(duì)波形數(shù)據(jù)的存儲(chǔ)和顯示,,達(dá)到穩(wěn)定同步的目的,。本系統(tǒng)設(shè)計(jì)的觸發(fā)器,采用全數(shù)字化結(jié)構(gòu),,大大降低了系統(tǒng)硬件電路的復(fù)雜性,,并且觸發(fā)條件的調(diào)整比較方便。觸發(fā)器通過(guò)引用單片機(jī)內(nèi)部的RAM資源定制了一個(gè)采集數(shù)據(jù)的緩存區(qū),,將波形數(shù)讀入該緩存區(qū),,按照預(yù)先設(shè)定的觸發(fā)門限,將緩存區(qū)中的數(shù)據(jù)讀出,,如果滿足觸發(fā)條件,,則將數(shù)據(jù)在屏幕上顯示出來(lái)?! ?/p>

4 系統(tǒng)調(diào)試和測(cè)試

在完成了系統(tǒng)的硬件設(shè)計(jì)和軟件設(shè)計(jì)以后,,需要進(jìn)行綜合調(diào)試和測(cè)試。通過(guò)調(diào)試,,不斷優(yōu)化程序代碼,,使系統(tǒng)的性能得以提高,工作狀態(tài)更加穩(wěn)定。在進(jìn)行測(cè)試時(shí),,輸入峰峰值為2 V,,頻率為1 kHz的正弦信號(hào),在LCD上觀察到的波形及測(cè)量參數(shù)如圖5所示,。從圖中可以看出,,波形顯示穩(wěn)定連續(xù),測(cè)量信號(hào)參數(shù)的精度高,,且包含彩色信息豐富,。

5 結(jié)束語(yǔ)

研究了以TFT彩屏液晶作為顯示器件的手持?jǐn)?shù)字存儲(chǔ)示波器的總體方案,即信號(hào)調(diào)理電路,,核心采集模塊,,單片機(jī)處理模塊和液晶外圍電路組成。在確定總體方案的同時(shí),,給出了實(shí)現(xiàn)此總體方案的具體方法,。

通過(guò)握手協(xié)議合理解決單片機(jī)與FPGA通信的問(wèn)題,用軟件設(shè)計(jì)了數(shù)字觸發(fā)器,,取代了一般示波器中常用的觸發(fā)電路,,降低了系統(tǒng)的硬件復(fù)雜度。該數(shù)字存儲(chǔ)示波器允許輸入信號(hào)的動(dòng)態(tài)范圍大,,體積小,,便于攜帶,操作簡(jiǎn)單,,具有很高的應(yīng)用價(jià)值和廣闊的發(fā)展空間,。