諸如機器視覺、監(jiān)控專用顯示器和醫(yī)用顯示器之類的工業(yè)視頻系統(tǒng),在將高分辨率視頻數(shù)據(jù)從源傳輸至處理器或顯示器時面臨許多難題。現(xiàn)有的解決方案(Camera-Link、GigE Vision 及其它 LVDS 接口)雖然可以滿足目前工業(yè)市場的需求,但對于透過較長電纜線提供可靠的高速傳輸速度數(shù)據(jù)方面卻遇到了障礙。增加的 EMI 通常伴隨著較高的開關數(shù)據(jù)速率。而將系統(tǒng)成本與設計復雜性降至最低,是永恒不變的要求。

常見工業(yè)視頻應用面臨的難題

我們首先來檢視一下幾種常見的應用。機器視覺系統(tǒng)需要將捕獲的圖像數(shù)據(jù)從數(shù)碼相機傳輸至遠程幀捕獲器。數(shù)據(jù)傳輸速率受圖像捕獲的分辨率、位深度及幀速率影響。設計較高的分辨率與位深度的圖像,是為了提供進行復雜分析所需的細節(jié)數(shù)據(jù)。這對于因幾何圖形縮小而需要進行更精密檢測的電子檢查設備等應用至關重要。要提高整體的檢查傳送率,則需要更快的幀速率。

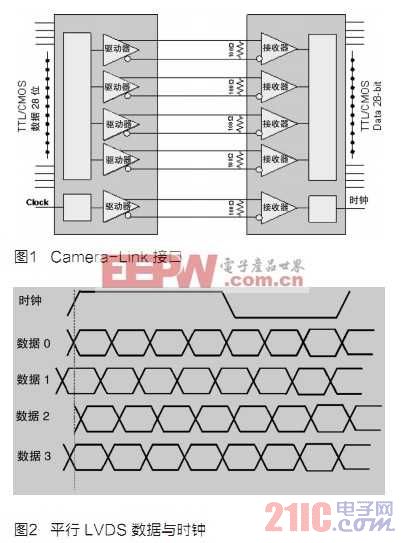

如今的機器視覺系統(tǒng)通常采用由 Camera Link 標準制定的通信接口。這個重要標準發(fā)表于 2000 年 10 月,多年來一直成功地為視覺行業(yè)提供支持。此接口由串行化數(shù)據(jù)(7:1 比率)的平行差動分對以及平行差動頻率組成。圖 1 所示為常見 Camera-Link 接口。

采用低電壓差分信號傳輸 (LVDS) 的 7:1 串行方案,可為許多應用提供高效、強大的通信能力。但若將該技術擴展至較高吞吐量與較長距離,則存在一些限制和難題。當時鐘速率提高和距離增長時,差分時鐘與數(shù)據(jù)對的平行性質就容易受影響從而使配對之間的過長電纜發(fā)生偏斜。由于在相機鏈路的接收器端是使用獨立時鐘通道對數(shù)據(jù)進行采樣的,因此保持正確的設置以及兩者之間的關系非常重要。隨著互連長度增加,對間偏斜也會增加,甚至可能會超過限制。為了將偏斜減至最小,可能需要高級且更貴的電纜與連接器。

在工業(yè)顯示器系統(tǒng)中,影像來源(成像器或圖形控制器)與數(shù)字顯示器之間的鏈路也面臨著類似的難題。如同視覺系統(tǒng)一樣,工業(yè)顯示器系統(tǒng)使用驅動器來提高數(shù)據(jù)速率,并且支持高達真彩色(每個像素 24 位)的較高色彩深度。更為明顯的發(fā)展趨勢是高清 (HD) 甚至更高分辨率的應用,這些影像可為監(jiān)控及醫(yī)療應用提供有用的細節(jié)。平行 LVDS 解決方案(類似于 Camera Link 使用的解決方案)具有同樣的電纜偏斜限制。隨著數(shù)據(jù)速率提高,偏斜要求的限制會進一步減小,最大電纜長度也因此縮短。

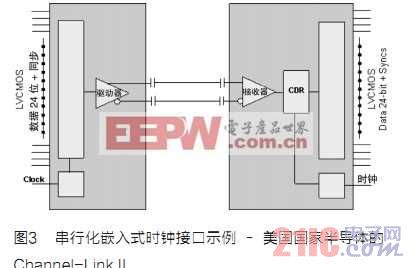

使用嵌入式時鐘接口可以消除配對之間的這種偏斜限制。所有數(shù)據(jù)與時鐘經(jīng)過編碼和串行化后,將通過單一差分對進行傳輸。解串器接收串行流,然后使用時鐘與數(shù)據(jù)恢復 (CDR) 電路提取時鐘與數(shù)據(jù)信號。

除了解決偏斜問題外,串行化解決方案還具有多個其它方面的優(yōu)點。僅驅動一個差分對可減小互連媒體的整體大小。這意味著可以使用較小的電纜與連接器,將 PCB 上的連接器覆蓋面積減至最小,并使接口變得更狹小且更具彈性。減少電纜組件中的配對數(shù)量,以及消除對嚴格偏斜容錯的限制,將允許使用較低成本的電纜。

轉移至串行化接口對系統(tǒng)設計具有非常積極的影響。但是,在使用嵌入式頻率方案進行設計時,必須考慮一些因素。首先要考慮的是差動對上的數(shù)據(jù)速率現(xiàn)在比較高。過去通過四個配對來傳輸?shù)臄?shù)據(jù),現(xiàn)在僅通過一個配對進行發(fā)送,因此數(shù)據(jù)速率大約提高了 4 倍。

簡化設計的技術

我們現(xiàn)在來探討一下與較高接口速度相關的一些考慮因素,以及可用于簡化設計和提供強大且具有成本效率的解決方案的各種功能與技術。

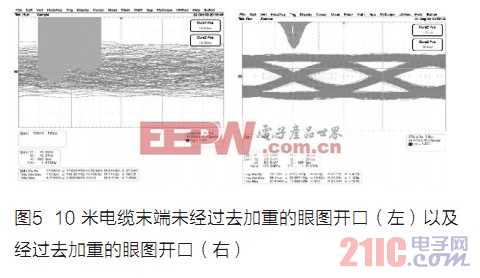

在這種較高的數(shù)據(jù)速率下,信號完整性顯得尤為重要。我們將不再關注時鐘與數(shù)據(jù)的一致性,而是關注串行化數(shù)據(jù)流內每個位的眼圖開口。在數(shù)據(jù)穿越電纜時,信號會因衰減、抖動及符號間干擾 (ISI) 效應而降級。要正確接收信號,重要的是電纜末端(解串器輸入端)的數(shù)據(jù)眼必須是“打開”狀態(tài)。

電纜等化與去加重是專用于防止信號降級的兩大功能。等化的作用是“重新開啟”電纜最末端差動信號的數(shù)據(jù)眼。均衡器采用高通濾波器,以及與電纜衰減曲線成反比的增益曲線。可對均衡器增益進行編程的能力,允許通過不同電纜與長度來進行效能優(yōu)化的微調。此電路可以是分離式電路,或是內置于解串器輸入端。

第二項技術是信號波形還原,可防止符號間干擾 (ISI) 效應。依據(jù)正在傳輸?shù)臄?shù)據(jù)模式,電荷可能會累積在電纜上。這會妨礙快速切換至相反狀態(tài)的能力。ISI 會導致信號振幅降低,這種情況在發(fā)送單一位(如由零組成的一個長字符串正中間的“一個”位)時尤為明顯。此單一位轉換的能量不足以抵消電纜上存儲的電荷,因此在解串行器輸入端的數(shù)據(jù)眼會呈現(xiàn)關閉狀態(tài)。

去加重可以在初始轉換完成后,在線路上進行驅動的輸出電壓。這樣就能將電纜上累積的電荷以及相關的直流偏移減至最少,使信號可以輕松轉換為新狀態(tài)。去加重的等級應該允許進行調整,以便針對互連特征優(yōu)化效應。

EMI – 普遍問題

無論是使用傳統(tǒng)接口還是使用串行化接口,所有系統(tǒng)都面臨著一個共同的難題,那就是降低 EMI。隨著分辨率與色彩深度提高,邊緣速率與通道開關次數(shù)也會提高,從而導致電磁輻射增加。此問題可以從多方面解決,首先是從 LVDS 及其廣泛用途著手。LVDS 使用通用平行視頻接口(4 個數(shù)據(jù)對 + 1 個時鐘對),并且還可用于串聯(lián)化嵌入式頻率解決方案。

但是,源與接收設備(幀捕獲器或顯示器)之間的連接可能使用 LVCMOS 接口。寬式平行 LVCMOS 輸出總線是公認的輻射“熱點”。請務必嘗試將與這些輸出開關相關的能量降至最低,并盡可能擴展此能量的頻譜。由于平行輸出切換更快,因此需要提高邊緣速率。輸出轉換應該盡可能慢至能夠有效支持要求的開關頻率與輸出負載。具有可程序化輸出驅動的解串器可提供此彈性。

擴展能量的頻譜是降低峰值輻射的常見做法。在某些情況下,源可能會提供擴頻頻率。所選串行器與解串器應該能夠跟蹤此頻率調制以獲得最大好處。在源進行擴展并非永遠都能得到支持,因此還需要使用可自行生成擴頻輸出的解串聯(lián)器,以便降低輸出“熱點”上的電磁輻射。

即使是使用具有降低 EMI 功能的芯片集,也務必要遵循合理的 印刷電路版設計慣例。

串行化視頻的解決方案

美國國家半導體 Channel-Link II 系列的串行器/解串器芯片集,是專為簡化串聯(lián)化視頻接口的應用而設計。75MHz 的最高時鐘頻率可支持 HD 720p 視頻。高達 24 位的數(shù)據(jù)、附帶的視頻同步信號以及視頻像素頻率,經(jīng)過串行化后將成為單一低電壓差動輸出。

這些芯片集均提供用于調整信號的可調式去加重與等化功能。

獲得專利的直流平衡編碼方案以及數(shù)據(jù)隨機化和加密功能,可將 ISI 減至最少并降低鏈路上的輻射,從而擴展了頻譜內容,否則這些未經(jīng)擴展的頻譜內容便會重復出現(xiàn)。串行器與解串器的設計,是要充分利用上游設備的擴頻時鐘,同時還提供自行生成的擴頻時鐘。降低 EMI 的其它功能包括降低驅動強度,以及交錯開關平行輸出驅動器。所有零件均提供“自動休眠”省電功能,當輸入接口處于非活動狀態(tài)時,便會切換至低功率模式。

平行總線可以與 LVCMOS 或 LVDS(4 個數(shù)據(jù) + 1 個頻率)連接。此 LVDS 接口相當于美國國家半導體的 28 位 Channel-Link 產品,并且提供簡單易用的升級路徑,其中的圖像源、幀捕獲器或顯示控制器均包含集成 LVDS。

對于需要更高頻寬與更長電纜驅動的系統(tǒng),美國國家半導體的 FPGA-Link 解決方案則是理想選擇。在接收設備和源上與具有成本效率的 FPGA 結合使用時,可通過 30 米長的電纜獲得高達 3.125Gbps 的數(shù)據(jù)速率。解串器可提供重新定時的串行輸出以驅動菊花鏈式接收設備,這在并排顯示器應用中特別有用。

嵌入式視頻系統(tǒng)可以獲得使用串行化接口時所具有的性能與成本優(yōu)勢。可靠的設計慣例與技術,對于成功的實施非常重要。美國國家半導體的 Channel-Link II 與 FPGA-Link 芯片集,提供具有信號調整功能的串聯(lián)化接口,可將偏斜問題降至最低,并允許使用更長且更細小的電纜。降低 EMI 的功能以及與各種來源和接收設備之間的兼容性,打造了簡單易用且功能強大的解決方案。