dMAX" title="dMAX">dMAX(Dual Data Movement Accelerator,雙向數(shù)據(jù)傳輸" title="數(shù)據(jù)傳輸">數(shù)據(jù)傳輸加速器)是TI公司的DSP芯片C6727B特有的一種片內(nèi)設(shè)備。應(yīng)用dMAX和EMIF" title="EMIF">EMIF(External Memory InteRFace,外部存儲(chǔ)器接口" title="接口">接口)可以實(shí)現(xiàn)片內(nèi)RAM、片內(nèi)和片外設(shè)備以及兩個(gè)片外設(shè)備之間的數(shù)據(jù)傳輸。dMAX模塊的內(nèi)部結(jié)構(gòu)如圖1所示。

圖1 dMAX內(nèi)部結(jié)構(gòu)圖

從圖中可以看出,dMAX主要由事件和中斷處理模塊、事件編碼器、傳輸事件模塊等組成。事件模塊分成高優(yōu)先級(jí)和低優(yōu)先級(jí)兩個(gè)相互獨(dú)立的模塊,各自有獨(dú)立的事件入口和事件參數(shù)表,和CPU有獨(dú)立的接口。使得dMAX可以同時(shí)處理兩個(gè)不同的事件。當(dāng)訪問(wèn)CPU端口時(shí),MAX0的優(yōu)先級(jí)高,MAX1的優(yōu)先級(jí)低。dMAX能夠通過(guò)執(zhí)行先進(jìn)的一維、二維與三維數(shù)據(jù)的存儲(chǔ)器傳輸工作,從而使DSP得以專注于信號(hào)處理任務(wù),顯著提高系統(tǒng)性能。適合圖像的子幀提取或者語(yǔ)音信號(hào)的子信道提取。

DSP內(nèi)部的數(shù)據(jù)交換中心在dMAX的控制下,可以實(shí)現(xiàn)片內(nèi)RAM、EMIF以及HPI接口之間的數(shù)據(jù)交換。本文介紹在dMAX控制下,實(shí)現(xiàn)片內(nèi)RAM和EMIF接口之間的數(shù)據(jù)交換。如果DSP采用普通的異步接口方式,數(shù)據(jù)傳輸需要建立、選通和保持3個(gè)階段,最少需要5個(gè)EMIF時(shí)鐘(建立和保持各1個(gè)時(shí)鐘,選通3個(gè)時(shí)鐘)。為了保證通信的可靠性,一般采用10個(gè)EMIF時(shí)鐘(建立3個(gè)時(shí)鐘,保持2個(gè)時(shí)鐘,選通5個(gè)時(shí)鐘)。而EMIF時(shí)鐘最快為133MHz;這樣,采用異步接口的通信速率一般為13.3M×32b/s(采用32位數(shù)據(jù)總線寬度)。此外,異步接口數(shù)據(jù)傳輸必須在CPU的參與下,使用指令實(shí)現(xiàn)數(shù)據(jù)搬移。將占用大量的CPU開(kāi)銷,在很多高速的數(shù)據(jù)采集和處理中,將降低系統(tǒng)的整體性能。為此,采用dMAX實(shí)現(xiàn)嵌入式FIFO數(shù)據(jù)傳輸克服異步傳輸?shù)娜秉c(diǎn),其傳輸采用突發(fā)讀寫(xiě)方式進(jìn)行,可以連續(xù)突發(fā)讀寫(xiě)8個(gè)數(shù)據(jù),一共只需要20個(gè)時(shí)鐘,通信速率提高為53.2M×32b/s,提高4倍讀寫(xiě)速率。還可以采用和DMA后臺(tái)運(yùn)行,這樣將大大降低整個(gè)系統(tǒng)數(shù)據(jù)讀寫(xiě)的開(kāi)銷,從而可以實(shí)現(xiàn)更加復(fù)雜和可靠的算法處理。

嵌入式FIFO設(shè)計(jì)

嵌入式FIFO的設(shè)計(jì)主要就是控制FIFO的7個(gè)參數(shù)。這7個(gè)參數(shù)分別為基地址、空間大小、空標(biāo)志、滿標(biāo)志、錯(cuò)誤標(biāo)志、讀指針和寫(xiě)指針。它們之間的關(guān)系如圖2所示。

圖2 FIFO結(jié)構(gòu)示意圖

基地址和空間大小用于規(guī)劃出一段內(nèi)存空間,該內(nèi)存空間用于FIFO設(shè)備,并被FIFO設(shè)備保護(hù)起來(lái),使得其他設(shè)備和程序不能訪問(wèn)該空間。為了便于操作方便,空間大小一般為2的整數(shù)次冪,但不做要求。具體到C6727B型號(hào)的DSP,空間大小最大為1M個(gè)元素,元素大小可以是8位、16位或者32位數(shù)據(jù),不能為其他類型的數(shù)據(jù)。基地址可以為內(nèi)存空間的任何一個(gè)地址,同樣為了操作方便,一般為空間大小的邊界點(diǎn)。例如,8個(gè)元素的FIFO,其基地址一般為XXXXX000b,也就是地址的低3位為0,基地址就肯定為8的整數(shù)次。同樣,64個(gè)元素的FIFO,其低6位為0。基地址和空間大小的特殊要求避免訪問(wèn)時(shí)的地址跨越多頁(yè)問(wèn)題,可以提高FIFO的訪問(wèn)速度。

空標(biāo)志和滿標(biāo)志用于表示FIFO的存儲(chǔ)狀態(tài)。讀指針和寫(xiě)指針用于表示讀寫(xiě)的當(dāng)前地址。錯(cuò)誤標(biāo)志表示對(duì)FIFO的錯(cuò)誤操作。當(dāng)FIFO處于滿標(biāo)志情況下仍然寫(xiě)FIFO,或者FIFO處于空標(biāo)志情況下仍然讀FIFO,F(xiàn)IFO都將終止當(dāng)前操作,并將錯(cuò)誤標(biāo)志置位。

FIFO的寫(xiě)操作只有一種工作方式,即每次寫(xiě)一個(gè)新的數(shù)據(jù),寫(xiě)指針加1,直到寫(xiě)滿。而FIFO讀操作有兩種工作方式,分別為標(biāo)準(zhǔn)操作和多階延遲(Multi-tap Delay Transfer)操作。標(biāo)準(zhǔn)操作和寫(xiě)操作一樣。多階延遲操作一般用于濾波處理,當(dāng)需要對(duì)輸入信號(hào)進(jìn)行濾波處理時(shí)候,每次希望從FIFO讀取一段窗口的數(shù)據(jù),進(jìn)行濾波處理,數(shù)據(jù)窗口仍然只移動(dòng)一個(gè)數(shù)據(jù)。在標(biāo)準(zhǔn)操作情況下,如果讀取一段窗口的數(shù)據(jù),F(xiàn)IFO則將該段窗口的數(shù)據(jù)全部彈出。多階延遲操作則只彈出一個(gè)數(shù)據(jù)。該操作方法對(duì)語(yǔ)音或者AD采樣數(shù)據(jù)的平滑、FIR等濾波非常適用。需要注意的是,多階延遲操作的數(shù)據(jù)窗大小需要設(shè)置,如果FIFO存儲(chǔ)的數(shù)據(jù)個(gè)數(shù)小于數(shù)據(jù)窗,F(xiàn)IFO則終止當(dāng)前操作,并給出錯(cuò)誤標(biāo)志。系統(tǒng)硬件結(jié)構(gòu)

C6727B和其他DSP有一個(gè)較大的區(qū)別,就是C6727B不再提供專門的外部中斷引腳,而是采用GPIO引腳和dMAX配合使用,通過(guò)寄存器的設(shè)置將GPIO引腳配置成外部中斷引腳。本文為了實(shí)現(xiàn)FIFO的實(shí)時(shí)操作,一旦外設(shè)向FIFO寫(xiě)入數(shù)據(jù),即發(fā)出中斷信號(hào)到DSP的CPU,通知CPU讀取數(shù)據(jù)。為此,需要使用1個(gè)外部中斷引腳,將C6727B的音頻串口的AXR[8]配置成通用的GPIO引腳,并在dMAX中設(shè)置成中斷引腳。此時(shí)需要將音頻串口的CONFIGMACSP0寄存器設(shè)置為0x0001,如圖3所示。此時(shí)音頻串口不能再作為普通的音頻口使用,而是配置成IO接口。

圖3 中斷功能設(shè)置框圖

從圖3中可以看出,配置好音頻串口后,一旦AXR[8]引腳有上升沿到,則McASP0激活dMAX的事件26,向CPU發(fā)送內(nèi)部中斷13。McASP的與中斷相關(guān)的寄存器配置是實(shí)現(xiàn)以上方案的重點(diǎn)。使用PFUNC寄存器將其配置成通用IO引腳;PDIR寄存器控制IO引腳的方向;如果是輸出引腳則由POUT引腳輸出高低電平,如果是輸入引腳,則由PDIN寄存器讀出該引腳的狀態(tài);此外,可以使用PDCLR和PSET寄存器清除或者設(shè)置輸出引腳的狀態(tài)。

系統(tǒng)軟件設(shè)計(jì)

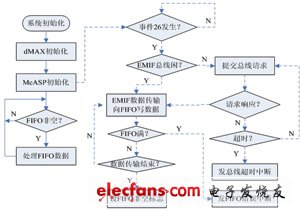

系統(tǒng)軟件設(shè)計(jì)主要包括McASP的初始化、dMAX的初始化、FIFO的初始化、中斷使能等。系統(tǒng)主程序只需要等待中斷進(jìn)行相應(yīng)的處理,主要的數(shù)據(jù)傳輸工作都是dMAX按照軟件配置自動(dòng)完成,不需要CPU參與。圖4是實(shí)現(xiàn)由外設(shè)寫(xiě)FIFO,DSP讀取FIFO數(shù)據(jù)的流程。圖中虛線部分表示由dMAX獨(dú)立完成的工作,實(shí)線部分表示由CPU完成的工作。兩者之間通過(guò)內(nèi)部中斷方式實(shí)現(xiàn)狀態(tài)的交流。

圖4 系統(tǒng)軟件流程

為了提高FIFO的讀寫(xiě)速率,一般采用突發(fā)方式進(jìn)行讀寫(xiě)。突發(fā)方式的讀時(shí)序如圖5所示。寫(xiě)時(shí)序和讀時(shí)序類似。突發(fā)方式一次最多只能讀寫(xiě)8個(gè)數(shù)據(jù),也可以一次突發(fā)讀寫(xiě)4個(gè)或者2個(gè)數(shù)據(jù)。突發(fā)讀寫(xiě)時(shí)數(shù)據(jù)的建立和保持時(shí)間最少可以設(shè)置成1個(gè)時(shí)鐘周期,如圖中所示。但為了通信可靠,一般采用2個(gè)時(shí)鐘周期。突發(fā)方式最大的節(jié)省時(shí)間是連續(xù)的其他數(shù)據(jù)將不再需要建立和保持周期,而是直接進(jìn)行讀寫(xiě),一般只需要兩個(gè)時(shí)鐘周期就可以完成一個(gè)數(shù)據(jù)的讀寫(xiě)。最快情況下,突發(fā)讀寫(xiě)8個(gè)數(shù)據(jù)只需要20個(gè)時(shí)鐘周期,讀寫(xiě)速率達(dá)到53.2M×32b/s,滿足大部分設(shè)備的要求。

圖5 突發(fā)讀時(shí)序圖

總結(jié)

dMAX的特有結(jié)構(gòu)使得其可以實(shí)現(xiàn)嵌入式FIFO。本文介紹了基于C6727B的dMAX的基本結(jié)構(gòu)以及基于dMAX的嵌入式FIFO軟硬件設(shè)計(jì),設(shè)置通用GPIO引腳作為中斷,為了加快FIFO的傳輸速率,使用突發(fā)讀寫(xiě)方式進(jìn)行數(shù)據(jù)傳輸。嵌入式FIFO的實(shí)現(xiàn),使得DSP和外部設(shè)備的通信更加方便和快捷,而且不需要CPU的參與,減輕了CPU的負(fù)擔(dān),CPU可以專注于復(fù)雜的算法處理。