智能卡(SMART card)通常指一張給定大小的塑料卡片,上面封裝了集成電路芯片,用于存儲(chǔ)和處理數(shù)據(jù)。隨著嵌入式設(shè)備的普及,智能卡在金融、電信、單位考勤、公共事業(yè)、交通、醫(yī)療等領(lǐng)域得到廣泛應(yīng)用。本文通過對(duì)ISO/IEC 7816-3傳輸協(xié)議的分析,基于AMBA總線架構(gòu),提出一款智能卡設(shè)計(jì)方案,通過FPGA驗(yàn)證并采用SMIC 0.18μm工藝流片成功。

2 智能卡控制器工作原理

2.1 復(fù)位應(yīng)答

當(dāng)控制器檢測(cè)到智能卡插入操作時(shí)對(duì)智能卡上電,并按照規(guī)范向智能卡發(fā)出冷復(fù)位信號(hào),智能卡接收到該信號(hào)后向控制器發(fā)送復(fù)位響應(yīng),提供編碼方式、協(xié)議選擇、時(shí)鐘轉(zhuǎn)換因子、波特率調(diào)整因子、額外保護(hù)時(shí)間和最大工作等待時(shí)間等參數(shù),后續(xù)的會(huì)話將按照這些參數(shù)進(jìn)行。如果冷復(fù)位之后控制器沒有收到符合格式的復(fù)位響應(yīng),控制器就發(fā)出熱復(fù)位;如果智能卡對(duì)熱復(fù)位仍然沒有給出符合格式的復(fù)位響應(yīng),控制器將結(jié)束會(huì)話,并釋放智能卡。

2.2 傳輸協(xié)議

智能卡控制器有字符傳輸方式(character transmission)和塊傳輸方式(block transmission)兩種傳輸協(xié)議。在字符傳輸方式中數(shù)據(jù)以字節(jié)單位發(fā)送,支持?jǐn)?shù)據(jù)奇偶校驗(yàn)。塊傳輸方式以多個(gè)字節(jié)組成的塊為發(fā)送單位,發(fā)送連續(xù)的數(shù)據(jù),不支持塊中單個(gè)字節(jié)數(shù)據(jù)的校驗(yàn),采用CRC/LRC軟件校驗(yàn)。

2.3 基本時(shí)間單元ETU

智能卡會(huì)話過程中,每個(gè)數(shù)據(jù)位占用時(shí)間為1個(gè)ETU(Elementary Time Unit),ETU與智能卡的時(shí)鐘頻率呈線性關(guān)系:ETU=F/(D×f)。其中,f為控制器工作頻率;F是時(shí)鐘轉(zhuǎn)換因子;D是波特率調(diào)整因子,支持2的次方數(shù)和負(fù)次方數(shù)。F和D的值,可以在智能卡的復(fù)位響應(yīng)后根據(jù)響應(yīng)提供的參數(shù)重新設(shè)定,如果智能卡沒有提供相應(yīng)的參數(shù),將使用缺省值(F=372,D=1)。

2.4 數(shù)據(jù)幀

在字符傳輸方式時(shí),數(shù)據(jù)幀由10個(gè)數(shù)據(jù)位組成(如圖1所示),第一個(gè)是起始位(Start),后面跟8 b數(shù)據(jù)位,最后一個(gè)是奇偶校驗(yàn)位。在沒有會(huì)話的時(shí)候,I/O信號(hào)線保持高電平。當(dāng)出現(xiàn)奇偶校驗(yàn)錯(cuò)誤時(shí),控制器會(huì)重發(fā)數(shù)據(jù),最多重發(fā)4次,如果連續(xù)5次都發(fā)送不成功,控制器發(fā)出中斷,請(qǐng)求系統(tǒng)釋放智能卡。

在塊傳輸方式時(shí),數(shù)據(jù)幀由1位起始位和8位數(shù)據(jù)位構(gòu)成,沒有校驗(yàn)位。塊幀由起始域,信息域和終止域構(gòu)成。起始域3個(gè)字節(jié)分別為節(jié)點(diǎn)地址、協(xié)議控制和長(zhǎng)度;信息域?yàn)榇l(fā)送的數(shù)據(jù),終止域?yàn)镃RC/LRC校驗(yàn)字節(jié)。

3 模塊劃分及硬件實(shí)現(xiàn)

智能卡控制器包括復(fù)位控制模塊,收發(fā)控制模塊,總線接口模塊,讀緩沖器模塊,寫緩沖器模塊,通過APB接口和AMBA總線相連,對(duì)外是CLK,RST,和1根雙向的I/O數(shù)據(jù)線(如圖2所示)。

實(shí)現(xiàn)各模塊功能需設(shè)置如下寄存器(如表1所示)。

3.1 復(fù)位控制模塊

復(fù)位控制模塊通過狀態(tài)機(jī)的跳變完成對(duì)智能卡的復(fù)位(如圖3所示)。當(dāng)智能卡上電后,系統(tǒng)初始處于IDLE狀態(tài),控制器在使能后按照規(guī)范向智能卡發(fā)出冷復(fù)位信號(hào)。首先RST復(fù)位信號(hào)置低400個(gè)CLK以上對(duì)卡復(fù)位,然后進(jìn)入等待復(fù)位響應(yīng)狀態(tài)。控制器經(jīng)過1 860個(gè)CLK后還沒有收到復(fù)位響應(yīng)則可以選擇進(jìn)入時(shí)鐘停止?fàn)顟B(tài)。當(dāng)時(shí)鐘恢復(fù)后,等待700個(gè)CLK后重新開始檢測(cè)復(fù)位響應(yīng)。當(dāng)I/O數(shù)據(jù)線上檢測(cè)到負(fù)跳變,則進(jìn)入起始位接收狀態(tài),一個(gè)ETU后順次進(jìn)入數(shù)據(jù)接收,校驗(yàn)位接收狀態(tài)。最后判斷校驗(yàn)位正確與否,如果校驗(yàn)正確就保持I/O線為高等待下一個(gè)數(shù)據(jù)的接收;如果出錯(cuò),則拉低I/O線1個(gè)ETU通知智能卡數(shù)據(jù)出錯(cuò),請(qǐng)求重傳,并設(shè)置錯(cuò)誤次數(shù)計(jì)數(shù)器。

如果冷復(fù)位之后控制器沒有收到符合格式的復(fù)位響應(yīng),控制器就發(fā)出熱復(fù)位,熱復(fù)位過程同上。如果熱復(fù)位后40 000個(gè)時(shí)鐘周期內(nèi),控制器仍未檢測(cè)到復(fù)位響應(yīng),則控制器將結(jié)束會(huì)話,并釋放智能卡。

3.2 數(shù)據(jù)收發(fā)控制模塊

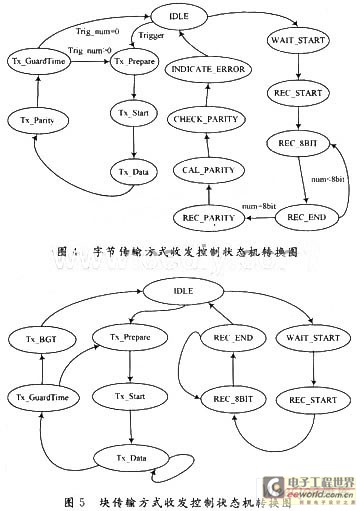

數(shù)據(jù)收發(fā)模塊按照系統(tǒng)對(duì)控制寄存器,各時(shí)間寄存器和輸出字節(jié)控制寄存器的設(shè)置來工作。與復(fù)位模塊一樣,數(shù)據(jù)收發(fā)模塊也是由狀態(tài)機(jī)跳變來完成。系統(tǒng)在復(fù)位響應(yīng)完成后進(jìn)人IDLE狀態(tài),根據(jù)協(xié)議選擇字節(jié)傳輸方式(如圖4所示)或是塊傳輸方式(如圖5所示)。

在字節(jié)傳輸方式下,當(dāng)系統(tǒng)設(shè)置了輸出字節(jié)控制寄存器后控制器就處于發(fā)送狀態(tài)。首先進(jìn)入Prepare狀態(tài),將發(fā)送FIFO中的數(shù)據(jù)放入移位寄存器,并計(jì)算出數(shù)據(jù)的奇偶校驗(yàn)位,為數(shù)據(jù)傳輸做好準(zhǔn)備。1個(gè)ETU之后進(jìn)入Start狀態(tài),拉低I/O數(shù)據(jù)線1個(gè)ETU來發(fā)送數(shù)據(jù)起始位。接著進(jìn)入數(shù)據(jù)發(fā)送狀態(tài),將移位寄存器中的數(shù)據(jù)按1 b/ETU的速率串行發(fā)出。然后發(fā)送1 b奇偶校驗(yàn)位。數(shù)據(jù)發(fā)送完畢后按照系統(tǒng)設(shè)置的保護(hù)時(shí)間將I/O線拉高若干個(gè)ETU。最后檢測(cè)是否已經(jīng)發(fā)出了指定的字節(jié)數(shù)(Trig_num)。如果數(shù)據(jù)發(fā)送完畢,則跳入IDLE狀態(tài)等待新的發(fā)送設(shè)置或轉(zhuǎn)入數(shù)據(jù)接收;否則進(jìn)入Prepare狀態(tài)開始下一個(gè)字節(jié)的發(fā)送。

當(dāng)系統(tǒng)處于數(shù)據(jù)接收狀態(tài)時(shí),首先進(jìn)入等待起始位狀態(tài),在此狀態(tài)設(shè)置超時(shí)計(jì)數(shù)器判斷卡是否有響應(yīng)。當(dāng)I/O線拉低后就進(jìn)入接收起始位狀態(tài),在該狀態(tài)的0.5ETU時(shí)刻判斷I/O數(shù)據(jù)線是否仍然拉低。如果I/O線跳高則說明是由于I/O線抖動(dòng)造成的起始位誤判,狀態(tài)跳回等待起始狀態(tài);如果I/O線仍然為低,則起始位接收成功,并在0.5個(gè)ETU后進(jìn)入數(shù)據(jù)接收狀態(tài)。8 b數(shù)據(jù)按照1 b/ETU的速率接收,完成后轉(zhuǎn)入接收校驗(yàn)位狀態(tài)。硬件根據(jù)接收的8 b數(shù)據(jù)計(jì)算出校驗(yàn)位并與收到校驗(yàn)位比較,如果不同則I/O線拉低告知智能卡數(shù)據(jù)錯(cuò)誤請(qǐng)求重發(fā),相同則進(jìn)入IDLE狀態(tài)等待接收下一個(gè)數(shù)據(jù)或是進(jìn)入發(fā)送狀態(tài)。

塊傳輸(如圖5所示)的接收過程和字符傳輸類似,按照起始位、8 b數(shù)據(jù)位的狀態(tài)機(jī)接收數(shù)據(jù)。一個(gè)字節(jié)接收完畢后返回IDLE,當(dāng)沒有發(fā)送任務(wù)時(shí)就進(jìn)入下一次起始位等待。一個(gè)字節(jié)數(shù)據(jù)發(fā)送完畢后有若干個(gè)ETU的保護(hù)時(shí)間,然后進(jìn)入Prepare狀態(tài)準(zhǔn)備發(fā)送下一個(gè)字節(jié)數(shù)據(jù)。當(dāng)所有數(shù)據(jù)發(fā)送完畢后,系統(tǒng)維持一個(gè)塊保護(hù)時(shí)間BGT(Block Guard Time),然后進(jìn)入IDLE等待新任務(wù)。

3.3 讀寫數(shù)據(jù)緩沖器模塊

由于APB總線上連接多個(gè)功能模塊,如USB,UART等都需要占用總線進(jìn)行數(shù)據(jù)傳輸,智能卡控制器只能通過發(fā)出總線請(qǐng)求在有限時(shí)間占有總線。這使得在進(jìn)行智能卡讀寫操作時(shí)會(huì)申請(qǐng)不到總線從而來不及存儲(chǔ)已收到的數(shù)據(jù)或者來不及獲取新的發(fā)送數(shù)據(jù),增加讀寫數(shù)據(jù)緩沖器實(shí)現(xiàn)數(shù)據(jù)暫存可以很好地解決這個(gè)問題。緩沖器采用寬度為8位,深度為16的同步FIFO。該FIFO通過在最高位額外設(shè)置1 b來判斷空/滿標(biāo)志位。當(dāng)讀寫指針的8 b數(shù)據(jù)位和1 b最高位都相同時(shí),F(xiàn)IFO為空。當(dāng)讀寫指針的8 b數(shù)據(jù)位相同并且1 b最高位相反時(shí),F(xiàn)IFO為滿。根據(jù)FIFO的空滿狀態(tài)來請(qǐng)求或停止新的數(shù)據(jù)。

3.4 APB總線接口模塊

ARM內(nèi)核通過APB總線讀寫智能卡控制器,完成了對(duì)寄存器的設(shè)置、中斷狀態(tài)的讀取以及收發(fā)數(shù)據(jù)的讀寫,讀寫時(shí)序需要符合AMBA APB總線協(xié)議。

系統(tǒng)通過總線接口模塊設(shè)置了控制器工作頻率,傳輸方式、編碼方式、時(shí)鐘轉(zhuǎn)換因子、波特率調(diào)整因子。當(dāng)解析出智能卡為異步半雙工字符傳輸模式時(shí),設(shè)置字符發(fā)送完畢后的保護(hù)時(shí)間和最大等待時(shí)間。當(dāng)解析出智能卡為異步半雙工塊傳輸模式時(shí),設(shè)置塊之問保護(hù)時(shí)間,最大等待之間,以及塊內(nèi)字符間的最大等待時(shí)間。系統(tǒng)按照上述設(shè)置工作。

系統(tǒng)在設(shè)定的參數(shù)下完成對(duì)接收FIFO的讀取和對(duì)發(fā)送FIFO的寫人,并且發(fā)出讀寫使能信號(hào)控制FIFO讀寫。

在收發(fā)控制模塊產(chǎn)生中斷后,對(duì)中斷狀態(tài)寄存器設(shè)置并交由軟件處理。

4 仿真結(jié)果及FPGA驗(yàn)證

智能卡控制器采用RTL級(jí)的Verilog實(shí)現(xiàn),在系統(tǒng)仿真過程中編寫智能卡仿真模型。使用Synopsys公司VCS對(duì)控制器進(jìn)行功能仿真和驗(yàn)證。對(duì)智能卡的數(shù)據(jù)收發(fā)波形如圖6所示。

從仿真結(jié)果可以看出,智能卡控制器符合ISO7816-3協(xié)議,可以對(duì)智能卡進(jìn)行復(fù)位及讀寫操作。

在FPGA驗(yàn)證中,采用Altera公司的StratixⅡ芯片。將智能卡控制器、AMBA總線等模塊的RTL代碼燒錄到ARM開發(fā)板的FPGA中,并且將外接一塊帶有智能卡插槽的擴(kuò)展板與ARM開發(fā)板連接。使用ARM的調(diào)試軟件ARMulator對(duì)控制器進(jìn)行功能測(cè)試。測(cè)試結(jié)果表明該控制器可以成功完成對(duì)智能卡的復(fù)位和數(shù)據(jù)讀寫操作。

5 結(jié) 語

根據(jù)上述VCS仿真和FPGA驗(yàn)證的結(jié)果,說明該智能卡控制器已經(jīng)達(dá)到功能要求,實(shí)現(xiàn)了ISO/IEC7816-3傳輸協(xié)議。利用Design Compiler對(duì)該模塊進(jìn)行綜合并編寫腳本對(duì)芯片的面積和時(shí)序進(jìn)行優(yōu)化,最終邏輯單元為1 368 cells,符合設(shè)計(jì)目標(biāo),實(shí)現(xiàn)了對(duì)智能卡的數(shù)據(jù)復(fù)位及收發(fā)操作。