雖然已經(jīng)有早期的USB3.0產(chǎn)品上市,但向超速(SuperSpeed)USB的大規(guī)模轉(zhuǎn)換還沒有開始。部分問題是USB 2.0已經(jīng)十分普及,生產(chǎn)成本非常低。高帶寬設(shè)備(如視頻攝像機和存儲設(shè)備)成為了SuperSpeed USB的第一批應(yīng)用對象。然而,至少目前為止,成本因素將USB 3.0實現(xiàn)仍限制用于較高端的產(chǎn)品。

除了廣泛部署任何 新的行業(yè)標準所面臨的固有挑戰(zhàn)外,USB 3.0不僅僅是USB 2.0的常規(guī)升級,因為USB 3.0可以提供10倍的性能提升。雖然性能提高了,但消費者對低成本互連的期望一直沒有改變。這就給工程師帶來了巨大的壓力,他們只能使用速度低得多的通道,同時仍要在各種條件下確保可靠性、互操作性和高性能。確保物理層(PHY)一致性的測試和認證從未有現(xiàn)在這么關(guān)鍵或重要。

USB 3.0共享許多其它高速串行技術(shù)(如PCI Express和串行ATA)的特性:8b/10b編碼、顯著的通道衰減以及擴展頻譜時鐘。本文將討論一致性測試方法,以及如何對發(fā)送端、接收端、電纜及互連實施最精確、可重復(fù)的測量。掌握這些技巧后,到SuperSpeed平臺集成實驗室(PIL)的旅程也許會更精彩。

高速Vs.超速

USB 3.0可以滿足帶寬日益增加的需求,能夠支持應(yīng)用提供更加實時的體驗。目前在用的USB設(shè)備數(shù)量估計超過10億,因此USB 3.0需要具有后向兼容功能,以支持傳統(tǒng)的USB 2.0設(shè)備。當(dāng)然,USB 2.0和3.0之間還有多個重要的PHY區(qū)別(表1)。

為了應(yīng)對與更高速度接口有關(guān)的新挑戰(zhàn),SuperSpeed USB一致性測試已經(jīng)作出了很大的修改。USB 2.0接收端的驗證包括接收端靈敏度測試。USB 2.0設(shè)備必須響應(yīng)150mV或150mV以上的測試包,同時忽略(抑制)低于100mV的信號。

另一方面,SuperSpeed USB接收端必須在有許多信號損傷的條件下還能正常工作,因此測試要求比USB 2.0更加嚴格。設(shè)計師還必須考慮傳輸線效應(yīng),并且使用包括在發(fā)送端進行去加重、在接收端進行連續(xù)時間線性均衡(CTLE)在內(nèi)的均衡技術(shù)。如今還要求在接收側(cè)進行抖動容限測試,但使用擴頻時鐘(SSC)和異步參考時鐘可能導(dǎo)致互操作性問題。

評估USB 3.0串行數(shù)據(jù)鏈路的另外一個重要部分是測量波形和互連通道行為之間的復(fù)雜交互。以下假設(shè)已經(jīng)不再成立:因為發(fā)送端輸出信號符合眼圖模板,所以在所有通道達到給定損耗條件下設(shè)計都能正常工作。為了理解在給定最差通道條件下發(fā)送端的余量,除了一致性要求外,你還需要建模通道和電纜的組合,并使用通道建模軟件分析通道效應(yīng)(圖1)。

發(fā)送端的一致性測試

發(fā)送端測試需要使用各種測試圖案(表2)。每種圖案的選擇依據(jù)是與評估圖案的測試有關(guān)的特征。CP0是一個D0.0擾碼序列,用于測量確定性抖動(Dj),比如數(shù)據(jù)關(guān)聯(lián)抖動(DDJ)。而CP1是一種無擾碼的D10.2全速時鐘圖案,不產(chǎn)生DDJ,因此更加適合用于評估隨機抖動(RJ)。

抖動和眼圖高度是在應(yīng)用均衡器函數(shù)和合適的時鐘恢復(fù)設(shè)置(二階鎖相環(huán)或PLL,閉環(huán)帶寬是10MHz,阻尼系數(shù)為0.707)之后用100萬個連續(xù)單位間隔測量的。抖動結(jié)果的計算方法是以1 x 10-12的誤碼率(BER)從測量數(shù)據(jù)總量中提取抖動性能。例如,利用抖動外推法,目標RJ等于測量得到的RJ(rms)乘以14.069。

圖2顯示了標準化的發(fā)送端一致性測試裝置,其中包括參考測試通道和電纜。測試點2(TP2)最靠近被測設(shè)備(DUT),而測試點1(TP1)是遠端測量點。所有發(fā)送端的常規(guī)化測量都是在TP點的信號上進行的。

在TP1點采集到信號后,可以使用一款稱為SigTest的軟件工具進行數(shù)據(jù)處理,類似于正式的PCI Express一致性測試。對于要求預(yù)先一致性測試、表征或調(diào)試的應(yīng)用,還可以用其它工具深入觀察不同條件或參數(shù)下的設(shè)計行為。帶USB 3.0特定軟件的高速示波器可以提供自動的標準化和信息化PHY發(fā)送端測試。這些工具可以確保測試設(shè)備得到了正確配置,從而有效節(jié)省時間。

在測試完成后,一份詳細的通過/失敗測試報告將突出顯示可能存在設(shè)計問題的地方。如果在不同測試位置(例如公司實驗室,測試室)之間出現(xiàn)矛盾,應(yīng)該使用前次測試運行時保存的數(shù)據(jù)再次執(zhí)行測試。

在要求進一步分析的場合,可以用抖動分析和眼圖分析軟件進行查錯和設(shè)計表征。例如,一次可以顯示多個眼圖,允許工程師分析不同的時鐘恢復(fù)技術(shù)或分析軟件通道模型的效果。另外,可以使用不同的濾波器分析SSC效應(yīng),最終解決系統(tǒng)互操作性問題。

雖然已經(jīng)有早期的USB3.0產(chǎn)品上市,但向超速(SuperSpeed)USB的大規(guī)模轉(zhuǎn)換還沒有開始。部分問題是USB 2.0已經(jīng)十分普及,生產(chǎn)成本非常低。高帶寬設(shè)備(如視頻攝像機和存儲設(shè)備)成為了SuperSpeed USB的第一批應(yīng)用對象。然而,至少目前為止,成本因素將USB 3.0實現(xiàn)仍限制用于較高端的產(chǎn)品。

除了廣泛部署任何 新的行業(yè)標準所面臨的固有挑戰(zhàn)外,USB 3.0不僅僅是USB 2.0的常規(guī)升級,因為USB 3.0可以提供10倍的性能提升。雖然性能提高了,但消費者對低成本互連的期望一直沒有改變。這就給工程師帶來了巨大的壓力,他們只能使用速度低得多的通道,同時仍要在各種條件下確保可靠性、互操作性和高性能。確保物理層(PHY)一致性的測試和認證從未有現(xiàn)在這么關(guān)鍵或重要。

USB 3.0共享許多其它高速串行技術(shù)(如PCI Express和串行ATA)的特性:8b/10b編碼、顯著的通道衰減以及擴展頻譜時鐘。本文將討論一致性測試方法,以及如何對發(fā)送端、接收端、電纜及互連實施最精確、可重復(fù)的測量。掌握這些技巧后,到SuperSpeed平臺集成實驗室(PIL)的旅程也許會更精彩。

高速Vs.超速

USB 3.0可以滿足帶寬日益增加的需求,能夠支持應(yīng)用提供更加實時的體驗。目前在用的USB設(shè)備數(shù)量估計超過10億,因此USB 3.0需要具有后向兼容功能,以支持傳統(tǒng)的USB 2.0設(shè)備。當(dāng)然,USB 2.0和3.0之間還有多個重要的PHY區(qū)別(表1)。

為了應(yīng)對與更高速度接口有關(guān)的新挑戰(zhàn),SuperSpeed USB一致性測試已經(jīng)作出了很大的修改。USB 2.0接收端的驗證包括接收端靈敏度測試。USB 2.0設(shè)備必須響應(yīng)150mV或150mV以上的測試包,同時忽略(抑制)低于100mV的信號。

另一方面,SuperSpeed USB接收端必須在有許多信號損傷的條件下還能正常工作,因此測試要求比USB 2.0更加嚴格。設(shè)計師還必須考慮傳輸線效應(yīng),并且使用包括在發(fā)送端進行去加重、在接收端進行連續(xù)時間線性均衡(CTLE)在內(nèi)的均衡技術(shù)。如今還要求在接收側(cè)進行抖動容限測試,但使用擴頻時鐘(SSC)和異步參考時鐘可能導(dǎo)致互操作性問題。

評估USB 3.0串行數(shù)據(jù)鏈路的另外一個重要部分是測量波形和互連通道行為之間的復(fù)雜交互。以下假設(shè)已經(jīng)不再成立:因為發(fā)送端輸出信號符合眼圖模板,所以在所有通道達到給定損耗條件下設(shè)計都能正常工作。為了理解在給定最差通道條件下發(fā)送端的余量,除了一致性要求外,你還需要建模通道和電纜的組合,并使用通道建模軟件分析通道效應(yīng)(圖1)。

發(fā)送端的一致性測試

發(fā)送端測試需要使用各種測試圖案(表2)。每種圖案的選擇依據(jù)是與評估圖案的測試有關(guān)的特征。CP0是一個D0.0擾碼序列,用于測量確定性抖動(Dj),比如數(shù)據(jù)關(guān)聯(lián)抖動(DDJ)。而CP1是一種無擾碼的D10.2全速時鐘圖案,不產(chǎn)生DDJ,因此更加適合用于評估隨機抖動(RJ)。

抖動和眼圖高度是在應(yīng)用均衡器函數(shù)和合適的時鐘恢復(fù)設(shè)置(二階鎖相環(huán)或PLL,閉環(huán)帶寬是10MHz,阻尼系數(shù)為0.707)之后用100萬個連續(xù)單位間隔測量的。抖動結(jié)果的計算方法是以1 x 10-12的誤碼率(BER)從測量數(shù)據(jù)總量中提取抖動性能。例如,利用抖動外推法,目標RJ等于測量得到的RJ(rms)乘以14.069。

圖2顯示了標準化的發(fā)送端一致性測試裝置,其中包括參考測試通道和電纜。測試點2(TP2)最靠近被測設(shè)備(DUT),而測試點1(TP1)是遠端測量點。所有發(fā)送端的常規(guī)化測量都是在TP點的信號上進行的。

在TP1點采集到信號后,可以使用一款稱為SigTest的軟件工具進行數(shù)據(jù)處理,類似于正式的PCI Express一致性測試。對于要求預(yù)先一致性測試、表征或調(diào)試的應(yīng)用,還可以用其它工具深入觀察不同條件或參數(shù)下的設(shè)計行為。帶USB 3.0特定軟件的高速示波器可以提供自動的標準化和信息化PHY發(fā)送端測試。這些工具可以確保測試設(shè)備得到了正確配置,從而有效節(jié)省時間。

在測試完成后,一份詳細的通過/失敗測試報告將突出顯示可能存在設(shè)計問題的地方。如果在不同測試位置(例如公司實驗室,測試室)之間出現(xiàn)矛盾,應(yīng)該使用前次測試運行時保存的數(shù)據(jù)再次執(zhí)行測試。

在要求進一步分析的場合,可以用抖動分析和眼圖分析軟件進行查錯和設(shè)計表征。例如,一次可以顯示多個眼圖,允許工程師分析不同的時鐘恢復(fù)技術(shù)或分析軟件通道模型的效果。另外,可以使用不同的濾波器分析SSC效應(yīng),最終解決系統(tǒng)互操作性問題。

均衡考慮事項

由于有較大的通道衰減,SuperSpeed USB要求采用某種形式的補償機制來打開接收端的眼圖。發(fā)送端一般采用去加重形式的均衡技術(shù)。歸一化的去加重比率在線性刻度下規(guī)定為3.5dB或1.5x。舉例來說,當(dāng)跳變沿比特電平為150mVp-p時,非跳變沿比特電平將為100mVp-p。

CTLE一致性均衡實現(xiàn)包括裸片上的有源接收端均衡或無源高頻濾波器(比如電纜均衡器中使用的濾波器)。這種模型非常適合用于一致性測試,因為在描述轉(zhuǎn)移函數(shù)時非常簡單。CTLE實現(xiàn)在頻域有一組極點和零點,因此在目標頻率處會出現(xiàn)峰值。

CTLE實現(xiàn)對設(shè)計而言更加簡單,并且比替代性技術(shù)消耗更低的功率。然而,在某些情況下,由于適配性、精度和噪聲放大等方面的限制,它們可能還不夠。其它技術(shù)包括前饋均衡(FFE)和判定反饋均衡(DFE),這些技術(shù)使用經(jīng)比例因子加權(quán)的數(shù)據(jù)樣本來補償通道損耗。

CTLE和FFE都是線性均衡器,因此都會由于高頻噪聲的提升而出現(xiàn)信噪比的劣化。然而,DFE在反饋環(huán)路中使用非線性元件,因而能最大限度地減少噪聲放大,補償碼間干擾(ISI)。圖3所示例子顯示了經(jīng)過顯著通道衰減后的5Gbit/s信號以及使用去加重、CTLE和DFE技術(shù)均衡過的信號。

USB 3.0接收端測試

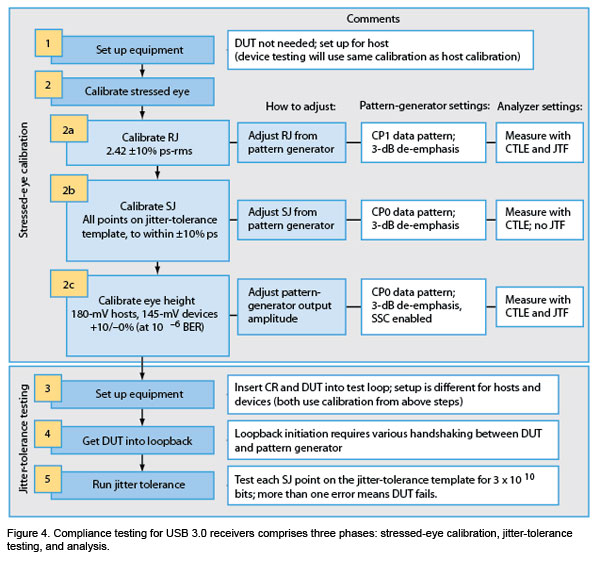

USB 3.0接收端測試類似于其它高速串行總線接收端的一致性測試,一般分為三個階段,開始是受壓眼圖校準,然后是抖動容限測試,最后是分析。下面讓我們看看這個過程的流程圖(圖4)。

受壓眼圖校準使用最糟糕信號,這個信號通常在垂直方向(通過增加的抖動)和水平方向(通過將幅度設(shè)置為接收端在部署時能看到的最低值)都有損傷。當(dāng)任何測試夾具、電纜或儀器發(fā)生改變時都必須執(zhí)行受壓眼圖校準。

抖動容限測試將校準后的受壓眼圖用作輸入,然后施加更高頻率帶來的附加正弦抖動(SJ)。這種SJ將作用于接收端內(nèi)的時鐘恢復(fù)電路,因此不僅使用最差信號條件測試了接收端,而且時鐘恢復(fù)也得到了明確的測試。最后,通過分析評估測試完成后是否需要執(zhí)行額外的設(shè)計任務(wù)才能達到一致性。

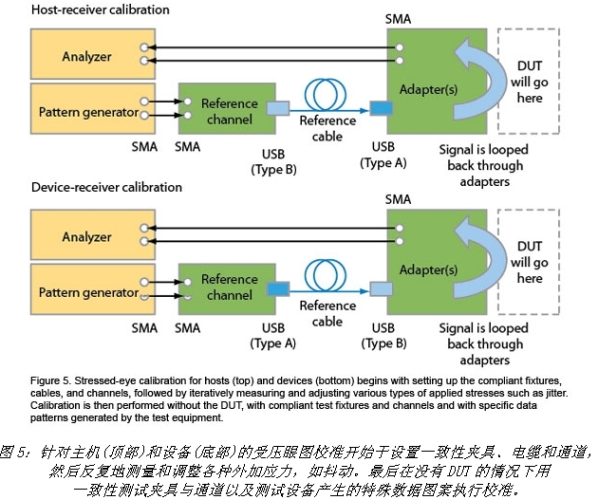

受壓眼圖校準過程首先要用一致性夾具、電纜和通道設(shè)置好測試設(shè)備(圖5)。下一步是反復(fù)測量和調(diào)整各種類型的外加應(yīng)力,如抖動。校準步驟執(zhí)行時不需要DUT,但需要一致性測試夾具、通道以及測試設(shè)備產(chǎn)生的特定數(shù)據(jù)圖案。測試儀器應(yīng)能執(zhí)行兩種功能——能夠增加各種應(yīng)力的圖案發(fā)生功能,以及抖動和眼圖測量等信號分析功能。

校準受壓眼圖時必須完成三種損傷校準:RJ、SJ和眼圖高度。每種校準都要求對圖案發(fā)生器和分析儀進行特定的設(shè)置。對每組電纜、適配器和儀器也必須做一次受壓眼圖校準。

由于使用不同的適配器和參考通道組,主機和設(shè)備將經(jīng)過不同的受壓眼圖校準過程。一旦完成后,校準眼圖的設(shè)置可以重復(fù)使用,只有當(dāng)設(shè)備設(shè)置發(fā)生改變時才必須做再次校準。

額外的圖案發(fā)生器要求

前面已經(jīng)介紹了要求校準的全部事項,下面讓我們再看看每步校準對圖案發(fā)生器的附加要求,包括使用的數(shù)據(jù)圖案、去加重程度、SSC是否應(yīng)激活等。在受壓眼圖校準方案中,列出了兩種圖案,即CP0和CP1。表3列出了所有的USB 3.0一致性圖案供參考。

CP0是一種8b/10b編碼、PRBS-16數(shù)據(jù)圖案(將D0.0字符送到USB 3.0發(fā)送端中進行擾碼和編碼的結(jié)果)。經(jīng)過8b/10b編碼后,最長的連1或連0長度從PRBS-16圖案中的16比特減少到了5個比特。CP3是類似于8b/10b編碼過的PRBS-16的圖案,其中包含最短(單個比特)和最長的相同比特序列。

CP1是用于RJ校準的時鐘圖案。許多儀器在RJ測量時采用dual-Dirac隨機與確定性抖動分離方法。使用時鐘圖案可以避免dual-Dirac方法的一些缺陷,例如將DDJ報告為RJ,特別是針對長圖案。通過使用時鐘圖案,作為ISI結(jié)果的DDJ將從抖動測量中消除,從而形成更精確的RJ測量結(jié)果。

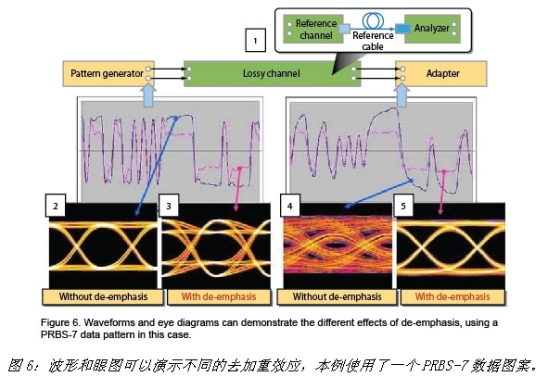

在圖案發(fā)生器和分析儀之間的有損通道(即USB 3.0參考通道和電纜)將導(dǎo)致垂直和水平方向表現(xiàn)為眼圖關(guān)閉的頻率相關(guān)損耗(圖6)。為了解決這種損耗問題,需要使用發(fā)送端去加重技術(shù)提升信號中的高頻分量,從而使BER為10-12或更高的工作鏈路有足夠好的接收眼圖。

從這些眼圖可以看出,沒有去加重時所有幅度名義上都是相同的。采用去加重后,跳變沿比特的幅度要高于非跳變沿比特的幅度,從而有效提升了信號的高頻分量。

在通過有損通道和電纜后,沒有經(jīng)過去加重處理的信號將受到碼間干擾(ISI)的影響,眼圖開度要比經(jīng)過了去加重的信號小。同時,采用去加重的信號是全開的。從這里可以看出,去加重程度會影響ISI和DDJ的程度,進而影響接收端的眼圖開度。

在同步數(shù)字系統(tǒng)(包括USB 3.0)中經(jīng)常使用SSC來減小電磁干擾(EMI)。如果不使用SSC,數(shù)字流頻譜中的載頻(即5Gbps)及其諧波處會出現(xiàn)大幅度的尖峰,并且有可能超過調(diào)整極限(圖7)。

為了防止出現(xiàn)這個問題,可以用SSC擴展頻譜能量。在這個案例中載頻被一個三角波所調(diào)制。用于接收端測試的頻率“擴展”量是5000ppm或25MHz,頻率調(diào)制周期為33kHz或每隔30μs,即三角波的一個周期。經(jīng)過SSC后,頻譜中的能量得到了擴展,不會再有單個頻率破壞規(guī)范極限。

如前所述,USB 3.0中的接收側(cè)均衡可以改善被碼間干擾損傷的信號,這種碼間干擾是由于參考通道和電纜中的頻率相關(guān)損耗引起的。這種概念等同于去加重——通過信號處理方法提升信號中的高頻分量。

雖然設(shè)備或主機中的接收端均衡電路與具體實現(xiàn)有關(guān),但USB 3.0標準為一致性測試規(guī)定了CTLE(圖8)。這種CTLE必須在進行一致性測試測量(都是針對發(fā)送端測試,在本例中是接收端受壓眼圖校準)之前,由誤碼率測試儀(BERT)或示波器等參考接收端實現(xiàn),并且通常采用軟件模擬的方式。

使用CTLE模擬進行抖動測量主要影響由信號處理方法引起的抖動,即ISI。CTLE模擬不影響與數(shù)據(jù)圖案(如RJ和SJ)不相關(guān)的抖動分量,雖然根據(jù)一致性測試規(guī)范(CTS)這兩種測量都要求使用CTLE。另一方面,眼圖高度會直接受到影響,因為ISI影響測量。

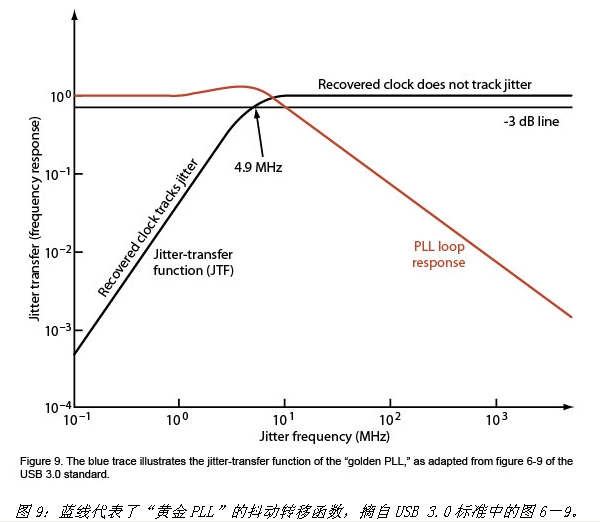

抖動測量時必須使用具有一致性抖動轉(zhuǎn)移函數(shù)(JTF)的時鐘恢復(fù)“黃金PLL”,如圖9中的藍線所示。JTF表明了有多少抖動從輸入信號轉(zhuǎn)移到下游分析儀。在本例中,-3dB截止頻率是4.9MHz。

在更低的SJ頻率(沿著JTF的傾斜部分,此處的PLL環(huán)路響應(yīng)是平坦的),恢復(fù)時鐘跟蹤數(shù)據(jù)信號上的抖動。這樣,相對于時鐘的數(shù)據(jù)抖動將按照JFT得到衰減。在較高的SJ頻率點,JTF變平,PLL響應(yīng)向下傾斜,信號中的SJ部分被轉(zhuǎn)移到下游分析儀。除了受壓眼圖校準期間的SJ外,所有測量都規(guī)定要使用一致性JTF。

一旦受壓眼圖完成校準,接收端測試就可以開始了。USB 3.0與以前的USB 2.0不同,要求進行BER測試。采用抖動容限測試形式的BER測試僅是接收端測試要求的測試項目。抖動容限測試使用最差輸入信號條件試驗接收端(受壓眼圖的校準見前面部分)。在受壓眼圖頂部,圍繞JTF的-3dB截止頻率且覆蓋一定頻率范圍的一系列SJ頻率和幅度被注入測試信號,同時由誤碼檢測器監(jiān)視接收端的錯誤或比特誤碼,并計算BER。

本文小結(jié)

隨著USB 3.0開始走向主流,需要對發(fā)送端和接收端進行成功的一致性和認證測試,這是將新產(chǎn)品推向市場的關(guān)鍵。這些產(chǎn)品不僅要求能與其它USB 3.0設(shè)備一起工作,而且要滿足消費者對各種條件下的性能和可靠性的期望值。

性能的急劇提高帶來了許多新的測試要求,也使得設(shè)計和認證比前代標準更具挑戰(zhàn)性。幸運的是,有一整套測試工具和資源可以用來協(xié)助SuperSpeed USB商標認證。