1引言

隨著ATM機(jī)普及,人們對(duì)流通貨幣質(zhì)量要求越來(lái)越高,鈔票清分工作對(duì)銀行業(yè)來(lái)說(shuō)就顯得格外重要。清分機(jī)是一種高端金融機(jī)具產(chǎn)品,能夠一次性完成鈔票的清分工作,包括鈔票點(diǎn)算、幣種識(shí)別、真?zhèn)舞b別、面額清分、版本清分、新舊清分、方位識(shí)別(包括正反面、上下方向等共4種組合)等。按照不同的功能,清分機(jī)的工作速度可達(dá)到每分鐘600張至1000張。

清分機(jī)的圖像采集系統(tǒng)主要是南圖像傳感器對(duì)在傳送帶上高速傳送的鈔票進(jìn)行采樣、緩存,然后送至DSP圖像處理模塊。該系統(tǒng)是以CPLD完成鈔票圖像信息采集時(shí)序控制和數(shù)據(jù)緩存,采用接觸式圖像傳感器(CIS)SV233A4W和模數(shù)轉(zhuǎn)換器AD9822實(shí)現(xiàn)圖像的采樣和量化功能。另外,使用碼盤(pán)和對(duì)管來(lái)實(shí)現(xiàn)傳送帶與采樣的同步。

2系統(tǒng)組成與原理

2.1系統(tǒng)組成

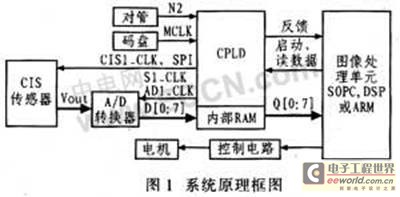

清分機(jī)的圖像采集系統(tǒng)主要由碼盤(pán)、對(duì)管、傳感器、A/D轉(zhuǎn)換器、CPLD等組成。CPLD是系統(tǒng)核心,控制各部分時(shí)序及數(shù)據(jù)采集。當(dāng)無(wú)鈔票時(shí),系統(tǒng)處于等待狀態(tài);當(dāng)有鈔票經(jīng)過(guò)對(duì)管時(shí),將產(chǎn)生一個(gè)觸發(fā)信號(hào),CPLD接收到觸發(fā)信號(hào)后,將控制接觸式圖像傳感器對(duì)鈔票進(jìn)行采樣,采樣間隔由碼盤(pán)信號(hào)分頻控制。采集到的圖像信息經(jīng)A/D轉(zhuǎn)換后,存儲(chǔ)到內(nèi)部RAM中,為圖像處理單元DSP的后續(xù)處理、識(shí)別提供數(shù)據(jù)。該系統(tǒng)原理框圖如圖1所示。

2.1.1 CIS SV233A4W簡(jiǎn)介

CIS是一種基于CMOS技術(shù)的線(xiàn)陣傳感器,它將光源、聚焦鏡片及感應(yīng)器固定于一個(gè)外罩內(nèi),具有體積小,成本低等特點(diǎn)。CIS適用于高速傳輸物體的表面圖像采集。

SV233A4W是一款單色(G)線(xiàn)性CIS傳感器,掃描寬度是216 mm,分辨率可達(dá)到200 dpi。該傳感器共有1728個(gè)像元,有CP(移位時(shí)鐘脈沖)和SP(啟動(dòng)脈沖)2個(gè)輸入控制信號(hào)。如果在CP的上升沿檢測(cè)到SP為高電平,則啟動(dòng)一行的掃描和串行移位輸出工作。在每個(gè)CP的下降沿,Vout端口輸出一個(gè)點(diǎn)的模擬電壓值,這樣經(jīng)過(guò)1 728個(gè)CP時(shí)鐘后,一行的數(shù)據(jù),等待下一個(gè)SP啟動(dòng)信號(hào)。掃描一行的典型時(shí)間為0.5 ms。

2.1.2 A/D轉(zhuǎn)換器AD9822簡(jiǎn)介

AD9822是號(hào)門(mén)對(duì)CCD/CIS模擬圖像進(jìn)行模/數(shù)轉(zhuǎn)換的器件,輸出動(dòng)態(tài)范圍是14位,可同時(shí)對(duì)3路RGB信號(hào)進(jìn)行A/D轉(zhuǎn)換。

AD9822具有3路RGB相互獨(dú)立的采樣和輸出結(jié)構(gòu),每一路包括:相關(guān)雙采樣器(CCD)、偏移控制D/A轉(zhuǎn)換器和數(shù)控增益放大器(PGA)。3路模擬信號(hào)經(jīng)選擇器依次輸出,后經(jīng)14位A/D轉(zhuǎn)換器獲得數(shù)字信號(hào),這14位數(shù)字信號(hào)分兩字節(jié)先后輸出(D0~D7)。該器件工作時(shí)設(shè)有3個(gè)時(shí)鐘,CDSCLK1是參考電平(OFFSEET)的采樣時(shí)鐘,CDSCLK2是輸入數(shù)據(jù)電平的采樣時(shí)鐘,ADCCLK(是模數(shù)轉(zhuǎn)換和控制數(shù)據(jù)輸出的時(shí)鐘。

AD9822共有4種工作模式,即3通道CDS模式、1通道CDS模式、3通道SHA模式和1通道SHA模式。在1通道模式中,只處理一路模擬信號(hào),而3通道模式則同時(shí)處理3路信號(hào)。這里采用3通道SHA模式,在該模式下一個(gè)采樣時(shí)鐘CDSCLK2后需要3個(gè)輸出時(shí)鐘ADCCLK輸出數(shù)據(jù)。

該器件內(nèi)部各路偏移D/A轉(zhuǎn)換器、PGA和模式的設(shè)置等都是由內(nèi)部8個(gè)寄存器(地址為000~111)完成的,這些寄存器是由3個(gè)端口信號(hào)SCLK、SLOAD和SDATA控制。

2.1.3碼盤(pán)

碼盤(pán)是一種常用的增量式角度傳感器(圖2),利用現(xiàn)代光刻技術(shù)在圓盤(pán)上均勻刻線(xiàn),當(dāng)圓盤(pán)旋轉(zhuǎn)時(shí),受刻線(xiàn)影響接收管接收到的光線(xiàn)出現(xiàn)亮暗變化,而輸出電平則高低跳變。將碼盤(pán)安裝在電機(jī)上,電機(jī)旋轉(zhuǎn)時(shí),便有脈沖信號(hào)從碼盤(pán)輸出。輸出的脈沖信號(hào)可與電機(jī)相連的傳送帶傳送的距離進(jìn)行換算,通過(guò)控制碼盤(pán)輸出脈沖的分頻來(lái)控制鈔票的采樣間隔。

2.1.4對(duì)管

對(duì)管位于CIS傳感器的上游,用于指示樣品(鈔票)的到來(lái)。當(dāng)對(duì)管被物體遮擋時(shí),對(duì)管輸出高電平,否則維持低電平。在應(yīng)用中對(duì)管輸出高電平的脈寬與鈔票全部通過(guò)的時(shí)長(zhǎng)相等。因而可以利用對(duì)管輸出信號(hào)(N2)控制每幀圖像的采樣使能。考慮到信號(hào)噪聲的影響,需對(duì)管信號(hào)濾波;為保證每幀圖像(包括整張鈔票)具備一定余量,需要延時(shí)處理N2信號(hào)。

2.2采樣原理

由于要從圖像采樣數(shù)據(jù)中提取出鈔票的各種特征信息,所以圖像采樣數(shù)據(jù)要確保無(wú)失真地恢復(fù)鈔票圖像信息。因此,采樣頻率需滿(mǎn)足二維取樣定理。假設(shè)鈔票圖像的頻譜在水平方向上的截止頻率為fm,在垂直方向的截止頻率為fm,則只要水平方向的空間取樣頻率F0滿(mǎn)足F0≥2Fm,垂直方向的空間取樣頻率fm滿(mǎn)足f0≥2fm條件,圖像便可精確恢復(fù)。水平方向的采樣頻率由圖像傳感器的性能決定,而垂直方向的采樣頻率則由碼盤(pán)信號(hào)的分頻決定。

3 CPLD控制實(shí)現(xiàn)

3.1系統(tǒng)總時(shí)序

該系統(tǒng)設(shè)計(jì)的關(guān)鍵在于圖像傳感器、A/D轉(zhuǎn)換器以及數(shù)據(jù)存儲(chǔ)器RAM之間的時(shí)序控制。系統(tǒng)的總時(shí)序關(guān)系為:對(duì)管信號(hào)N2是采樣一張鈔票的總使能,碼盤(pán)信號(hào)MCLK的分頻SP作為每一行采樣的啟動(dòng)信號(hào)。在每一行的采樣過(guò)程中,通過(guò)傳感器移位時(shí)鐘CIS1_CLK將每一點(diǎn)的數(shù)據(jù)移出。通過(guò)時(shí)鐘S1_CLK2控制A/D轉(zhuǎn)換器讀取采樣的模擬數(shù)據(jù),并由輸出時(shí)鐘AD1_CLK控制A/D轉(zhuǎn)換器輸出量化的數(shù)字?jǐn)?shù)據(jù)。然后,在地址時(shí)鐘ADR0_CLK和寫(xiě)時(shí)鐘WR_CLK的控制下寫(xiě)入RAM,系統(tǒng)總時(shí)序如圖3所示。

3.2參數(shù)確定

根據(jù)CIS SV233A4W傳感器特性可知,啟動(dòng)脈沖SP的脈寬應(yīng)大于100 ns,而移位時(shí)鐘CIS1_CLK最大頻率為5MHz。脈寬大于50 ns,采樣一行的典型時(shí)間是0.5 ms。若每張鈔票需采樣60行,則一張鈔票最少需要30 ms,1分鐘最多可采樣1800張鈔票。傳感器的輸出數(shù)據(jù)相對(duì)于移位時(shí)鐘的延時(shí)為68ns,所以A/D轉(zhuǎn)換器AD9822的讀取時(shí)鐘S1_CLK2與移位時(shí)鐘CIS1_CU(需滿(mǎn)足上述關(guān)系。由A/D轉(zhuǎn)換器AD9822的特性可知,讀取時(shí)鐘S1_CLK2的脈寬大于10 ns,輸出時(shí)鐘AD1_CLK大于30 ns。S1_CLK2的頻率與CIS1_CLK相同,AD1_CLK的頻率應(yīng)該是S1_CLK2的3倍頻(3通道SHA模式),而相位應(yīng)在S1_CLK2之后。

3.3設(shè)計(jì)實(shí)現(xiàn)

CPLD的內(nèi)部結(jié)構(gòu)如圖4所示。CLOCK(50 MHz)為系統(tǒng)的基準(zhǔn)時(shí)鐘,通過(guò)分頻器件DIV_N產(chǎn)生不同倍率的分頻時(shí)鐘。DIV_N輸出的分頻時(shí)鐘(S1、AD1、WR、ADR0)作為系統(tǒng)中各時(shí)鐘的基本信號(hào),與行采樣使能SAMPLE_EN邏輯與后,得到傳感器移位時(shí)鐘CIS1_CLK,A/D采樣時(shí)鐘S1_CLK2,A/D轉(zhuǎn)換輸出時(shí)鐘AD1_CLK,RAM地址時(shí)鐘ADR0_CLK和RAM寫(xiě)時(shí)鐘WR_CLK信號(hào),這些時(shí)鐘信號(hào)只有在輸入有效數(shù)據(jù)時(shí)使能,這樣可避免讀人干擾數(shù)據(jù),還可降低系統(tǒng)功耗。在DIV_N中僅采用一個(gè)計(jì)數(shù)信號(hào)對(duì)CLOCK上升沿計(jì)數(shù),計(jì)數(shù)狀態(tài)下,根據(jù)所需波形輸出特定向量,共用一個(gè)計(jì)數(shù)信號(hào)實(shí)現(xiàn)不同倍率分頻,嚴(yán)格保證信號(hào)之間的相位關(guān)系。

對(duì)管信號(hào)N2和碼盤(pán)輸出脈沖信號(hào)MCLK,在電平跳變的前后產(chǎn)生的毛刺可采用數(shù)字可重觸發(fā)器FILTER_16濾除。CLK為同步時(shí)鐘;當(dāng)輸入信號(hào)Vin_L為低電平時(shí),Vout為高電平,并對(duì)內(nèi)部計(jì)數(shù)器同步置數(shù)15;當(dāng)輸入信號(hào)Vin_L為高電平時(shí),計(jì)數(shù)器由計(jì)數(shù)值15對(duì)CLK上升沿遞減計(jì)數(shù),計(jì)數(shù)至0時(shí),Vout在下一個(gè)CLK上升沿輸出低電平;CL對(duì)Vout和內(nèi)部計(jì)數(shù)器異步清零,初始化。Vout信號(hào)可用于濾除負(fù)脈沖Vin_L的毛刺,Vout的下降沿相對(duì)于Vin_L的上升沿有16個(gè)CLK時(shí)鐘延時(shí)。

總使能信號(hào)IMAGE_EN是N2信號(hào)經(jīng)濾波、延時(shí)后得到的,它和碼盤(pán)分頻信號(hào)SP拓寬后的信號(hào)SP_1728邏輯相與后得到行采樣使能信號(hào)SAMPLE_EN,用于控制采樣間隔。這里SP是將碼盤(pán)輸出信號(hào)MCLK經(jīng)DIV_6六分頻,再經(jīng)單穩(wěn)態(tài)電路DIFF得到的分頻數(shù)可根據(jù)實(shí)際參數(shù)(碼盤(pán)刻線(xiàn)精度、電機(jī)轉(zhuǎn)速)修改。DIFF可以將前面的分頻信號(hào)變?yōu)槊}寬為1個(gè)時(shí)鐘周期的脈沖信號(hào),其內(nèi)部標(biāo)識(shí)狀態(tài)為Q1Q0。當(dāng)輸入脈沖Sin為低電平時(shí),Q1Q0=00,輸出脈沖Sout=0;Sin為高電平時(shí),Q1Q0=00,表明Sin的上升沿出現(xiàn)在前一個(gè)時(shí)鐘周期,Sin=1,并Q1Q0=11;若Q1Q0≠00,則表明Sin的上升沿并非剛到達(dá),Sout清零,Q1Q0=10。

信號(hào)SP_1728的脈寬為1 728個(gè)移位時(shí)鐘周期,確保在每一行采樣的過(guò)程中,全部且僅將1 728個(gè)點(diǎn)的圖像信息輸出。內(nèi)部RAM的寫(xiě)地址端接人一個(gè)12位加法計(jì)數(shù)器ADDRESS_12b,對(duì)ADRO_CLK計(jì)數(shù),輸出RAM的12位寫(xiě)地址,清零端接CIS SV233A4W的啟動(dòng)信號(hào)SP。

4仿真與結(jié)果分析

4.1時(shí)序控制仿真

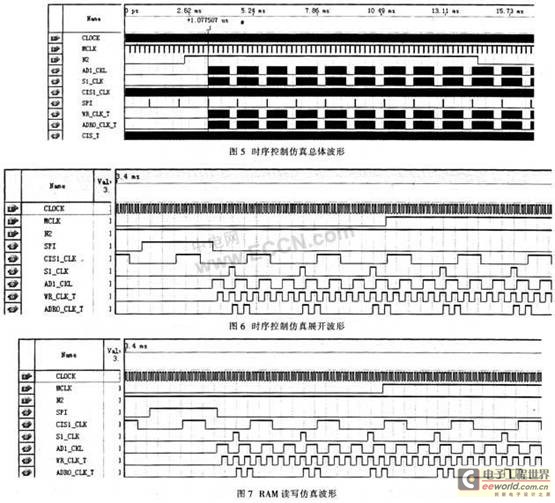

按照系統(tǒng)設(shè)計(jì)結(jié)構(gòu),該系統(tǒng)輸入時(shí)鐘CLOCK的頻率為50 MHz,碼盤(pán)信號(hào)頻率為6 kHz,其仿真波形如圖5和圖6所示。由仿真波形可看出,滿(mǎn)足系統(tǒng)要求中時(shí)序關(guān)系,由于A/D轉(zhuǎn)換器只有一路輸入,所以每3個(gè)輸出數(shù)據(jù)有一組數(shù)據(jù)為有效地址。

4.2 RAM讀寫(xiě)仿真

存儲(chǔ)在CPLD內(nèi)部RAM的采樣數(shù)據(jù)要由后續(xù)DSP處理模塊讀取。在寫(xiě)時(shí)鐘wrclock的作用下,從地址0開(kāi)始向RAM依次寫(xiě)入0、1、2、3……,然后在RAM的讀時(shí)鐘端施加一個(gè)讀時(shí)鐘rdclock,在讀地址rdaddress端施加從0遞增的讀地址,仿真RAM的讀寫(xiě),得到的仿真波形如圖7所示。由仿真波形可以看出,RAM的讀寫(xiě)正確,讀取的數(shù)據(jù)相對(duì)于讀時(shí)鐘有一定延時(shí)。

5結(jié)語(yǔ)

該高速圖像采集裝置已在鈔票清分機(jī)中得到良好應(yīng)用。該系統(tǒng)設(shè)計(jì)也可應(yīng)用于連續(xù)、高速的圖像采集系統(tǒng),另外,還可采用接觸式傳感器,使其具有曝光時(shí)間短,感光速度和數(shù)據(jù)傳輸速度快,實(shí)現(xiàn)高效輸入等特點(diǎn),從而能夠很好的滿(mǎn)足清分機(jī)對(duì)采樣圖像質(zhì)量的要求。