1 引言

大容量數(shù)據(jù)的高速傳輸是存儲(chǔ)技術(shù)的研究的熱點(diǎn)技術(shù),而在工業(yè)環(huán)境的數(shù)據(jù)傳輸中抗干擾技術(shù)以及醫(yī)療設(shè)備對(duì)人身的安全也是目前研究的熱門(mén)課題,USB(Universal Serial Bus)是 “通用串行總線”。它是一種應(yīng)用在 PC領(lǐng)域的接口技術(shù)。其主要優(yōu)點(diǎn)是:可以熱插拔、攜帶方便、標(biāo)準(zhǔn)統(tǒng)一,因而得到了廣泛的應(yīng)用。 USB用于測(cè)試與測(cè)量應(yīng)用的優(yōu)勢(shì)很多,使用 USB接口的設(shè)備也與日俱增,例如數(shù)碼相機(jī)、掃描儀、圖像設(shè)備、醫(yī)療設(shè)備、打印機(jī)等等。在工業(yè)環(huán)境自動(dòng)化程度較高的現(xiàn)場(chǎng),醫(yī)療設(shè)備對(duì)人體信息的提取和診斷,大量信息數(shù)據(jù)的獲取與存儲(chǔ)往往應(yīng)用快速的 USB接口來(lái)實(shí)現(xiàn),而目前的 USB接口對(duì)工業(yè)干擾非常敏感,在醫(yī)療上對(duì)人身安全存在隱患,USB的隔離應(yīng)用是基于 PC平臺(tái)的醫(yī)療設(shè)備和具有很大地電位差的工業(yè)應(yīng)用。本文提出基于 CPLD的 USB隔離技術(shù),實(shí)現(xiàn)了 USB總線的可靠安全通信,在工業(yè)現(xiàn)場(chǎng)和醫(yī)療設(shè)備通信接口中發(fā)揮著重要作用。

2 系統(tǒng)硬件構(gòu)成及工作原理

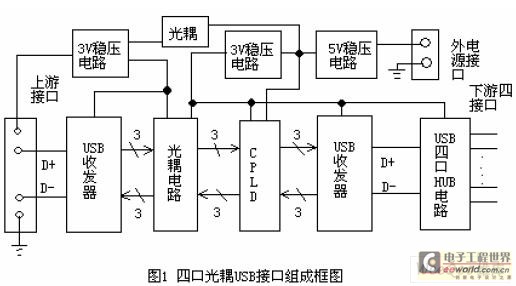

全速(12Mbps) USB連接的光隔離,12Mbps的速度可滿足一般數(shù)據(jù)傳輸?shù)膸捯螅O(shè)計(jì)中使用廉價(jià)耦合器,支持足夠的數(shù)據(jù)傳輸速率。 USB連接器包含四條線:2條用于電源供電(VBUS和 GND),2條用于 USB數(shù)據(jù)傳輸(D+和 D-)。VBUS提供 5V電源,電流可達(dá) 500mA。D+和 D-為雙向信號(hào)線,信號(hào)傳輸速率為 12Mbps (每位 83ns)。D+和 D-信號(hào)電平為 3.3V。圖 1所示隔離 USB接口組成框圖,系統(tǒng)主要由 USB收發(fā)器 SP5301、光藕電路、主控芯片 CPLD、USB四口 HUB電路 TUSB2046B、電源隔離五部分構(gòu)成。

隔離系統(tǒng)的工作原理:差分信號(hào)是以半雙工的形式實(shí)現(xiàn)的,就是說(shuō),數(shù)據(jù)線的任何一部分都可以傳送和接收數(shù)據(jù),但是在任意時(shí)刻只能進(jìn)行發(fā)送或者只能進(jìn)行接收,兩者不能同時(shí)進(jìn)行。半雙工實(shí)現(xiàn)要求驅(qū)動(dòng)器在不傳送數(shù)據(jù)時(shí)進(jìn)入高阻抗?fàn)顟B(tài)。基于此原理,利用 CPLD的控制能力,使其處于上下游的接收狀態(tài),一旦檢測(cè)到一方有信息包到來(lái),立即進(jìn)行隔離通路的切換,完成信號(hào)隔離通過(guò),且保證信號(hào)的完整性。

工作過(guò)程:外電源接口上電,通過(guò)穩(wěn)壓電路提供 5V、3V電壓,分別給 CPLD的 I/O口, CPLD核、下游藕合電路、 USB收發(fā)器、四口 HUB電路提供電源。CPLD完成復(fù)位后,產(chǎn)生控制光耦信號(hào),使上游口上電(由上位機(jī) USB接口提供,節(jié)省上位機(jī)電源)。 CPLD處于上下游接收狀態(tài),當(dāng)上游差分信號(hào)到達(dá) USB收發(fā)器后,收發(fā)器將差分信號(hào)轉(zhuǎn)換為 VP、VM、 RESO三個(gè)信號(hào),經(jīng)光電耦合電路后進(jìn)入 CPLD檢測(cè)、處理、切換,再經(jīng)下游 USB收發(fā)器轉(zhuǎn)換為差分信號(hào),送入四口 HUB電路解析處理。反之亦然。

系統(tǒng)的軟件設(shè)計(jì)與實(shí)現(xiàn)

CPLD是整個(gè)系統(tǒng)的控制核心,軟件的設(shè)計(jì)好壞關(guān)系到整個(gè)系統(tǒng)的穩(wěn)定性和可靠性。CPLD采用 XILINX公司的 XC95144XL,具有集成度高、可靠性好及工作速度快等優(yōu)點(diǎn),開(kāi)發(fā)軟件功能強(qiáng)大、靈活易用、升級(jí)方便。考慮到 USB信號(hào)速度高,要求切換快,便于升級(jí),功耗低,綜合各種因素選用該芯片。CPLD的主要功能是: 1)對(duì) 50MHZ的時(shí)鐘信號(hào)進(jìn)行分頻,產(chǎn)生系統(tǒng)所需的各種時(shí)鐘信號(hào);2)為電源的上電順序提供監(jiān)測(cè)和控制信號(hào); 3)實(shí)時(shí)判斷信息包并及時(shí)為 USB收發(fā)器提供轉(zhuǎn)換控制信號(hào);4)為 TUSB2046B提供復(fù)位信號(hào),監(jiān)測(cè)四口 HUB的 Suspend信號(hào)并產(chǎn)生復(fù)位信號(hào)為上游設(shè)備; CPLD控制邏輯狀態(tài)轉(zhuǎn)換圖如圖 2所示,系統(tǒng)上電后,CPLD初始化,并為 TUSB2046B產(chǎn)生足夠的復(fù)位信號(hào),使其正常穩(wěn)定工作,然后使自己處于上下游接收狀態(tài),若上游有信息包,則立即轉(zhuǎn)換下游處于發(fā)送狀態(tài),讓包信號(hào)完全通過(guò),包結(jié)束時(shí),又回到上下游接收狀態(tài)。若下游有信息包時(shí),按上述方法上傳。

設(shè)計(jì)實(shí)現(xiàn)應(yīng)用 XILINX公司的集成開(kāi)發(fā)環(huán)境 ISE6.3,用 VHDL語(yǔ)言進(jìn)行描述,采用自頂向下的方法進(jìn)行設(shè)計(jì)。考慮到系統(tǒng)的對(duì)稱性,在此僅畫(huà)出下游的控制邏輯關(guān)系,圖 3所示為下游監(jiān)測(cè)與控制的邏輯關(guān)系框圖,上游沒(méi)有 down_suspend監(jiān)測(cè)和復(fù)位產(chǎn)生電路,其它完全一致。

4 仿真結(jié)果

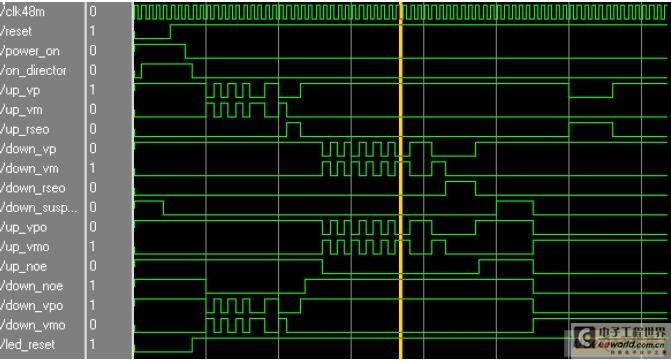

該 USB隔離系統(tǒng)通過(guò) ModelsimXE5.7C進(jìn)行了波形仿真,仿真波形如圖 4所示。從波形上可看出:上下游信息包信號(hào)都能完整地通過(guò),所需的控制信號(hào)及復(fù)位信號(hào)滿足理論設(shè)計(jì)要求,驗(yàn)證了工作原理的正確性。

5 結(jié)論

本設(shè)計(jì)的主要?jiǎng)?chuàng)新點(diǎn)在于 USB總線的協(xié)議的復(fù)雜性和快速性為設(shè)計(jì)實(shí)現(xiàn)必須面對(duì)許多的挑戰(zhàn),能在分析協(xié)議的基礎(chǔ)上利用 CPLD解決了 USB總線隔離的問(wèn)題,巧妙的檢測(cè)信息包起始、快切換和包結(jié)束的難題,克服了傳輸信息包結(jié)束慢上拉與過(guò)渡,保證系統(tǒng)的完整性。在各種不同傳輸信號(hào)中,采用各自不同的處理方式,不影響傳輸線的指標(biāo)和參數(shù),使系統(tǒng)穩(wěn)定可靠,該設(shè)計(jì)在實(shí)際的醫(yī)療設(shè)備對(duì)人體測(cè)試中達(dá)到了預(yù)期的效果。實(shí)驗(yàn)結(jié)果也證明,在后序的網(wǎng)絡(luò)信息安全的具有生物特征識(shí)別功能的 USB研究中提供重要的指導(dǎo)意義。