引言

80+和計算機(jī)產(chǎn)業(yè)拯救氣候行動計劃(Climate Savers Computing) 給計算機(jī)電源設(shè)立了一個強(qiáng)有力的效率標(biāo)準(zhǔn)。這些標(biāo)準(zhǔn)的“白金”級別規(guī)定計算機(jī)電源在20%額定負(fù)載狀態(tài)下必須有90%的效率,50%額定負(fù)載時效率必須達(dá)到94%,而在100%負(fù)載時效率必須達(dá)到91%。為了滿足這些標(biāo)準(zhǔn),一些電源設(shè)計人員選擇使用一個具有同步整流的相移、全橋接DC/DC轉(zhuǎn)換器。這種拓?fù)浣Y(jié)構(gòu)是一種比較好的選擇,因為它可以在主FET上實(shí)現(xiàn)零電壓開關(guān)(ZVS)。一種普遍使用的驅(qū)動同步整流器的方法是利用已經(jīng)存在的信號驅(qū)動主FET。這樣做存在的唯一問題是要求主FET時滯,以實(shí)現(xiàn)零電壓開關(guān)。這會導(dǎo)致兩個同步整流器在快速續(xù)流期間同時關(guān)閉,從而允許過多的體二極管導(dǎo)電,最終降低系統(tǒng)效率。本文的目的是建議使用不同的時序,驅(qū)動這些同步整流器,從而減少體二極管導(dǎo)電并最終提高整體系統(tǒng)效率。

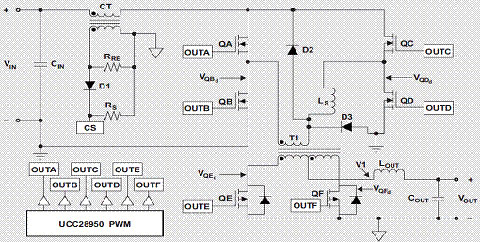

市場上有一些脈寬調(diào)制器(PWM),其設(shè)計目標(biāo)是用于控制相移、全橋接轉(zhuǎn)換器,而非驅(qū)動同步整流器(QE和QF)。工程師們發(fā)現(xiàn)他們可以通過PWM控制器的控制信號OUTA和OUTB來控制同步FET,這樣便可以在本應(yīng)用中使用這些控制器。圖1顯示了其中一款轉(zhuǎn)換器中的一個功能示意圖。

圖1 同步整流改進(jìn)型相移、全橋接轉(zhuǎn)換器

問題

通過延遲H橋接(QA、QB、QC、QD)的FET導(dǎo)通,PWM控制器有助于在這些轉(zhuǎn)換器中實(shí)現(xiàn)ZVS。FET QA和QB導(dǎo)通和斷開轉(zhuǎn)換過渡之間的延遲(tDelay)會使同步FET QE和QF同時斷開,從而允許其主體二極管實(shí)施上述導(dǎo)電行為。下列方程式較好地估算了續(xù)流期間QE和QF的主體二極管傳導(dǎo)損耗:

![]()

其中POUT為輸出功率,VOUT為輸出電壓,VD為主體二極管的正向壓降,而fs為電感開關(guān)頻率。

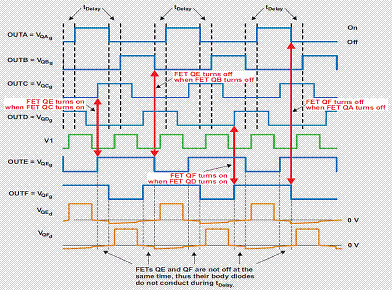

QE和QF的主體二極管傳導(dǎo)損耗(PDiode)過多會使設(shè)計達(dá)不到“白金”標(biāo)準(zhǔn)。更多詳情,請參見圖1和圖2。如圖所示,OUTA驅(qū)動FET QA和QF,而OUTB驅(qū)動FET QB和QE。V1為LOUT和COUT濾波器網(wǎng)絡(luò)輸入的電壓,而VQEd和VQFd為相應(yīng)同步整流器QE和QF的電壓。

圖2 圖1所示轉(zhuǎn)換器的時序圖

解決方案

若想減少Q(mào)E和QF主體二極管導(dǎo)電,最好是在QA和QB延遲期間(tDelay) 讓這些同步整流器開啟。要做到這一點(diǎn),必須通過其自有輸出來驅(qū)動FET QE和QF,其中“導(dǎo)通”時間而非同步的“斷開”時間會重疊。圖3顯示了具有6個單獨(dú)驅(qū)動信號(OUTA到OUTF)的相移、全橋接轉(zhuǎn)換器的功能示意圖。通過根據(jù)QA到QD的邊緣,導(dǎo)通和斷開OUTE及OUTF,可以產(chǎn)生QE(OUTE)和QF(OUTF)的信號。表1和圖4顯示了完成這項工作所需的時序。圖4所示理論波形表明,這種技術(shù)去除了主體二極管導(dǎo)電,其會在tDelay期間兩個柵極驅(qū)動均為斷開時,與圖2所示柵極驅(qū)動信號一起出現(xiàn)。

表1 OUTE和OUTF導(dǎo)通/斷開過渡轉(zhuǎn)換

圖3 使用表1時序的相移、全橋接轉(zhuǎn)換器

圖4 減少Q(mào)E和QF體二極管導(dǎo)電的時序圖

試驗結(jié)果

為了查看這種技術(shù)在減少主體二極管導(dǎo)電方面的效果如何,我們對一個390-V到12-V相移、全橋接轉(zhuǎn)換器進(jìn)行了改進(jìn),旨在通過圖2和4所示信號驅(qū)動FET。

圖5顯示了同步FET(QE和QF)柵極的波形圖,它們通過OUTA和OUTB PWM輸出驅(qū)動。圖中,在OUTA和OUTB之間的延遲時間(tDelay) 期間可以觀測到主體二極管導(dǎo)電。

圖5 QE和QF主體二極管導(dǎo)電波形圖

圖6顯示了同步FET(QE和QF)柵極的波形圖,它們通過圖3所示OUTE和OUTF信號驅(qū)動。這些信號都產(chǎn)生自TI新的UCC28950相移、全橋接控制器。圖6表明FET QE和QF導(dǎo)通的同時主體二極管沒有導(dǎo)電。盡管仍然可以看到一些主體二極管導(dǎo)電,但沒有圖5那么多。

圖6 顯示了QE和QF低主體二極管導(dǎo)電的波形圖

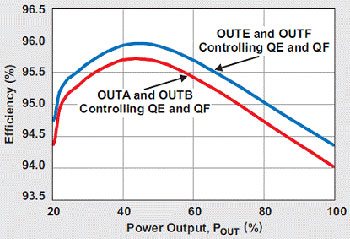

我們對兩種驅(qū)動方案(OUTA和OUTB與OUTE和OUTF)從20%到滿負(fù)載條件下600-W DC/DC轉(zhuǎn)換器的效率進(jìn)行了測量。在下一頁的圖7中,顯示了這兩種驅(qū)動方案的轉(zhuǎn)換器效率數(shù)據(jù)。我們可以看到,相比使用OUTA和OUTB,在50%到100%負(fù)載時使用OUTE和OUTF的效率高出約0.4%。0.4%效率增加看起來似乎并不多,但在設(shè)計人員努力想要達(dá)到“白金”標(biāo)準(zhǔn)時效果就不一樣了。

圖7 不同QE和QF驅(qū)動方案下600-W DC/DC轉(zhuǎn)換器的效率

結(jié)論

即使我們可以通過一個并非為同步整流(OUTA和OUTB驅(qū)動方案)而設(shè)計的相移、全橋接控制器來對一個具有同步整流器的相移、全橋接轉(zhuǎn)換器進(jìn)行控制,實(shí)現(xiàn)ZVS所要求的OUTA和OUTB之間接通延遲也會使兩個同步FET在同一時間(tDelay) 關(guān)閉。這種延遲會導(dǎo)致在FET快速續(xù)流期間出現(xiàn)過多的體二極管導(dǎo)電。本文表明更加有效的方法是:在快速續(xù)流期間疊加同步整流器的“接通”時間,以便讓體二極管不導(dǎo)電。利用這種方法,雖然體二極管導(dǎo)電并沒有完全消失,但其被極大減少,從而提高了整體系統(tǒng)效率,讓“白金”效率標(biāo)準(zhǔn)更容易達(dá)到。