摘要:本文針對(duì)由FPGA

FPGA

現(xiàn)場可編程邏輯門陣列(FPGA, Field Programmable Gate Array),是一個(gè)含有可編輯元件的半導(dǎo)體設(shè)備,可供使用者現(xiàn)場程式化的邏輯門陣列元件。FPGA是在PAL、GAL、CPLD等可編輯器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。 [全文]

構(gòu)成的高速數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)處理能力弱的問題,提出FPGA與單片機(jī)

單片機(jī)

單片機(jī)是單片微型計(jì)算機(jī)(Single-Chip Microcomputer)的簡稱,是一種將中央處理器CPU隨機(jī)存儲(chǔ)器RAM、只讀存儲(chǔ)器ROM、多種I/O口和中斷系統(tǒng)、定時(shí)器/計(jì)時(shí)器等功能(可能還包括顯示驅(qū)動(dòng)電路、脈寬調(diào)制電路、模擬多路轉(zhuǎn)換器、A/D轉(zhuǎn)換器等電路)采用超大規(guī)模集成電路技術(shù)集成到一塊硅片上構(gòu)成的微型計(jì)算機(jī)系統(tǒng)。 [全文]

實(shí)現(xiàn)數(shù)據(jù)串行通信的解決方案。在通信過程中完全遵守RS232協(xié)議,具有較強(qiáng)的通用性和推廣價(jià)值。

1 前言

現(xiàn)場可編程邏輯器件(FPGA)在高速采集系統(tǒng)中的應(yīng)用越來越廣,由于FPGA對(duì)采集到的數(shù)據(jù)的處理能力比較差,故需要將其采集到的數(shù)據(jù)送到其他CPU

CPU

CPU也稱為中央處理器,是電子計(jì)算機(jī)的主要設(shè)備之一。其功能主要是解釋計(jì)算機(jī)指令以及處理計(jì)算機(jī)軟件中的數(shù)據(jù)。所謂的計(jì)算機(jī)的可編程性主要是指對(duì)CPU的編程。CPU是計(jì)算機(jī)中的核心配件,只有火柴盒那么大,幾十張紙那么厚,但它卻是一臺(tái)計(jì)算機(jī)的運(yùn)算核心和控制核心。計(jì)算機(jī)中所有操作都由CPU負(fù)責(zé)讀取指令,對(duì)指令譯碼并執(zhí)行指令的核心部件。CPU、內(nèi)部存儲(chǔ)器和輸入/輸出設(shè)備是電子計(jì)算機(jī)的三大核心部件。 [全文]

系統(tǒng)來實(shí)現(xiàn)數(shù)據(jù)的處理功能,這就使FPGA系統(tǒng)與其他CPU系統(tǒng)之間的數(shù)據(jù)通信提到日程上,得到人們的急切關(guān)注。本文介紹利用VHDL語言實(shí)現(xiàn) FPGA與單片機(jī)的串口

串口

串口是計(jì)算機(jī)上一種非常通用的設(shè)備通信協(xié)議,大多數(shù)計(jì)算機(jī)包含兩個(gè)基于RS232的串口。串口同時(shí)也是儀器儀表設(shè)備的通信協(xié)議,并可用于獲取遠(yuǎn)程采集設(shè)備的數(shù)據(jù)。 [全文]

異步通信電路。

整個(gè)設(shè)計(jì)采用模塊化的設(shè)計(jì)思想,可分為四個(gè)模塊:FPGA數(shù)據(jù)發(fā)送模塊,F(xiàn)PGA波特率發(fā)生控制模塊,F(xiàn)PGA總體接口模塊以及單片機(jī)數(shù)據(jù)接收模塊

接收模塊

接收模塊的工作電壓為5伏,靜態(tài)電流4毫安,它為超再生接收電路,接收靈敏度為-105dbm,接收天線最好為25~30厘米的導(dǎo)線,最好能豎立起來。接收模塊本身不帶解碼集成電路,因此接收電路僅是一種組件,只有應(yīng)用在具體電路中進(jìn)行二次開發(fā)才能發(fā)揮應(yīng)有的作用,這種設(shè)計(jì)有很多優(yōu)點(diǎn),它可以和各種解碼電路或者單片機(jī)配合,設(shè)計(jì)電路靈活方便。 [全文]

。本文著重對(duì)FPGA數(shù)據(jù)發(fā)送模塊實(shí)現(xiàn)進(jìn)行說明。

2 FPGA數(shù)據(jù)發(fā)送模塊的設(shè)計(jì)

根據(jù)RS232 異步串行通信來的幀格式,在FPGA發(fā)送模塊中采用的每一幀格式為:1位開始位+8位數(shù)據(jù)位+1位奇校驗(yàn)位+1位停止位,波特率為2400。本系統(tǒng)設(shè)計(jì)的是將一個(gè)16位的數(shù)據(jù)封裝成高位幀和低位幀兩個(gè)幀進(jìn)行發(fā)送,先發(fā)送低位幀,再發(fā)送高位幀,在傳輸數(shù)據(jù)時(shí),加上文件頭和數(shù)據(jù)長度,文件頭用555555來表示,只有單片機(jī)收到555555時(shí),才將下面?zhèn)鬏數(shù)臄?shù)據(jù)長度和數(shù)據(jù)位進(jìn)行接收,并進(jìn)行奇校驗(yàn)位的檢驗(yàn),正確就對(duì)收到的數(shù)據(jù)進(jìn)行存儲(chǔ)處理功能,數(shù)據(jù)長度可以根據(jù)需要任意改變。由設(shè)置的波特率可以算出分頻系數(shù),具體算法為分頻系數(shù)X=CLK/(BOUND*2)。可由此式算出所需的任意波特率。下面是實(shí)現(xiàn)上述功能的VHDL源程序。

Library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity atel2_bin is

port( txclk: in std_logic; --2400Hz的波特率時(shí)鐘

reset: in std_logic; --復(fù)位信號(hào)

din: in std_logic_vector(15 downto 0); --發(fā)送的數(shù)據(jù)

start: in std_logic; --允許傳輸信號(hào)

sout: out std_logic --串行輸出端口

);

end atel2_bin;

architecture behav of atel2_bin is

signal thr,len: std_logic_vector(15 downto 0);

signal txcnt_r: std_logic_vector(2 downto 0);

signal sout1: std_logic;

signal cou: integer:=0;

signal oddb:std_logic;

type s is(start1,start2,shift1,shift2,odd1,odd2,stop1,stop2);

signal state:s:=start1;

begin

process(txclk)

begin

if rising_edge(txclk) then

if cou<3 then thr<="0000000001010101"; --發(fā)送的文件頭

elsif cou=3 then

thr<="0000000000000010"; --發(fā)送的文件長度

elsif (cou>3 and state=stop2) then thr<=din;--發(fā)送的數(shù)據(jù)

end if;

end if;

end procESS;

process(reset,txclk)

variable tsr,tsr1,oddb1,oddb2: std_logic_vector(7 downto 0);

begin

if reset='1' then

txcnt_r<=(others=>'0');

sout1<='1';

state<=start1;

cou<=0;

elsif txclk'event and txclk='1' then

case state is

when start1=>

if start='1' then

if cou=3 then

len<=thr;

end if;

tsr:=thr(7 downto 0);

oddb1:=thr(7 downto 0);

sout1<='0'; --起始位

txcnt_r<=(others=>'0');

state<=shift1;

else

state<=start1;

end if;

when shift1=>

oddb<=oddb1(7) xor oddb1(6) xor oddb1(5) xor oddb1(4) xor oddb1(3) xor oddb1(2) xor oddb1(1) xor oddb1(0);

sout1<=tsr(0); --數(shù)據(jù)位

tsr(6 downto 0):=tsr(7 downto 1);

tsr(7):='0';

txcnt_r<=txcnt_r+1;

if (txcnt_r=7) then

state<=odd1;cou<=cou+1;

end if;

when odd1=> --奇校驗(yàn)位

if ddb='1' then

sout1<='0';state<=stop1;

else

sout1<='1';state<=stop1;

end if;

when stop1=>

sout1<='1'; --停止位

if cou<4 then

state<=start1;

else

state<=start2;

end if;

when start2=>

tsr1:=thr(15 downto 8);

oddb2:=thr(15 downto 8);

sout1<='0'; --起始位

txcnt_r<=(others=>'0');

state<=shift2;

when shift2=>

oddb<=oddb2(7) xor oddb2(6) xor oddb2(5) xor oddb2(4) xor oddb2(3) xor oddb2(2) xor oddb2(1) xor oddb2(0);

sout1<=tsr1(0);--數(shù)據(jù)位

tsr1(6 downto 0):=tsr1(7 downto 1);

tsr1(7):='0';

txcnt_r<=txcnt_r+1;

if (txcnt_r=7) then

state<=odd2;

end if;

when odd2=> --奇校驗(yàn)位

if ddb='1' then

sout1<='0';state<=stop2;

else

sout1<='1';state<=stop2;

end if;

when stop2=>

sout1<='1'; --停止位

if len="0000000000000000" then

state<=stop2;

else

state<=start1;

len<=len-1;

end if;

end case;

end if;

end process;

sout<=sout1;

end behav;

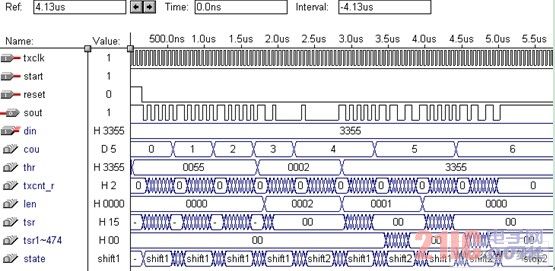

其中各信號(hào)的說明已在程序中標(biāo)明了。波形仿真圖如圖2所示。

圖2 FPGA數(shù)據(jù)發(fā)送時(shí)序仿真圖

圖中Din寫入值為3355H,波特率為2400Hz,Start信號(hào)始終置邏輯1,即隨時(shí)都能發(fā)送數(shù)據(jù)。Reset信號(hào)邏輯1時(shí)復(fù)位,邏輯0時(shí)電路開始工作。THR是數(shù)據(jù)寄存器,文件頭、數(shù)據(jù)長度以及數(shù)據(jù)位都先寄存到THR中,Len是數(shù)據(jù)長度,TSR是低8位數(shù)據(jù)幀寄存器,TSR1是高8位數(shù)據(jù)幀寄存器。數(shù)據(jù)長度Len定為02H,發(fā)送時(shí)先發(fā)送低8位55H,后發(fā)送高8位33H,一共發(fā)送兩遍。發(fā)送的數(shù)據(jù)格式說明:當(dāng)發(fā)送55H時(shí),其二進(jìn)制為01010101,則發(fā)送的數(shù)據(jù)的二進(jìn)制數(shù)為00101010111(1位開始位+8位數(shù)據(jù)位+1位奇校驗(yàn)位+1位停止位)。

單片機(jī)部分先對(duì)FPGA發(fā)送過來的文件頭進(jìn)行確認(rèn),正確就接收文件,否則放棄接收的數(shù)據(jù)。根據(jù)FPGA發(fā)送模塊的協(xié)議,對(duì)串口控制寄存器SCON和波特率控制寄存器PCON的設(shè)置即可實(shí)現(xiàn)。