頻率信號(hào)具有抗干擾性強(qiáng),易于傳輸,易于保持信息完整性和可以獲得較高測量精度等優(yōu)點(diǎn),被廣泛應(yīng)用于日常生活、工業(yè)等各個(gè)領(lǐng)域,頻率測量成為信息提取、設(shè)備檢測等過程中的一個(gè)重要環(huán)節(jié)。頻率檢測作為電子測量領(lǐng)域最基本的測量之一,隨著數(shù)字電子技術(shù)的發(fā)展而得到了長足的進(jìn)步,數(shù)字頻率測量也得到了越來越廣泛的應(yīng)用,從而使測頻原理和測頻方法的研究受到越來越多的關(guān)注。本文在簡述頻率測量原理和方法的基礎(chǔ)上,主要介紹一種基于PXI總線的寬帶、高精度數(shù)字頻率計(jì)的設(shè)計(jì)與實(shí)現(xiàn)。

1 測頻原理

目前對頻率的測量采用的方法主要有:圍繞電子計(jì)數(shù)器計(jì)一定時(shí)間內(nèi)的脈沖個(gè)數(shù)來確定頻率;對信號(hào)時(shí)頻變換的算法進(jìn)行研究。本文主要討論前者。

1.1 直接測頻法

電子計(jì)數(shù)器是一種利用比較法進(jìn)行測量的最常見、最基本的數(shù)字化儀器,是其他數(shù)字化儀器的基礎(chǔ)。頻率在時(shí)間軸上是無限延伸的,因此對頻率測量需要確定一個(gè)取樣時(shí)間T,在該時(shí)間內(nèi)對被測信號(hào)的周期進(jìn)行累加計(jì)數(shù)(若計(jì)數(shù)值為N),根據(jù)fx=N/T得到頻率值。此種方法由于閘門時(shí)間與被測信號(hào)不同步,計(jì)數(shù)時(shí)存在±1的計(jì)數(shù)誤差,影響測頻精度。

1.2 等精度測量法

可見直接測頻法雖然設(shè)計(jì)簡單,但是精度不高,為消除“±1計(jì)數(shù)誤差”,對其進(jìn)行改進(jìn)如圖1所示。

被測信號(hào)經(jīng)過濾波、放大、分頻、整形預(yù)處理之后,將處理后的方波信號(hào)和閘門時(shí)間預(yù)置方波信號(hào)進(jìn)行同步控制。同步控制一般由D觸發(fā)器和三態(tài)門來實(shí)現(xiàn)。在測頻率和周期時(shí),單片機(jī)控制中心發(fā)出清零信號(hào)使三態(tài)傳輸門處于高阻狀態(tài),同時(shí)給出啟動(dòng)閘門信號(hào),當(dāng)被測信號(hào)整形后的方波信號(hào)上升沿到來時(shí),同步控制發(fā)出信號(hào),使閘門A和閘門B同時(shí)開始對被測信號(hào)和標(biāo)準(zhǔn)信號(hào)進(jìn)行計(jì)數(shù)。當(dāng)單片機(jī)發(fā)出結(jié)束閘門信號(hào)后,fx的方波信號(hào)上升沿的到來,將使計(jì)數(shù)器停止計(jì)數(shù),并申請中斷服務(wù)。這樣便實(shí)現(xiàn)了閘門的啟閉與fx同步,再將中斷服務(wù)送來的數(shù)據(jù)送入運(yùn)算中心進(jìn)行處理,最后將結(jié)果送入顯示系統(tǒng),顯示測量結(jié)果。時(shí)序圖如圖2所示。

經(jīng)分析,誤差主要來自標(biāo)頻信號(hào)與閘門B不同步產(chǎn)生的“±1”誤差,為進(jìn)一步提高測頻精度,提出了基于相位重合的全同步測頻方法。

1.3 全同步測頻法

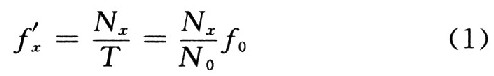

設(shè)開啟閘門時(shí)脈沖同步時(shí)間差為△t1,關(guān)閉閘門時(shí)脈沖同步時(shí)間差為△t2,脈沖的相位同步檢測最大誤差為△t,則有△t1≤△t,△t2≤△t。不計(jì)標(biāo)準(zhǔn)時(shí)鐘誤差,實(shí)際閘門與標(biāo)準(zhǔn)時(shí)鐘同步,實(shí)際閘門時(shí)間為T,被測信號(hào)計(jì)數(shù)值為Nx,標(biāo)準(zhǔn)時(shí)鐘計(jì)數(shù)值為No,則被測信號(hào)的頻率測量值為:

真實(shí)值為:

![]()

頻率測量的相對誤差為:

由式(3)可知,誤差只與脈沖相位檢測電路的準(zhǔn)確度有關(guān)。

2 硬件電路設(shè)計(jì)

2.1 信號(hào)調(diào)理電路設(shè)計(jì)

被測信號(hào)為1 Hz~6 GHz,頻帶范圍較寬,而CPLD/FPGA中計(jì)數(shù)器工作頻率不超過200MHz,因此需要對被測信號(hào)進(jìn)行預(yù)處理。該頻率計(jì)模塊包含 3個(gè)測試通道,分別為0,1,2通道。其中,O通道所測頻率范圍為1~6 GHz;1通道所測頻率范圍為50 MHz~1 GHz;2通道所測頻率范圍為1 Hz~50 MHz。對于0,1通道的信號(hào),由于頻率較高,因而先由高頻信號(hào)接收器進(jìn)行接收整形,然后經(jīng)前端分頻器分頻后送到FPGA/CP-LD進(jìn)行計(jì)數(shù);對于2通道所測的信號(hào)被放大整形后直接送到FPGA/CPLD計(jì)數(shù)。

2.2 器件選擇

由于該頻率計(jì)模塊分3個(gè)測試通道,對應(yīng)不同的測試通道,選用了相對應(yīng)的器件。在O通道,選用Zarlink公司的ZL40800和SP8782,實(shí)現(xiàn)8×32分頻;在1通道,選用SP8782實(shí)現(xiàn)32分頻;在2通道選用施密特觸發(fā)器對信號(hào)進(jìn)行放大整形。高穩(wěn)定度晶振選用TC75溫度補(bǔ)償晶振,其穩(wěn)定度為±10-8;FPGA選用Altera公司的EPM7032SLC44-5,其速度等級(jí)為5 ns,既滿足了該電路的要求,又兼顧了電磁兼容;高頻信號(hào)接收器采用NB6L16差分接收器,其接收的最高信號(hào)頻率可達(dá) 6 GHz。

2.3 PXI總線接口電路設(shè)計(jì)

專用PCI接口芯片加CPLD/FPGA的接口方案,采用專用接口芯片PCI9030雖沒有像直接采用CPLD/FPGA那么靈活,但它可以大大縮短開發(fā)周期,并且專用總線接口芯片具有通用性,提供配置寄存器,具備用于突發(fā)傳輸功能的片內(nèi)FIFO等優(yōu)點(diǎn),避免了自行設(shè)計(jì)PXI總線將大量的人力和物力投入到紛繁的邏輯驗(yàn)證、時(shí)序分析工作上,開發(fā)周期長的弊端。

2.4 基于FPGA的相位重合檢測電路設(shè)計(jì)

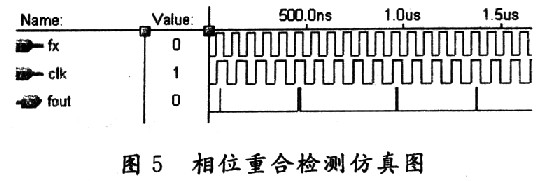

相位重合檢測電路基本原理:利用FPGA內(nèi)部的延時(shí)特性,信號(hào)經(jīng)過方向延時(shí)后和原信號(hào)相與,即可獲得與延時(shí)時(shí)間長度相同的輸出,且輸出間隔為各自的周期,當(dāng)兩路信號(hào)在第一次與門之后重合時(shí),y輸出高電平,此時(shí)判斷兩信號(hào)相位重合。EPM7032SLCA4-5的延時(shí)時(shí)間為5 ns。電路圖如圖4所示,時(shí)序圖如圖5所示。

3 基于PXI總線的寬帶頻率計(jì)設(shè)計(jì)

3.1 PXI總線介紹

PXI總線是在PCI總線內(nèi)核技術(shù)上增加了成熟的技術(shù)規(guī)范和要求形成的。它通過增加用于多板同步的觸發(fā)總線和參考時(shí)鐘(10 MHz),用于進(jìn)行精確定時(shí)的星型觸發(fā)縱向,以及用于相鄰模塊間高速通信的局部總線來滿足用戶試驗(yàn)和測量的要求。PXI將Windows 95和Windows NT定義為其標(biāo)準(zhǔn)軟件框架,并要求所有的儀器模塊都帶有按VISA規(guī)范編寫的WIN32設(shè)備驅(qū)動(dòng)程序,使PXI成為一種系統(tǒng)級(jí)的規(guī)范,確保系統(tǒng)易于集成和使用。

3.2 頻率計(jì)系統(tǒng)組成

被被測信號(hào)經(jīng)過調(diào)理電路預(yù)處理后與標(biāo)準(zhǔn)頻率一起輸出到相位檢測電路后,由總線控制打開預(yù)制閘門,當(dāng)檢測到相位重合時(shí),實(shí)際閘門開啟并計(jì)數(shù),當(dāng)預(yù)制閘門下降沿到來時(shí)并不立即停止計(jì)數(shù),而是等到下一次的脈沖重合點(diǎn)到來時(shí)關(guān)閉閘門并停止計(jì)數(shù),系統(tǒng)由PXI總線進(jìn)行控制。原理圖如圖6所示。

4 結(jié)語

介紹了一種基于PXI總線的高精度寬帶頻率計(jì),采用預(yù)分頻和相位同步測頻相結(jié)合的技術(shù),實(shí)現(xiàn)了寬帶范圍內(nèi)的高精度測頻要求,同時(shí),通過FPGA將關(guān)鍵電路部分以邏輯編程的方式集成在芯片中,易于修改,使用方便。整個(gè)系統(tǒng)由PXI總線進(jìn)行通信和控制,該頻率計(jì)在電子測量領(lǐng)域有著廣泛的應(yīng)用前景。