0 引言

傳真通信規(guī)程是將要掃描的電平信號(hào)值進(jìn)行A/D轉(zhuǎn)換,再經(jīng)過(guò)圖像二值化處理,,表示成連續(xù)交替黑白點(diǎn)的數(shù)據(jù)序列(I/O序列),,再對(duì)該數(shù)據(jù)序列進(jìn)行編碼后,調(diào)制發(fā)送,;接收端對(duì)收到的編碼數(shù)據(jù)信號(hào)解調(diào)后進(jìn)行譯碼,,最后由熱敏頭打印輸出。

在傳真通信中,,對(duì)傳真圖像數(shù)據(jù)進(jìn)行編碼和譯碼是傳真通信的關(guān)鍵技術(shù),。改進(jìn)的Huffman碼(MHC)是ITU—T.4向各國(guó)推薦的一維標(biāo)準(zhǔn)碼,主要應(yīng)用于三類(lèi)傳真機(jī)上,。MHC碼是一種常用的變長(zhǎng)碼,,其信源的消息與碼字之間的關(guān)系是一對(duì)一的,是信息保持型的壓縮方法,。雙網(wǎng)傳真系統(tǒng)完成與Internet和PSTN網(wǎng)絡(luò)的傳真通信,,采用嵌入式系統(tǒng)的設(shè)計(jì)思路劃分軟硬件。其中,,傳真協(xié)議采用軟件實(shí)現(xiàn),,傳真編譯碼和外圍設(shè)備控制器采用硬件實(shí)現(xiàn),以降低設(shè)計(jì)復(fù)雜度,,提高傳真效率,。

1 傳真機(jī)硬件系統(tǒng)模型

硬件電路模塊應(yīng)包括:CIS掃描電路模塊(A/D轉(zhuǎn)換)、編碼電路模塊(圖像二值化處理),、譯碼電路模塊,、打印電路模塊、步進(jìn)電機(jī)驅(qū)動(dòng)電路模塊及時(shí)鐘電路模塊。并以NiosⅡ軟核處理器,、CIS掃描器件,、步進(jìn)電機(jī)、TPH打印器件為硬件平臺(tái),,通過(guò)FPGA實(shí)現(xiàn)硬件電路模塊,。上層軟件通過(guò)讀寫(xiě)寄存器來(lái)控制外圍設(shè)備和編譯碼電路,完成編碼數(shù)據(jù)的讀取和譯碼數(shù)據(jù)的寫(xiě)入,。圖1給出了硬件系統(tǒng)功能模塊劃分邏輯圖,。

雙網(wǎng)傳真機(jī)的編譯碼電路設(shè)計(jì)與實(shí)現(xiàn)" height="115" src="http://files.chinaaet.com/images/20110713/39563ced-b7ae-4d8d-85bb-3bea94a8aa84.jpg" width="350" />

其中,時(shí)鐘電路用來(lái)產(chǎn)生掃描,、打印及步進(jìn)電機(jī)所需的時(shí)序信號(hào),;由時(shí)鐘電路產(chǎn)生的CIS時(shí)鐘周期為2.6μs,打印時(shí)鐘周期為4.96μs,,步進(jìn)電機(jī)時(shí)鐘周期為10ms,。數(shù)據(jù)地址讀寫(xiě)總線(xiàn)接口與NiosⅡ處理器直接交互各種控制命令及讀寫(xiě)數(shù)據(jù),產(chǎn)生外圍設(shè)備的工作使能信號(hào),,通過(guò)地址選通信號(hào),,完成各個(gè)模塊與NiosⅡ處理器之間數(shù)據(jù)的交互。

2 外圍設(shè)備控制單元

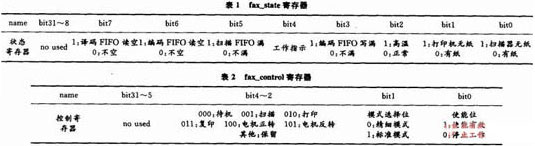

外圍設(shè)備的控制主要是通過(guò)對(duì)CIS掃描器件,、TPH打印器件和步進(jìn)電機(jī)發(fā)出相應(yīng)的控制時(shí)序信號(hào)完成掃描,、打印和步進(jìn)電機(jī)的驅(qū)動(dòng)等功能。該部分采用硬件實(shí)現(xiàn)可以產(chǎn)生超過(guò)定時(shí)中斷周期的更小周期的時(shí)序信號(hào)和時(shí)序要求精確的驅(qū)動(dòng)信號(hào),,同時(shí)可以通過(guò)配置控制寄存器,,對(duì)掃描和打印的功能進(jìn)行選擇,上層軟件通過(guò)狀態(tài)寄存器來(lái)判斷電路的工作狀態(tài),。表1和表2給出了寄存器的詳細(xì)描述,。

2.1 CIS掃描及A/D轉(zhuǎn)換

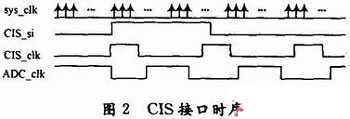

設(shè)計(jì)采用的CIS器件具有最高1.7MHz的掃描時(shí)鐘,且有效掃描寬度為216mm(A4紙的寬度),,每行有1728個(gè)掃描點(diǎn),。FPGA片內(nèi)的數(shù)字邏輯產(chǎn)生驅(qū)動(dòng)信號(hào)CIS_si和CIS_clk,并將模擬信號(hào)接入A/D轉(zhuǎn)換器的模擬輸入端口,,由FPGA片內(nèi)數(shù)字邏輯實(shí)時(shí)對(duì)A/D轉(zhuǎn)換器的輸出進(jìn)行采集,。圖2給出了CIS接口時(shí)序。其中,,CIS_si為行啟動(dòng)信號(hào),每行有1728個(gè)掃描點(diǎn),,每隔10ms啟動(dòng)一次CIS_si,。由于掃描最快能達(dá)到1.8ms/line,而打印最快只能達(dá)到10ms/line,所以?huà)呙柰瓿珊笄翌A(yù)留出步進(jìn)電機(jī)工作的時(shí)間,,這樣就能滿(mǎn)足該系統(tǒng)的要求,。CIS_clk為2.6μs的掃描時(shí)鐘,占空比為0.254,。ADC_clk為AD采樣時(shí)鐘,,周期與CIS_clk相同,占空比為0.046,。

A/D轉(zhuǎn)換的原理是通過(guò)CIS掃描器件把原稿的光信號(hào)轉(zhuǎn)化為電信號(hào),,將CIS掃描器件獲得的模擬電信號(hào)通過(guò)A/D轉(zhuǎn)換器件轉(zhuǎn)化為8b的數(shù)字信號(hào)在ADC_clk的下降沿送入掃描數(shù)據(jù)緩沖區(qū)。

2.2 步進(jìn)電機(jī)控制

在傳真機(jī)硬件系統(tǒng)中,,步進(jìn)電機(jī)的主要作用是根據(jù)當(dāng)前工作狀態(tài),,驅(qū)動(dòng)掃描或打印夾紙的滾軸。步進(jìn)電機(jī)的時(shí)鐘周期為10ms,,滿(mǎn)足系統(tǒng)要求,。掃描時(shí)步進(jìn)電機(jī)反轉(zhuǎn),打印時(shí)正轉(zhuǎn),。通過(guò)控制寄存器,,可以實(shí)現(xiàn)標(biāo)準(zhǔn)和精細(xì)兩種掃描模式。

2.3 打印器件

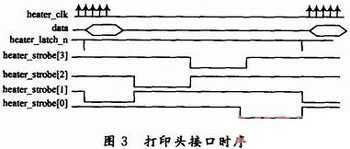

設(shè)計(jì)所用的熱敏打印器件系統(tǒng)采用SHECHA216-UH,,其接口時(shí)序如圖3所示(data表示數(shù)據(jù)在鎖存信號(hào)有效后輸出),。其中,heater_clk為打印頭時(shí)鐘,,1MHz,,50 %占空比;heater_latch_n為打印頭鎖存信號(hào),,低電平有效,,每隔10ms鎖存一次;heater_trobe[3:0]為打印頭加熱段選信號(hào),,在10ms內(nèi),,這四個(gè)信號(hào)依次低有效一次。

3 編碼電路單元設(shè)計(jì)

對(duì)一個(gè)二值傳真信源來(lái)說(shuō),,一副傳真圖像是由掃描線(xiàn)上的像素組成的,,而每一掃描線(xiàn)又總是由一些連續(xù)的黑像素和白像素組成,連續(xù)發(fā)生的黑像素為連‘1’,,白像素為連‘0’,,也稱(chēng)之為黑游程和白游程。連‘1’的個(gè)數(shù)稱(chēng)為黑游程長(zhǎng)度,,連‘0’的個(gè)數(shù)稱(chēng)為自游程長(zhǎng)度,。黑白游程總是交替出現(xiàn)的,。游程長(zhǎng)度就等于一條掃描線(xiàn)上的像素總數(shù),A4幅面一般為1728,。本項(xiàng)目使用的圖像二值化方法是固定閾值法,,即將A/D轉(zhuǎn)化后的8b數(shù)據(jù)和閾值做比較,得到‘0’或‘1’(白點(diǎn)或黑點(diǎn)),。當(dāng)總線(xiàn)地址為01H時(shí),,讀取32位編碼寄存器。

無(wú)失真的信源編碼方式中,,使用最多的是變長(zhǎng)碼,,其中最優(yōu)的編碼是Huffman碼,改進(jìn)的Huffman碼(MHC)是三類(lèi)傳真機(jī)信源編碼的標(biāo)準(zhǔn),。MHC所做的主要改進(jìn)是將碼字分為終止碼和形成碼,,能夠用較短的編碼來(lái)表示較長(zhǎng)的連續(xù)黑點(diǎn)或自點(diǎn)。0~63的游程長(zhǎng)度用終止碼表示,,64整數(shù)倍的游程長(zhǎng)度由形成碼表示,,任意游程長(zhǎng)度大于63的碼字表示為“形成碼+終止碼”。例如,,當(dāng)白游程長(zhǎng)度為131b(128+3)時(shí),,編碼表示為‘100101000’,即,,白游程長(zhǎng)度128b的形成碼‘10010’加上白游程長(zhǎng)度為3b的終止碼‘1000’,。行同步碼EOL的格式為‘0000000000 01’。WRLC為白游程長(zhǎng)度編碼,,BRLC為黑游程長(zhǎng)度編碼,。每一行的第一個(gè)游程長(zhǎng)度編碼為白碼字,黑白游程長(zhǎng)度碼字連續(xù)交替,。收到連續(xù)的六個(gè)EOL后表示該頁(yè)結(jié)束,。根據(jù)T.4的表述,一頁(yè)編碼后的傳真數(shù)據(jù)格式如表3所示,。

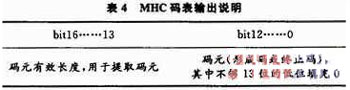

在構(gòu)建碼表時(shí),,構(gòu)建四個(gè)不同的碼表單元,即黑,、白游程形成碼碼元單元和黑,、白游程終止碼碼元單元。同時(shí)需要存儲(chǔ)黑白游程編碼碼元的長(zhǎng)度信息,。終止碼碼表的地址是按游程長(zhǎng)度編寫(xiě)的,,即0~63,而形成碼的碼表地址共有27個(gè),。這樣存儲(chǔ)可以通過(guò)黑白計(jì)數(shù)值直接找到地址,,碼表所存儲(chǔ)的信息為17位,,表4給出了MHC碼表的輸出說(shuō)明。

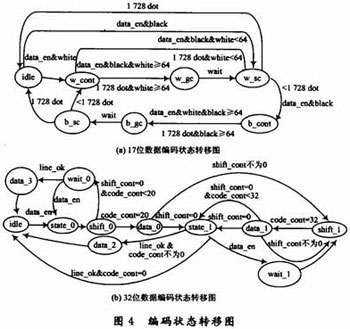

例如,,編碼得到的碼元信息是‘0111’,這是白游程2所代表的碼元,,則碼元的有效長(zhǎng)度為‘0100’(4位),,碼元信息為‘011100000000 0’(13位)。在碼元黑白屬性發(fā)生改變時(shí),,如果當(dāng)前游程的計(jì)數(shù)長(zhǎng)度小于64,,則取計(jì)數(shù)長(zhǎng)度的低6位為地址,查找對(duì)應(yīng)碼表(終止碼表)中的17位數(shù)據(jù),;如果游程長(zhǎng)度大于或等于64,,則取計(jì)數(shù)長(zhǎng)度的高5位為地址,查找對(duì)應(yīng)碼表(形成碼表)中的17位數(shù)據(jù),。NiosⅡ處理器進(jìn)行數(shù)據(jù)交換,,采用32位寄存器接口。每次查找完MHC碼表后,,采用二級(jí)編碼電路對(duì)一級(jí)編碼電路得到的信息再進(jìn)行一次編碼,,將17位編碼數(shù)據(jù)轉(zhuǎn)換成32位編碼數(shù)據(jù)。圖4給出了編碼狀態(tài)轉(zhuǎn)移圖,。

4 譯碼電路單元設(shè)計(jì)

對(duì)于MHC碼而言,,首先它是一個(gè)變長(zhǎng)碼,發(fā)送端在編碼時(shí)把游程長(zhǎng)度所對(duì)應(yīng)的碼元數(shù)據(jù)不留間隙的存入發(fā)送緩沖區(qū)中,,經(jīng)過(guò)調(diào)制載波后發(fā)送出去,。接收端解調(diào)出來(lái)的數(shù)據(jù),即編碼數(shù)據(jù),,譯碼時(shí)從該數(shù)據(jù)序列中分離出碼字,,由碼字去找出所對(duì)應(yīng)的游程長(zhǎng)度,輸出到打印緩沖區(qū),,就完成了譯碼過(guò)程,。要提高譯碼速度,可以采用多步合一的方法,,減少查找碼表的次數(shù),,也就是一次輸入多個(gè)碼元。根據(jù)碼表的特點(diǎn),,對(duì)白譯碼而言,,第一次可直接輸入4個(gè)碼元,對(duì)于黑譯碼,,第一次可輸入2個(gè)碼元,,隨后每次可輸入2個(gè)碼元或1個(gè)碼元,。

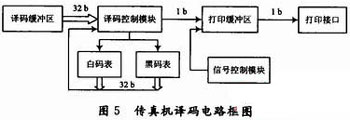

譯碼時(shí),通過(guò)Avalon總線(xiàn)接口將編碼數(shù)據(jù)寫(xiě)入一個(gè)32×256 b的緩沖區(qū),;譯碼完成后,,將數(shù)據(jù)送到打印緩沖區(qū),由信號(hào)控制模塊控制打印緩沖區(qū)的復(fù)位,、讀時(shí)鐘,、讀請(qǐng)求和打印頭時(shí)鐘信號(hào),打印緩沖區(qū)的大小為1×2 048 b,。當(dāng)寫(xiě)入個(gè)數(shù)記到1728時(shí),,就會(huì)進(jìn)行讀操作。如果出現(xiàn)誤碼,,寫(xiě)入個(gè)數(shù)超過(guò)1728時(shí),,F(xiàn)IFO清零,此時(shí)不進(jìn)行讀操作,,而是將誤碼的那行數(shù)據(jù)丟棄,,并加入一行白點(diǎn)(1728個(gè)‘0’)。傳真譯碼電路如圖5所示,。

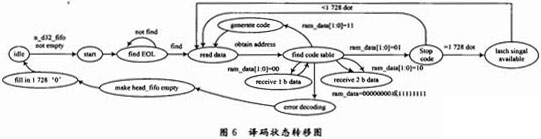

在譯碼電路中,,檢測(cè)到EOL后,將對(duì)譯碼緩沖區(qū)的數(shù)據(jù)交替地進(jìn)行白譯碼,、黑譯碼,、白譯碼操作。其中譯碼碼表的地址和數(shù)據(jù)寬度均為8b,。譯碼時(shí),,接收4b數(shù)據(jù)(白碼元),通過(guò)形成的8b地址來(lái)查找碼表并返回一個(gè)8b數(shù)據(jù)Ram_Data,,并根據(jù)此數(shù)據(jù)低2位的值來(lái)進(jìn)行下一步操作,。當(dāng)Ram_Data低2位為‘01’時(shí),輸出數(shù)據(jù)高6位的值,,此時(shí)終止碼使能有效,;當(dāng)Ram_Data低2位為‘11’時(shí),輸出數(shù)據(jù)高6位的值,,此時(shí)形成碼使能有效,;當(dāng)Ram_Data低2位為‘00’時(shí),表示接收1b數(shù)據(jù)和Ram_Data相加形成新地址,;當(dāng)Ram_Data低2位為‘10’時(shí),,表示接收2b數(shù)據(jù)和Ram_Data相加形成新地址;繼續(xù)查找碼表,,重復(fù)操作,,直到譯出碼元或出錯(cuò)為止,。查找黑白碼表不同的是:對(duì)于白譯碼而言,由于最短碼字長(zhǎng)度為4,,所以第一次可直接查找4b碼元,,隨之可查找2b或1b碼元;而對(duì)于黑譯碼而言,,由于最短的碼字長(zhǎng)度為2,,所以第一次查找2b碼元,隨之可查找2b或1b碼元,;輸出的6b數(shù)據(jù)為連續(xù)黑點(diǎn)或連續(xù)白點(diǎn)的個(gè)數(shù)。將譯碼后的數(shù)據(jù)存入1×2048 b的打印緩沖區(qū),,當(dāng)存儲(chǔ)數(shù)據(jù)滿(mǎn)一行時(shí),,輸出到打印頭打印,待清空后再進(jìn)行下一行的譯碼,。掃描到打印一行的時(shí)間要求是10ms,,所以譯碼完成后進(jìn)行等待,直到數(shù)據(jù)鎖存后再進(jìn)行下一行的譯碼,。譯碼狀態(tài)轉(zhuǎn)移圖如圖6所示,。

5 仿真驗(yàn)證與系統(tǒng)測(cè)試

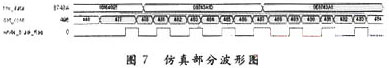

采用基于碼表遍歷的驗(yàn)證策略,對(duì)電路進(jìn)行仿真驗(yàn)證,,并查看輸出波形圖,,結(jié)果均與設(shè)計(jì)要求一致。仿真部分波形圖如圖7所示,。

其中,,fifo_data為編碼數(shù)據(jù);dot_cont為譯出的總點(diǎn)數(shù),;white_black_flag為黑白標(biāo)志位,,‘1’表示黑,‘0’表示白,。

該電路通過(guò)QuartusⅡ環(huán)境下的SOPC配置CPU核,,在Altera公司的FPGA開(kāi)發(fā)板上進(jìn)行下載,并在NiosⅡ開(kāi)發(fā)環(huán)境中使用軟件測(cè)試該電路,,通過(guò)寄存器驅(qū)動(dòng)電路工作,,經(jīng)過(guò)掃描,CPU核向電路寫(xiě)入編碼數(shù)據(jù),,待輸出標(biāo)識(shí)位有效后,,再讀出譯碼后數(shù)據(jù),通過(guò)傳真機(jī)打印出來(lái),。綜合結(jié)果表明電路可以工作在100MHz時(shí)鐘頻率下,。

將傳真標(biāo)準(zhǔn)樣張編碼數(shù)據(jù)送給譯碼模塊完成對(duì)譯碼電路的測(cè)試,,打印出的圖像滿(mǎn)足測(cè)試標(biāo)準(zhǔn)。然后將標(biāo)準(zhǔn)樣張?jiān)褰?jīng)過(guò)掃描編碼,,送給譯碼打印,,輸出打印結(jié)果與原稿比對(duì)。通過(guò)反復(fù)調(diào)試,,軟硬件運(yùn)行穩(wěn)定,,達(dá)到系統(tǒng)功能指標(biāo)。

6 結(jié)語(yǔ)

本文采用兩級(jí)編碼和快速譯碼的設(shè)計(jì)思路,,在FPGA芯片上實(shí)現(xiàn)了編譯碼電路和外設(shè)控制器,。上層軟件通過(guò)寄存器接口完成對(duì)硬件系統(tǒng)的控制,經(jīng)過(guò)仿真驗(yàn)證與測(cè)試,,電路對(duì)傳真數(shù)據(jù)正確編譯碼,,與軟件系統(tǒng)相配合為高性能的雙網(wǎng)傳真機(jī)提供了可靠的技術(shù)基礎(chǔ)。