關(guān)鍵字:AT25T1024 FLASH 高速SPI接口

在一些軍用芯片的早期設(shè)計(jì)中,一般先采用比較成熟的商用協(xié)議芯片進(jìn)行軍用化改造(通常做成板卡形式),而商用芯片的軍用化改造主要體現(xiàn)在確定性、實(shí)時(shí)性、穩(wěn)定性、安全性等問題上,所以一般需要在商用協(xié)議芯片的上層加入較多的控制功能。FPGA以其資源豐富,易于組織流水和并行處理等優(yōu)點(diǎn),為這種復(fù)雜控制提供了很好的選擇。而SPI在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,因此在基于FPGA的讀寫接口設(shè)計(jì)中,高速SPI是一種很好的選擇。

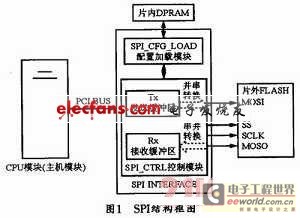

1 SPI結(jié)構(gòu)

SPI (Serial Peripheral Interface-串行外圍設(shè)備接口)是Motorola公司推出的一種高效率全雙工同步串行數(shù)據(jù)接口,以主從模式工作,廣泛應(yīng)用于FLASH,實(shí)時(shí)時(shí)鐘,AD轉(zhuǎn)換器等。SPI串行外圍設(shè)備總線根據(jù)串行同步時(shí)鐘極性(CPOL)和時(shí)鐘相位(CPHA)兩個(gè)參數(shù)的設(shè)置分為四種工作方式(SPO,SP1,SP2,SP3)。本板卡選用的片外存儲(chǔ)器AT25F1024僅支持0和3模式,為簡(jiǎn)化設(shè)計(jì),本設(shè)計(jì)的SPI時(shí)鐘采用SP0模式(CP-OL=0,CPHA=0),時(shí)鐘極性為低電平,時(shí)鐘相位串行時(shí)鐘上升沿采樣數(shù)據(jù),下降沿?cái)?shù)據(jù)輸出.SPI為主從工作方式,主設(shè)備由三部分構(gòu)成,SPI_CFG_LOAD配置加載模塊可自動(dòng)讀取存儲(chǔ)器FLASH的值,并加載到片內(nèi)DPRAM中。主機(jī)通過配置SPI_CTRL控制模塊相應(yīng)的寄存器,來完成對(duì)片外FLASH的訪問。SPI結(jié)構(gòu)框圖如圖1所示。

2 高速SPI接口設(shè)計(jì)

2.1 配置加載模塊的設(shè)計(jì)

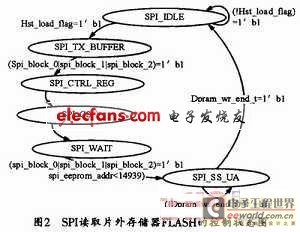

SPI_CFG_LOAD配置加載模塊主要完成從片外FLASH讀取數(shù)據(jù),并將數(shù)據(jù)存入片內(nèi)DPRAM中的功能。圖2給出了對(duì)應(yīng)的狀態(tài)機(jī)設(shè)計(jì)。

各狀態(tài)說明如下:

SPI_IDLE:空閑狀態(tài),如果主機(jī)配置了寄存器SPICFGSTART,狀態(tài)就跳到SPI_TX_BUFFER狀態(tài)。

SPI_TX_BUFFER:在此狀態(tài)主要向SPI_CTRL模塊的發(fā)送緩沖區(qū)地址0填入8位讀命令及讀取數(shù)據(jù)的三字節(jié)起始地址,狀態(tài)機(jī)之間進(jìn)入下一狀態(tài)。

SPI_CTRL_REG:在這一狀態(tài),配置SPI_CTRL模塊CTRL寄存器的值,包括一次讀操作搬運(yùn)的數(shù)據(jù)位數(shù),數(shù)據(jù)加載方式。如果配置GO位為“1”,表明可以開始進(jìn)行讀傳輸,進(jìn)入下一狀態(tài)SPI_CS。

SPI_CS:配置SPI_CTRL)模塊寄存器SS位的值,以選擇傳輸數(shù)據(jù)的從設(shè)備。

SPI_WAIT:本狀態(tài)判斷讀操作的起始地址和終止地址是否在要求的范圍內(nèi),如果處于相應(yīng)的范圍,地址自動(dòng)加64后,狀態(tài)機(jī)進(jìn)入SPI_SS_ UA狀態(tài)。

SPI_SS_UA:等待片內(nèi)DPRAM的寫操作完成,如果DPRAM_WR_END_T信號(hào)為高,說明當(dāng)前的傳輸操作已經(jīng)結(jié)束,可以進(jìn)入下一次的訪問,狀態(tài)機(jī)進(jìn)入SPI_IDLE狀態(tài)。

關(guān)鍵字:AT25T1024 FLASH 高速SPI接口

2.2 控制模塊的設(shè)計(jì)

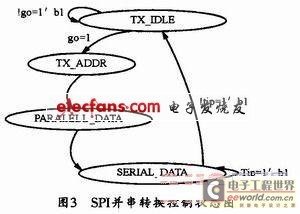

SPI_CTRL控制模塊可將發(fā)送緩沖區(qū)0的數(shù)據(jù)讀出來,經(jīng)過并串轉(zhuǎn)換,發(fā)送到串行線SI上,并且控制從串行線SO上接收數(shù)據(jù),存儲(chǔ)在接收緩沖區(qū),并行數(shù)據(jù)轉(zhuǎn)換成串行輸出由并串轉(zhuǎn)換狀態(tài)機(jī)來控制實(shí)現(xiàn),見圖3。

各狀態(tài)含義如下:

TX_IDLE:等待主機(jī)設(shè)置控制寄存器的GO位,如果置“1”,表示準(zhǔn)備開始傳輸,跳入下一狀態(tài)TX_ADDR。

TX_ADDR:當(dāng)傳輸長(zhǎng)度小于等于32位時(shí),跳入下一狀態(tài)PARALELL_DATA。

PARALELL_DATA:如果GO為1,在此狀態(tài)TIP將被置“1”,說明傳輸開始,傳輸?shù)挠?jì)數(shù)器開始計(jì)數(shù)。

SERIAL_DATA:并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù)發(fā)送出去,當(dāng)CNT_SHIFT計(jì)數(shù)器減到0時(shí),傳輸結(jié)束,狀態(tài)跳入TX_IDLE。

2.3 串行移位時(shí)鐘設(shè)計(jì)

SPI串行線上的主從設(shè)備必須根據(jù)具體要求設(shè)置匹配的傳輸時(shí)序模式,時(shí)序只有匹配,數(shù)據(jù)傳輸才能正常進(jìn)行。如果設(shè)置的不匹配,可能導(dǎo)致數(shù)據(jù)接收方和發(fā)送方在同一時(shí)鐘沿作用,而使數(shù)據(jù)傳輸失敗。本設(shè)計(jì)中的時(shí)鐘僅支持SP0模式,即串行時(shí)鐘處于空閑電平時(shí),空閑狀態(tài)時(shí)鐘的極性電平為低,在時(shí)鐘的前沿采樣數(shù)據(jù),時(shí)鐘后沿串行線上數(shù)據(jù)變化。

在采樣時(shí)刻,線上數(shù)據(jù)必須已經(jīng)穩(wěn)定可靠,因此數(shù)據(jù)發(fā)送端設(shè)備應(yīng)提前將數(shù)據(jù)移出到數(shù)據(jù)線上,本SPI接口電路設(shè)計(jì)在同一串行移位時(shí)鐘周期中的前一個(gè)時(shí)鐘沿(即相反時(shí)鐘變化方向)將數(shù)據(jù)移出,移位時(shí)鐘設(shè)計(jì)為系統(tǒng)時(shí)鐘的兩分頻,為40/2MHz。

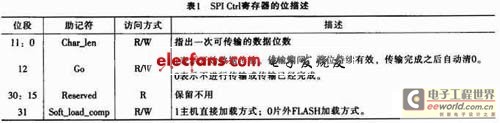

2.4 SPI相關(guān)寄存器描述

在本設(shè)計(jì)中,共有四種32位寄存器,包括控制寄存器,從設(shè)備選擇寄存器,加載配置數(shù)據(jù)起始寄存器以及加載配置數(shù)據(jù)完成寄存器。

控制寄存器用來控制配置信息加載方式,即:片外FLASH加載方式或主機(jī)直接加載方式。當(dāng)選擇片外FLASH加載方式時(shí),控制寄存器還用來控制一次數(shù)據(jù)傳輸?shù)拈L(zhǎng)度。CTRL寄存器的具體描述見表1。

從設(shè)備選擇寄存器的SS位置“1”時(shí),表示選中從設(shè)備。置“0”表示不選擇任何從設(shè)備,本設(shè)計(jì)僅支持一個(gè)從設(shè)備。

加載配置數(shù)據(jù)起始寄存器的SPICFGSTART位置“1”時(shí),配置數(shù)據(jù)自動(dòng)從FLASH中讀取并寫入到DPRAM中,置“0”不進(jìn)行讀FLASH操作。

加載配置數(shù)據(jù)完成寄存器為只讀寄存器,用來判斷數(shù)據(jù)是否已經(jīng)加載完成。

2.5 SPI緩沖區(qū)設(shè)計(jì)

圖4所示為主機(jī)可直接訪問的SPI接口內(nèi)部DPRAM發(fā)送和接收數(shù)據(jù)緩沖區(qū)。

SPI發(fā)送數(shù)據(jù)緩沖區(qū)深度65,數(shù)據(jù)位寬32位,其中地址22’h 3e0600存放訪問AT25F1024存儲(chǔ)器的指令,當(dāng)進(jìn)行寫操作時(shí),從數(shù)據(jù)發(fā)送緩沖區(qū)最低位地址22’h3e0604開始,將數(shù)據(jù)搬運(yùn)出來,串行發(fā)送到AT25F1024存儲(chǔ)器。

SPI接收數(shù)據(jù)緩沖區(qū)深度65,數(shù)據(jù)位寬32位,其中地址22’h3e0400緩存讀取的AT25F1024配置和狀態(tài)信息,偏移地址22’h3e0404~22’ h3e0500緩存指定FLASH讀取的總線配置數(shù)據(jù)數(shù)據(jù),最大緩存2048位。

3 數(shù)據(jù)搬運(yùn)時(shí)間

3.1 主機(jī)寫片外FLASH的時(shí)間

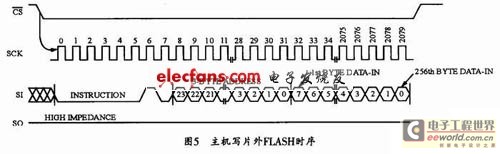

本設(shè)計(jì)使用的存儲(chǔ)器AT25F1024緩沖數(shù)據(jù)寄存器大小2048位,寫使能需要8個(gè)串行時(shí)鐘周期,向片外FLASH傳輸2048位數(shù)據(jù)需要2080個(gè)串行時(shí)鐘周期(包括了32位寫指令的傳輸數(shù)據(jù)),這樣寫一次需要時(shí)間為2088個(gè)時(shí)鐘周期,主機(jī)將1Mbits的FLASH填滿,時(shí)間大約為2088 x50ns(串行時(shí)鐘40/2MHz)×512 (填滿1Mbits需要512次寫操作)=53.4ms。讀1Mbits的FLASH需要的時(shí)間約為2080x50x512=53.2ms。圖5所示為主機(jī)寫片外FLASH時(shí)序圖。

3.2 讀取數(shù)據(jù)并加載到片內(nèi)DPRAM的時(shí)間

通過SO管腳讀取AT25F1024的過程按下面順序執(zhí)行,當(dāng)片選拉低選擇此器件之后,通過SI線發(fā)送讀指令,后面跟隨要讀的地址(三個(gè)字節(jié)地址),指令傳輸完之后,SI線上的任何數(shù)據(jù)將被忽略。指定地址的數(shù)據(jù)接著被移出到SO線上。如果僅讀取一個(gè)字節(jié),當(dāng)數(shù)據(jù)讀出來之后,CS信號(hào)驅(qū)動(dòng)為高。讀指令繼續(xù)時(shí),字節(jié)地址自動(dòng)增加,并且數(shù)據(jù)不斷被搬運(yùn)出來。

AT25F1024緩沖數(shù)據(jù)寄存器大小2048位,在本設(shè)計(jì)中,寫使能需要32個(gè)串行時(shí)鐘周期,這樣讀取一次需要時(shí)間為2080個(gè)時(shí)鐘周期,將片內(nèi)DPRAM(DPRAM大小14940字節(jié))填滿,時(shí)間大約為2080x50ns(串行時(shí)鐘40/2MHZ)x59(填滿片內(nèi)DPRAM需要大約59次讀操作)=6.13ms。

4 結(jié)束語

本文從應(yīng)用的實(shí)際需求出發(fā),在FPGA中實(shí)現(xiàn)了對(duì)外部FLASH進(jìn)行讀寫的高速SPI接口,并已在某型板卡中成功應(yīng)用。本文重點(diǎn)用有限狀態(tài)機(jī)的形式對(duì)各部分的工作原理和實(shí)現(xiàn)方法進(jìn)行了描述。在FPGA資源比較緊張,限制管腳的使用數(shù)目,對(duì)速率又有比較高的需求的情況下,利用此SPI接口進(jìn)行數(shù)據(jù)的加載或者固化,具有很高的應(yīng)用價(jià)值。