隨著主流市場即將演進到SuperSpeed USB,許多設計團隊正力圖加快設計認證。本文將為您提供專家建議參考,幫助您輕松完成這一過程。

盡管市場上已經(jīng)出現(xiàn)了早期的USB 3.0產(chǎn)品,但主流市場轉向Super Speed USB 還有待時日。部分原因在于,USB 2.0接口無所不在,且生產(chǎn)成本低廉。高帶寬設備(如攝像機和存儲設備)已經(jīng)率先演進到SuperSpeed USB。但就目前而言,基于成本因素考慮,USB3.0實施仍限于較高端的產(chǎn)品。

大規(guī)模部署任何新的行業(yè)標準(包括USB3.0)都存在內(nèi)在挑戰(zhàn)。此外,USB2.0到USB 3.0并非簡單的跳躍,其性能提高了十倍之多。盡管性能得到大幅度提升,但消費者對低成本互連設備的預期并沒有改變。這就給工程師們帶來了明顯的壓力,需要在一個原本速度很低的信號通道上傳輸高速率信號,同時要在各種條件下保證可靠性、互操作能力和高性能。為保證物理層(PHY)一致性和認證,測試變得空前關鍵或重要。

USB 3.0擁有許多其它高速串行技術(如PCI Express和串行ATA)共有的特點:8b/10b編碼,明顯的通道衰減,擴頻時鐘。本文將介紹一致性測試方法及怎樣對發(fā)射機、接收機及線纜和互連進行最精確的、可重復的測量。在掌握了這些竅門之后,您便可以更有效地準備SuperSpeed PIL(Platform Integration Lab)之行了。

High Speed Vs. SuperSpeed

USB 3.0滿足了市場對于更高帶寬下實時體驗應用的需求。目前USB設備達數(shù)十億,因而USB 3.0也提供了向下兼容能力,支持傳統(tǒng)USB 2.0設備。然而,USB 2.0和3.0在物理層有多種差異 (表1)。

表1. USB 2.0 和 SuperSpeed USB物理層區(qū)別

SuperSpeed USB一致性測試已經(jīng)有明顯變化,以適應更高速接口帶來的新挑戰(zhàn)。USB 2.0接收機驗證需要執(zhí)行接收機靈敏度測試。USB 2.0設備必須對150 mV及以上的測試包做出響應,并且忽略100 mV以下的信號。

SuperSpeed USB接收機必須面對更多的信號損傷,因此測試要求要比USB 2.0更加苛刻。設計人員還必須考慮傳輸線效應,在發(fā)射機中使用均衡技術(包括去加重),在接收機中使用連續(xù)時間線性均衡技術(CTLE)。此外,現(xiàn)在還要求在接收機上進行抖動容限測試,使用擴頻時鐘(SSC)和異步參考時鐘可能會導致互操作能力問題。

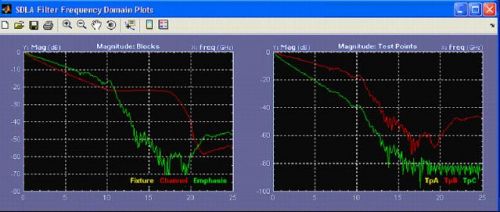

評估USB 3.0串行數(shù)據(jù)鏈路另一個重要部分是被測波形與互連通道的聯(lián)系非常復雜。不能再認為只要發(fā)射機輸出滿足了眼圖模板,電路就一定能在傳輸損耗滿足要求的通道中正常工作。想了解發(fā)射機余量一定時的最差的傳輸通道,您需要在一致性測試要求以外建立通道和線纜組合模型,使用通道建模軟件,分析通道效應 (圖1)。

圖1. 軟件工具,可以針對參考測試通道分析USB 3.0 通道效應。

隨著主流市場即將演進到SuperSpeed USB,許多設計團隊正力圖加快設計認證。本文將為您提供專家建議參考,幫助您輕松完成這一過程。

盡管市場上已經(jīng)出現(xiàn)了早期的USB 3.0產(chǎn)品,但主流市場轉向Super Speed USB 還有待時日。部分原因在于,USB 2.0接口無所不在,且生產(chǎn)成本低廉。高帶寬設備(如攝像機和存儲設備)已經(jīng)率先演進到SuperSpeed USB。但就目前而言,基于成本因素考慮,USB3.0實施仍限于較高端的產(chǎn)品。

大規(guī)模部署任何新的行業(yè)標準(包括USB3.0)都存在內(nèi)在挑戰(zhàn)。此外,USB2.0到USB 3.0并非簡單的跳躍,其性能提高了十倍之多。盡管性能得到大幅度提升,但消費者對低成本互連設備的預期并沒有改變。這就給工程師們帶來了明顯的壓力,需要在一個原本速度很低的信號通道上傳輸高速率信號,同時要在各種條件下保證可靠性、互操作能力和高性能。為保證物理層(PHY)一致性和認證,測試變得空前關鍵或重要。

USB 3.0擁有許多其它高速串行技術(如PCI Express和串行ATA)共有的特點:8b/10b編碼,明顯的通道衰減,擴頻時鐘。本文將介紹一致性測試方法及怎樣對發(fā)射機、接收機及線纜和互連進行最精確的、可重復的測量。在掌握了這些竅門之后,您便可以更有效地準備SuperSpeed PIL(Platform Integration Lab)之行了。

High Speed Vs. SuperSpeed

USB 3.0滿足了市場對于更高帶寬下實時體驗應用的需求。目前USB設備達數(shù)十億,因而USB 3.0也提供了向下兼容能力,支持傳統(tǒng)USB 2.0設備。然而,USB 2.0和3.0在物理層有多種差異 (表1)。

表1. USB 2.0 和 SuperSpeed USB物理層區(qū)別

SuperSpeed USB一致性測試已經(jīng)有明顯變化,以適應更高速接口帶來的新挑戰(zhàn)。USB 2.0接收機驗證需要執(zhí)行接收機靈敏度測試。USB 2.0設備必須對150 mV及以上的測試包做出響應,并且忽略100 mV以下的信號。

SuperSpeed USB接收機必須面對更多的信號損傷,因此測試要求要比USB 2.0更加苛刻。設計人員還必須考慮傳輸線效應,在發(fā)射機中使用均衡技術(包括去加重),在接收機中使用連續(xù)時間線性均衡技術(CTLE)。此外,現(xiàn)在還要求在接收機上進行抖動容限測試,使用擴頻時鐘(SSC)和異步參考時鐘可能會導致互操作能力問題。

評估USB 3.0串行數(shù)據(jù)鏈路另一個重要部分是被測波形與互連通道的聯(lián)系非常復雜。不能再認為只要發(fā)射機輸出滿足了眼圖模板,電路就一定能在傳輸損耗滿足要求的通道中正常工作。想了解發(fā)射機余量一定時的最差的傳輸通道,您需要在一致性測試要求以外建立通道和線纜組合模型,使用通道建模軟件,分析通道效應 (圖1)。

圖1. 軟件工具,可以針對參考測試通道分析USB 3.0 通道效應。

發(fā)射機一致性測試

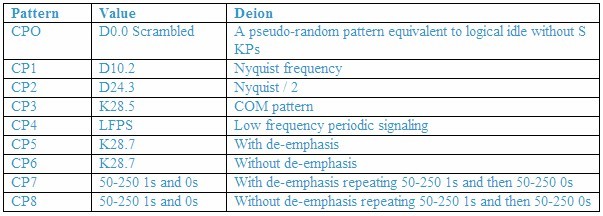

通過使用各種測試碼型以幫助進行發(fā)射機測試 (表2)。每種碼型都是根據(jù)與評估碼型的測試有關的特點而選擇的。CP0(一種D0.0加擾序列)用來測量確定性抖動(Dj),如數(shù)據(jù)相關抖動(DDJ)。CP1(一種未加擾D10.2全速率時鐘碼型)不生成DDJ,因此更適合評估隨機性抖動(RJ)。

表2. SuperSpeed USB 發(fā)送端一致性測試碼型

抖動和眼高的測量是通過對100萬個連續(xù)比特(UI)進行分析而得到,需要使用均衡器功能和適當?shù)臅r鐘恢復設置(二階鎖相環(huán)、或稱為PLL,10 Mhz環(huán)路帶寬,0.707的阻尼系數(shù))。通過分析被測數(shù)據(jù)樣本,可以外推出10-12誤碼率(BER)下的抖動值。例如,通過外推算法,把測得的RJ (rms)乘以14.069,可以得到10-12誤碼率下RJ(PK-PK)。

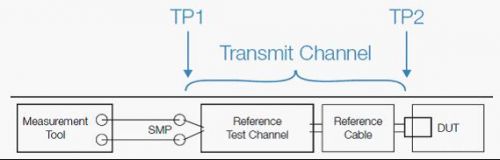

圖2. 標準化發(fā)射機一致性測試設置,包括參考測試通道和線纜。測試點2 (TP2)距被測器件(DUT)最近,測試點1 (TP1)是遠端測量點。

在TP1采集信號后,可以使用SigTest軟件處理數(shù)據(jù),這與PCI Express官方的一致性測試方法類似。對需要預測試一致性、檢定或調(diào)試的應用,希望可以進一步了解電路在各種條件或參數(shù)下的特點。裝有USB 3.0分析軟件的高帶寬示波器提供了Normative和Informative方式的物理層發(fā)射端自動測量。省掉了手動配置的步驟,大大節(jié)約了測量時間。

在測試完成后,詳細的Pass/Fail測試報告標記出哪里可能發(fā)生設計問題。如果在不同測試地點(如公司實驗室、測試中心)結果不一致,可以使用之前測試時保存的波形數(shù)據(jù)重新分析(離線測量)。

如果要求更多的分析,可以使用抖動分析和眼圖分析軟件,調(diào)試和檢定電路。例如,可以一次顯示多個眼圖,允許工程師分析不同時鐘恢復設置或軟件通道模型的影響。此外,可以使用不同的濾波器,分析SSC的影響,解決系統(tǒng)互操作能力問題。

均衡考慮因素

由于明顯的通道衰減,SuperSpeed USB要求某種形式的補償,張開接收機上的眼圖。發(fā)射機上采用均衡技術,其采用去加重的形式。規(guī)定的標稱去加重比是3.5 dB,用線性單位表示為1.5倍。例如,在跳變比特電平為150 mVp-p時,非跳變比特電平為100 mVp-p。

CTLE標準均衡實現(xiàn)方案包括片內(nèi)技術、有源接收機均衡或無源高頻濾波器,如線纜均衡器上使用的濾波器。這一模型特別適合一致性測試,因為它非常簡便地描述了傳輸函數(shù)。CTLE通過頻域中的一系列極點和零點,在特定頻率上達到峰值(Peak)。

CTLE實現(xiàn)方案的設計要比其它技術簡單,能耗要低于其它技術。然而,在某些情況下,由于適應性、精度和噪聲放大方面的限制,僅僅使用CTLE實現(xiàn)方案可能是不夠的。其它技術包括前向反饋均衡(FFE)和判定反饋均衡(DFE),通過對數(shù)據(jù)樣點加權一些補償系數(shù)來補償通道損耗。

CTLE和FFE是線性均衡器。因此,這兩種技術都會提升高頻噪聲,而產(chǎn)生信噪比劣化。但是,DFE在反饋環(huán)路中使用非線性元器件,使噪聲的放大達到最小,補償碼間干擾(ISI)。圖3示例了一個經(jīng)過傳輸通道明顯衰減的5Gbps 信號,和使用去加重、CLTE和DFE均衡技術處理之后的信號。

圖3. 去加重(藍色)、長通道(白色)、CTLE (紅色)和三階DFE (灰色)對5-Gbit/s信號(黃色)產(chǎn)生的不同效果。