在便攜式傳感器、4至20mA控制回路或具有模數轉換器(ADC" title="ADC">ADC)的其他系統(tǒng)設計中,功耗越低,意味著電池續(xù)航" title="電池續(xù)航">電池續(xù)航時間越長,控制系統(tǒng)功能越強。在選擇滿足應用的功率" title="功率">功率預算的ADC時,可使用多種技術和折衷方案。

降低功耗" title="低功耗">低功耗最明顯的方法是采用電源電壓較低的ADC。如今的ADC可以采用3、2.5甚至1.8V的模擬和數字電源供電,5至3V的電壓降可以實現40%的即時省電。

降低數字電源電壓會引起兩個不利因素:ADC上需要一個獨立的數字電源引腳,并且數字輸出端可能出現較低的驅動電流。通過降低模塊電源電壓來降低功耗時,主要問題是信噪比(SNR)較低。不過現在的低噪聲處理技術和設計技巧可以確保現在的低壓ADC的SNR與模擬電源電壓較高的大功率ADC相同。

要對電源進行優(yōu)化,除了模擬電源電壓之外,研究模擬前端的其它部分也非常重要。傳統(tǒng)的傳感器和模擬輸入前端需要0至5V甚至10V的輸入范圍,以便實現最高的動態(tài)性能或者直接連接至傳感器。過去,降低電源電壓會減小ADC的動態(tài)范圍。假定傳感器輸出保持在5或10V的水平不變,那么信號必須進行衰減才能與ADC的輸入范圍匹配。

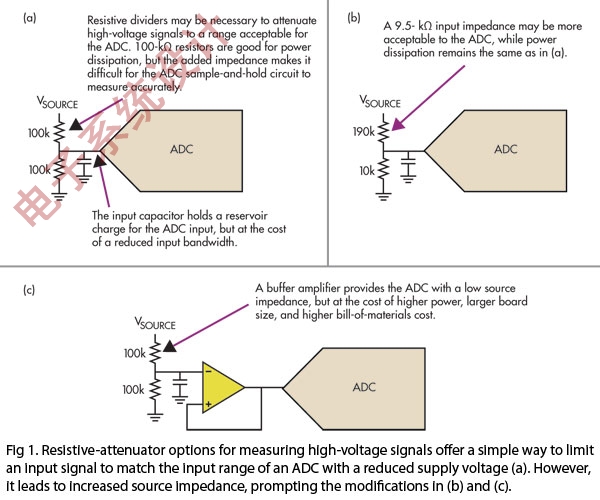

在傳感器與地之間增加一個電阻分壓器就能方便地實現這種信號衰減。大電阻值可用來限制功耗(圖1a)。不過,ADC一般需要較低的源阻抗,而這個采用電阻衰減器的方法需要實現低功耗,這兩種需求是相互沖突的。

圖1:用于測量高電壓信號的電阻衰減器可以提供一種限制輸入信號的簡單方法,以使ADC的輸入范圍與較低的電源電壓相匹配(a)。但是這會導致源阻抗增加,從而需要進行(b)和(c)中的修改。

另一個方案是增加電源與ADC輸入端之間的電阻值,以及減小ADC輸入端與地之間的電阻值(圖1b)。這樣的更改可以將ADC的有效阻抗從50 kΩ降低到9.5 kΩ,但同時也會減小ADC的輸入范圍。假定采用10V的電源,0至5V的輸入范圍會縮小至0至0.5V。

在圖1a和1b中,在電阻分壓器與ADC輸入端之間增加一個接地的旁路電容器可以將源阻抗與ADC輸入端的阻抗隔離。這樣的旁路電容可在ADC信號采集階段迅速將電荷傳輸到采樣電容器中。遺憾的是,此旁路電容器也限制了輸入信號的帶寬。

因此,第三個方案是在電阻分壓器與ADC之間增加一個緩沖放大器(圖1c) 。當然,緩沖器和其它放大器/濾波器信號調理級會增加功耗。

相反,如果傳感器輸出較小的話,減小模擬電源電壓和輸入范圍就不存在什么問題。傳感器系統(tǒng)中常用的惠斯登電阻電橋(Wheatstone-bridge)網絡就是這樣一個例子。每加1V的傳感器激勵電壓時,它即可提供2mV的滿量程輸出擺幅(典型值)。

在該裝置中,ADC測量的傳感器輸出滿量程范圍僅為5至10mV。此外,與高分辨率、低噪聲基底和出色的總動態(tài)范圍等其它參數相比,ADC所減小的輸入范圍的影響不大。

突發(fā)模式" title="突發(fā)模式">突發(fā)模式處理

對功耗要求較高的ADC設計的另一個技巧是“突發(fā)模式處理”。ADC先上電進行轉換快速突發(fā),然后掉電進入低功耗休眠模式。

這種工作模式非常適合具有快速微控制器或FPGA以及每秒至少能夠產生數千安培電流的ADC的應用。掉電時,ADC電源的電流可以降到幾微安或更低。這樣,平均功耗就會顯著低于ADC最快采樣率時的功耗。

突發(fā)模式處理充分利用了ADC能夠以低于其最高采樣率的有效速率循環(huán)開關的能力。幾乎所有的ADC數據手冊都會規(guī)定最高采樣率(也稱為輸出速率或吞吐率)下的功耗。

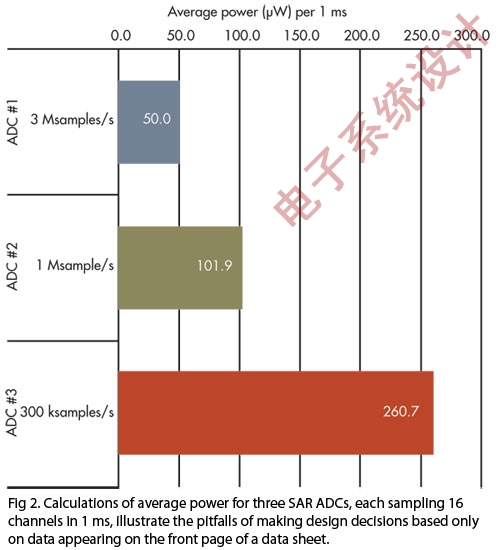

三個類似的集成多工器的ADC可以在1ms的時間內測量16個模擬輸入,有效采樣率均為1ksample/s(圖2) 。在最高采樣率下,ADC #1在3Msamples/s的采樣率下消耗的功率為8.3mW,ADC #2在1Msamples/s的采樣率下消耗的功率為6.0mW,ADC #3在300ksamples/s的采樣率下消耗的功率為4.7mW。

圖2:三個SAR ADC可以在1ms的時間內測量16個模擬輸入。

只看數據手冊首頁時,功耗最差的似乎是3Msample/s ADC。但是進一步研究其有功功率、關斷(或待機)功率和有效的采樣率之后,很明顯,選擇采樣率較高的ADC實際上更為合適。

對于ADC #1而言,8.3mW的有功功率部分所對應的有功時間僅為5.3s(每次轉換333ns,16次轉換),其6W的待機/關斷功率所對應的關斷時間為1ms的剩余部分(994.7s)。其平均功率為[(有功功率×有功時間) + (關斷功率×關斷時間)]/總周期時間,這個公式可以得出有效吞吐率為1ksample/s,平均功率為50W。

ADC #2與ADC #1類似,但是ADC #2的最高采樣率為1Msample/s。有功功率為6mW,有功時間為16s(每次轉換1s),關斷功率為6W,關斷時間為984s,從而得出其平均功率為ADC #1的平均功率的兩倍。

ADC #3采用低速內核,其最高采樣率為300ksample/s。功耗只有4.65mW,但是16次采樣轉換的時間為53s(比ADC #1長10倍),關斷功率為15W,關斷時間為947s。因此,ADC #3的平均功率為260.7W,比ADC #1的平均功率高5倍。

突發(fā)模式處理的一個潛在不足是可能需要具有更快時鐘速率的微控制器或FPGA。另一個不足是需要關斷和開啟電壓參考。如果ADC有內部基準,則需要一段時間(一般》100 s)上電和穩(wěn)定,然后ADC才能提供其有保證的線性度規(guī)格。

對于以突發(fā)模式工作且ADC外接一個電壓參考的應用,該基準源可以隨時上電。這種電壓參考僅耗費極小的功率,例如MAX6029的串聯型電壓參考,僅消耗5.25A(最大值)的功率。預置電壓輸出包含2.048、2.5、3、3.3、4.096和5V。這些基準電壓幾乎與所有的ADC都能很好地匹配。例如,2.048V的基準電壓僅需要15.75W的額外平均功率。

較低的采樣率

大多數ADC數據手冊都指定了兩種情況下的電源電流:最高采樣率和斷電模式。了解這些數據點很有好處,但是許多系統(tǒng)都是在低于最高采樣率的情況下運行ADC。此時,研究電源電壓如何隨采樣率變化很有幫助。

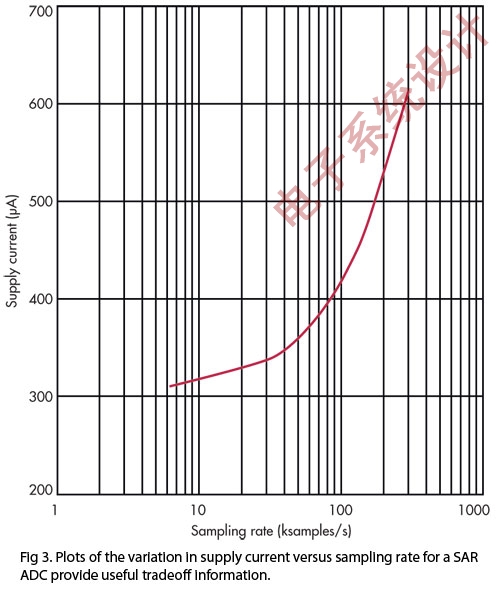

讓我們研究一下圖2中300ksample/s ADC采用3V電源供電(圖3)時的電源電流與采樣率關系圖。采樣率為300ksamples/s時的功耗為3V×0.62mA = 1.86mW,但采樣率為100ksamples/s時僅為1.26mW,可以節(jié)省32%的功率。

SAR ADC通過在轉換時上電并在轉換之間掉電,可以在較低的采樣率下大幅節(jié)能。大多數SAR ADC都有差不多的功耗,但是如果有些內部電路在轉換之間保持有源工作狀態(tài),節(jié)能幅度就可能不那么顯著。在任何情況下,最好都查看一下SAR ADC數據手冊上的典型電源電流與采樣率的曲線。

SAR ADC與ΔΣ ADC

較低的電源電流和采樣率是SAR ADC獨有的特性。主要用于精密應用的其它類型的ADC是ΔΣ ADC。這種ADC在較低的輸出速率下通常不能實現節(jié)能,因為ΔΣ調制器可以通過對輸出信號進行過采樣然后將結果平均,從而實現高精度。另一方面,SAR ADC的采樣電路并非連續(xù)運行。每一次采樣時,它都獲取一個模擬輸入 “快照”。

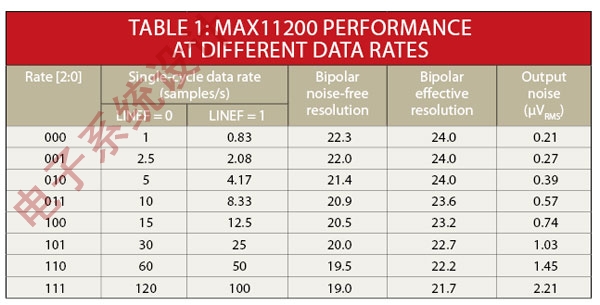

以較低輸出速率運行ΔΣ ADC無法實現節(jié)能(請參見“Lower-Power Delta-Sigma Design”) 。但是這種ADC可以提供較低的平均噪聲和更好的有效分辨率。比如,MAX11200 24位ΔΣADC就可以提供最大值低于1mW的低功耗和23位以上的高有效分辨率。可以通過改變輸出速率和過采樣率,在較低輸出速率下實現較高的有效分辨率。

MAX11200在2.4576MHz或2.048MHz內部振蕩器上工作時,可以在120samples/s的采樣率下實現21.7位有效分辨率,在10samples/s采樣率下實現23.6位有效分辨率。不過,可以通過軟件控制提供多個采樣率以及最終的無噪聲分辨率(NFR)、有效分辨率和RMS噪聲(參見表1)。

增加動態(tài)范圍,減少增益級

考慮是采用SAR ADC還是采用ΔΣ ADC時,查看一下整個信號鏈的功耗很有用。信號鏈可能包含一個可編程增益放大器(PGA)。許多SAR ADC會放大或者衰減輸入信號,以確保信號占據ADC最大輸入范圍的相當大部分。該幅度可以采用內部PGA或者通過指定使用外部PGA進行調整。

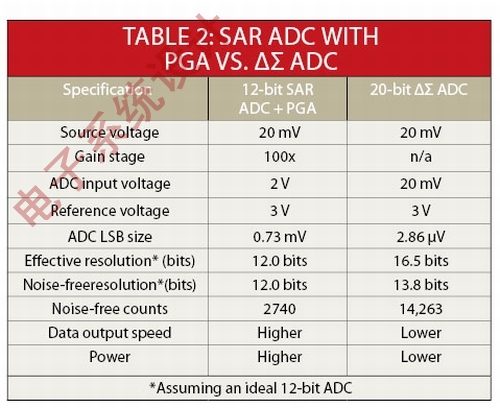

例如,測量由惠斯登電橋傳感器提供電源的20mV信號的設計可能會在電橋與ADC之間包含一個100的增益級。(ADC通常提供0至3V或者0至5V的輸入范圍。)假定一個采用3.0V電壓參考偏置的12位ADC,其最低有效位(LSB)為0.73mV。無增益時,ADC在20mV信號中(20mV/0.73mV)只能得到27位LSB。增加一個100V/V的增益級后,ADC可以在相同的信號中得到2740位LSB。

高分辨率、高性能ΔΣ ADC的成本已經下降到足以使其成為SAR ADC加PGA的價格合理的替代方案。采用具有低噪聲和最終的高有效分辨率的ΔΣ ADC時,可以一并去除PGA及其功耗。

許多ΔΣ ADC與傳感器直接連接,同時提供與SAR ADC加PGA方案相同的輸入信號粒度(分辨率)。ΔΣ ADC的低噪聲電平(1V以下)可以實現這種性能。由ADC的輸入范圍和內部噪聲電平確定的有效分辨率在基本上為直流的條件下捕獲ADC噪聲,這樣量化噪聲就不會構成問題:

有效分辨率 = log2 (電壓輸入范圍/電壓噪聲)

= log2 (20 mV/210 nV)

= 16.5位

采用同樣的20mV電橋信號和上述ADC(噪聲電平為210nVRMS)時,可能實現16.5位的有效分辨率。計算出有效分辨率之后,設計人員可以從中推斷出最終的無噪聲分辨率(有效分辨率:2.7位)和最終的無噪聲計數。無噪聲計數定義為在沒有噪聲干擾的情況下ADC可實現的讀數個數。例如,具有12.0位無噪聲分辨率的ADC(理想的12位ADC)可以提供4096個無噪聲計數。上個示例中的無噪聲計數為:

無噪聲計數(LSBs) = 2NFR

= 2(16.5 – 2.7)

= 213.8

= 14,263 LSBs

因此,與較低分辨率的SAR ADC加PGA方案對比時,具有低噪聲的ΔΣ ADC可以提供更高的有效分辨率、更高的無噪聲分辨率和更多的無噪聲計數。表2對理想的12位ADC加PGA與低噪聲ΔΣ ADC的規(guī)格進行了對比。ΔΣ ADC不僅可以實現更多的無噪聲計數和更高的分辨率,還可以實現較低的功率預算。主要折衷因素一般是ΔΣ ADC的最高采樣率比較低。

總而言之,對低功耗的需求已經催生出諸多降低總系統(tǒng)功耗的新技術:不同的ADC架構、突發(fā)模式處理、SAR ADC以較低采樣率工作以及降低電源電壓。雖然這些技術同時也引入了各種折衷因素,但是它們可以提供更長的電池使用壽命,或者可能允許使用更高性能的ADC,同時能夠滿足4至20mA電流回路的功率預算。

作者:Steve Logan