JPEG2000的兩大核心模塊(見圖1),,小波變換和EBCOT[2](基于優(yōu)化截?cái)帱c(diǎn)的嵌入式塊編碼)其運(yùn)算開銷很大,,占據(jù)了整個(gè)編碼器處理時(shí)間的一半以上。因此,,有必要研究合理的實(shí)現(xiàn)方式,,一般來(lái)說(shuō)采取軟件實(shí)現(xiàn)方式相對(duì)比較簡(jiǎn)單,比如JPEG2000的參考代碼jasper[3],,但實(shí)時(shí)處理的能力較差,,即使采用嵌入式系統(tǒng)的方案,如使用DSP或ARM等通用處理器,,基本上也是通過(guò)軟件的方式來(lái)實(shí)現(xiàn),,速度提升不大,必須針對(duì)塊編碼本身的特點(diǎn)設(shè)計(jì)高效的硬件結(jié)構(gòu)單元,。只有這樣,,才能使JPEG2000在實(shí)時(shí)處理的應(yīng)用中發(fā)揮其作用。

2.存儲(chǔ)優(yōu)化的實(shí)現(xiàn)方案

JPEG2000的嵌入式塊編碼是基于位平面的編碼,其對(duì)象是小波變換后頻域系數(shù)組成的相對(duì)較小的碼塊,,大小一般是32×32或64×64,。碼塊中的系數(shù)包含符號(hào)信息和許多個(gè)不同權(quán)值的幅度信息。位平面編碼的思想就是將最重要的信息先進(jìn)行編碼,,也就是權(quán)值較大的幅度信息先編碼,,這樣配合后續(xù)的碼流組織(見圖1)即可使最終的碼流獲得漸進(jìn)傳輸?shù)奶匦浴?/p>

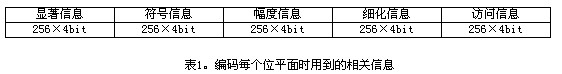

根據(jù)標(biāo)準(zhǔn)[1],編碼過(guò)程中除了用到符號(hào)和幅度信息外,,還需要每個(gè)比特位的顯著信息,,細(xì)化信息和訪問(wèn)信息。因此,,對(duì)于一個(gè)32×32的碼塊,,編碼一個(gè)位平面時(shí),總共需要存儲(chǔ)5×1024位的信息,。另外,,由于編碼是以一列中的4位為單位,所以通常將每塊編碼信息存儲(chǔ)為256×4的形式(見表1),。

但是事實(shí)上這種存儲(chǔ)結(jié)構(gòu)是低效的,,因?yàn)楦鶕?jù)標(biāo)準(zhǔn)[1],編碼一個(gè)比特位包括兩個(gè)步驟,,即判斷通道歸屬和編碼原操作,。在這兩個(gè)步驟中,需要訪問(wèn)的信息包括當(dāng)前位的顯著,、符號(hào),、幅度、細(xì)化和訪問(wèn)信息,,以及當(dāng)前位的周圍8個(gè)比特位的顯著和符號(hào)信息,。對(duì)于基于列的編碼方式,如果按照上面的方案存儲(chǔ)信息,,即將符號(hào)和顯著信息以字長(zhǎng)為4存儲(chǔ),,則實(shí)際上每次編碼一列,需要讀入前一編碼帶(通常將每4行稱為一個(gè)編碼帶),、當(dāng)前編碼帶和后一編碼帶的共12位顯著和符號(hào)信息,,但是事實(shí)上只有其中的6位是有用的,其余6位是冗余信息,。由于編碼是基于比特位的操作,,因此會(huì)頻繁地訪問(wèn)存儲(chǔ)區(qū)域,每次編碼一列必須讀出相應(yīng)的各信息位,,編碼完成一列數(shù)據(jù)還要將相應(yīng)的編碼信息再次寫回存儲(chǔ)區(qū)域,,以達(dá)到更新編碼信息的目的,。可見,,采取上述4位字長(zhǎng)的方案是非常低效的,。

所以,本文設(shè)計(jì)了一種相對(duì)合理的存儲(chǔ)方案,,即在碼塊的最上面一行和最下面一行各添加一行全0數(shù)據(jù)(這是對(duì)顯著和符號(hào)平面而言),,構(gòu)成34×32的塊,然后以兩行為一組,,并按交錯(cuò)存儲(chǔ)的方式,,即A,B,,C,,B,A,,,。。,。,C,,B,,A,將信息分配至三塊存儲(chǔ)區(qū)域MEMA,,MEMB和MEMC(見表2),。

另外,從顯著和符號(hào)信息緩存寫數(shù)據(jù)至相應(yīng)的寄存器(6×3bit)時(shí),,也要根據(jù)相應(yīng)的編碼帶進(jìn)行切換,,對(duì)于奇數(shù)編碼帶(假設(shè)第一個(gè)編碼帶記為零),順序?yàn)锳BC,,對(duì)于偶數(shù)的編碼帶,,順序?yàn)镃BA(見表3)。而且,,從表三可以看出,,用于訪問(wèn)MEMA、MEMB,、MEMC的地址信號(hào)的變化也不盡相同,,其中訪問(wèn)MEMB的地址順序增長(zhǎng),而MEMA的地址在從奇編碼帶過(guò)渡到偶編碼帶的過(guò)程中保持不變,,從偶編碼帶過(guò)渡到奇編碼帶的過(guò)程中增長(zhǎng),,對(duì)于MEMC的情況正好和MEMA相反,。

因此,必須設(shè)計(jì)相應(yīng)的控制電路和地址產(chǎn)生電路來(lái)配合這個(gè)存儲(chǔ)方案,。

3.硬件架構(gòu)

根據(jù)上面的分析,,提出相應(yīng)的位平面編碼器的硬件架構(gòu),如圖2所示,,本架構(gòu)針對(duì)32×32的碼塊,。

圖2.基于內(nèi)存優(yōu)化方案的位平面編碼器的硬件架構(gòu)

圖2中的位平面編碼器主要包括幾個(gè)部分,即內(nèi)部緩存,,寄存器組,,地址產(chǎn)生模塊,判斷通道歸屬模塊,,編碼原操作模塊,,狀態(tài)機(jī)模塊,計(jì)數(shù)器模塊,。

地址產(chǎn)生模塊包括兩個(gè),,地址產(chǎn)生模塊1負(fù)責(zé)產(chǎn)生讀取外部DWT系數(shù)緩存的地址信號(hào);地址產(chǎn)生模塊2負(fù)責(zé)產(chǎn)生讀取內(nèi)部5塊緩存區(qū)域的相應(yīng)地址。

判斷通道歸屬模塊,,根據(jù)當(dāng)前寄存器組中相應(yīng)的編碼信息,,判斷比特位是否屬于當(dāng)前的編碼通道,如果屬于當(dāng)前的編碼通道,,則進(jìn)行相應(yīng)的編碼原操作,,否則跳過(guò)該比特位,繼續(xù)編碼下一個(gè)比特位,。

編碼原操作模塊包括4部分,,即零值編碼、符號(hào)編碼,、細(xì)化編碼和游程編碼,。一般的實(shí)現(xiàn)方式采用查找表來(lái)實(shí)現(xiàn)編碼原操作,而本設(shè)計(jì)中均采用組合電路的形式來(lái)實(shí)現(xiàn),,這樣可以提高產(chǎn)生CX(編碼模式)和D(編碼比特位)的速度,。

狀態(tài)機(jī)模塊決定了整個(gè)編碼器的編碼流程,編碼主要分為兩個(gè)階段,,即預(yù)處理階段和模式產(chǎn)生階段,。預(yù)處理階段主要用于完成5塊緩存區(qū)域內(nèi)容的初始化,模式產(chǎn)生階段則按照顯著,、細(xì)化和清除通道的順序依次進(jìn)行編碼,,輸出編碼模式給后續(xù)的算術(shù)編碼模塊。狀態(tài)機(jī)模塊還接收來(lái)自計(jì)數(shù)器的輸出,,決定當(dāng)前處于什么狀態(tài),,在每個(gè)位平面編碼完成后必須轉(zhuǎn)到預(yù)處理階段,,更新下一位位平面的幅度信息,并清零訪問(wèn)緩存的內(nèi)容,。

4.Verilog設(shè)計(jì)

本文建議的硬件架構(gòu)采用VERILOG[4]語(yǔ)言描述,,主模塊是bpc.v,包括ram_block.v,,addr_generator.v,,fill_ram.v,pass_judge.v,,coding_primitive.v和state_machine.v共6 個(gè)子模塊,。編碼流程的實(shí)現(xiàn)通過(guò)主狀態(tài)機(jī)產(chǎn)生相應(yīng)的使能信號(hào),激活當(dāng)前的模塊操作,,當(dāng)操作完成后,,由該模塊產(chǎn)生操作中止信號(hào)給主狀態(tài)機(jī),從而使編碼流程進(jìn)入下一步驟,。下面列出了部分用于模塊間握手的代碼,,代碼中以省略號(hào)代表其它一些控制信號(hào)和其它一些狀態(tài)。

case (cstate)

,。,。。

gene_layer:begin

,。,。。gene_layer_en = 1;fill_ram_en = 0;pass_judge_en = 0; ,。。,。

if (gene_layer_fin) nstate = fill_ram;else nstate = gene_layer;end

fill_ram:begin

,。。,。gene_layer_en = 0;fill_ram_en = 1;pass_judge_en = 0; ,。。,。

if (fill_ram_fin) nstate = pass_judge;else nstate = fill_ram;end

,。。,。

endcase

5.實(shí)驗(yàn)結(jié)果

本設(shè)計(jì)采用modelsim工具進(jìn)行了功能仿真,,使用quartus[6]工具進(jìn)行了邏輯綜合,得到的綜合結(jié)果如表3所示,。

下面是使用jasper軟件和本硬件實(shí)現(xiàn)對(duì)幾幅標(biāo)準(zhǔn)圖像(大小512×512的灰度圖像)編碼的時(shí)間比較,。

6.結(jié)論

本文通過(guò)對(duì)JPEG2000中的位平面編碼器的存儲(chǔ)方案進(jìn)行了分析,,設(shè)計(jì)了一個(gè)高效的存儲(chǔ)結(jié)構(gòu)以及相應(yīng)的控制電路,設(shè)計(jì)采用verilog[4]語(yǔ)言描述,,通過(guò)quartus[6]軟件邏輯綜合后,,能夠在0.1s內(nèi)完成一幅512×512灰度圖像的編碼,編碼時(shí)間僅為jasper[3]軟件實(shí)現(xiàn)方案的30%左右,。由于塊編碼器的特點(diǎn),,每個(gè)碼塊的編碼本身是獨(dú)立的,可以并行進(jìn)行,,而且根據(jù)綜合結(jié)果,,使用EP1C12Q240C8完全可以在一塊芯片內(nèi)集成多個(gè)位平面編碼器的IP核,每個(gè)塊編碼器核可以并行執(zhí)行,,因此,,可以進(jìn)一步提高編碼器的速度,從而使實(shí)時(shí)處理圖像成為可能,。另外,,還可以將設(shè)計(jì)定制為ASIC,將最終產(chǎn)品應(yīng)用到數(shù)碼相機(jī),、圖像監(jiān)控中,,其市場(chǎng)前景是十分廣闊的。