ADV7125有3個(gè)視頻數(shù)據(jù)寄存器DATA REGISTER和一個(gè)視頻控制寄存器POWER-DOWN MODE。數(shù)據(jù)寄存器的3個(gè)輸入端分別連接紅綠藍(lán)三色的數(shù)字視頻信號(hào),數(shù)據(jù)寄存器后面緊跟數(shù)模轉(zhuǎn)換單元,將數(shù)字信號(hào)轉(zhuǎn)換為模擬信號(hào);控制寄存器將數(shù)字的消隱信號(hào)、同步信號(hào)轉(zhuǎn)換合并。數(shù)模轉(zhuǎn)換后的模擬視頻信號(hào)和控制寄存器輸出的同步、消隱控制信號(hào)共同作為ADV7125的輸出信號(hào),此輸出信號(hào)大小受Rset端和地之間接入的外加電阻RSET大小的控制。

2 ADV7125芯片用于VGA轉(zhuǎn)換的基本原理

ADV7125芯片用于VGA轉(zhuǎn)換的基本原理是,將S3C2440輸出的數(shù)字視頻信號(hào)轉(zhuǎn)換為模擬的VGA輸出信號(hào),模擬的VGA輸出信號(hào)的大小受ADV71 25芯片外圍參考電壓VREF和外加電阻RSET的控制,(VREF和RSET的具體接法如圖4所示)其關(guān)系如下:

![]()

式中IOG、IOR、IOB分別代表綠、紅、藍(lán)三色信號(hào)的幅度。當(dāng)不用復(fù)合同步信號(hào)![]() 時(shí),需要把

時(shí),需要把![]() 端連接低電平,這時(shí)IOG的關(guān)系式同式(2)。

端連接低電平,這時(shí)IOG的關(guān)系式同式(2)。

上式中的![]() 是ADV7125的一個(gè)附加信號(hào)控制端,ADV7125的另外一個(gè)附加信號(hào)控制端是

是ADV7125的一個(gè)附加信號(hào)控制端,ADV7125的另外一個(gè)附加信號(hào)控制端是![]() (消隱信號(hào)控制端)。

(消隱信號(hào)控制端)。![]() 和

和![]() 都是在時(shí)鐘上升沿被鎖存,保證像素?cái)?shù)據(jù)流的同步。

都是在時(shí)鐘上升沿被鎖存,保證像素?cái)?shù)據(jù)流的同步。![]() 和

和![]() 的功能是:通過視頻同步信號(hào)的編碼,影響VGA視頻信號(hào)的輸出。通過在模擬輸出端口內(nèi)部加了一個(gè)加權(quán)電流,實(shí)現(xiàn)此功能。這個(gè)電流的有無,由

的功能是:通過視頻同步信號(hào)的編碼,影響VGA視頻信號(hào)的輸出。通過在模擬輸出端口內(nèi)部加了一個(gè)加權(quán)電流,實(shí)現(xiàn)此功能。這個(gè)電流的有無,由![]() 和

和![]() 邏輯輸入判定。

邏輯輸入判定。

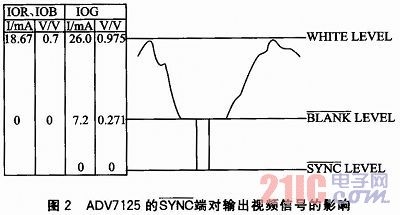

圖2說明了當(dāng)![]() 和

和![]() 兩者都為高電平時(shí),IOR和IOB兩者與IOG的對(duì)比。

兩者都為高電平時(shí),IOR和IOB兩者與IOG的對(duì)比。

表1詳細(xì)說明了![]() 和

和![]() 對(duì)模擬輸出的影響。該表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的條件下測(cè)量的。

對(duì)模擬輸出的影響。該表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的條件下測(cè)量的。

對(duì)應(yīng)圖2和表1可得到以下結(jié)論:

①當(dāng)IOR、IOG、IOB三端的DAC輸入為0x00時(shí),代表屏幕最黑,此時(shí)對(duì)應(yīng)圖2為![]() LEVEL,對(duì)應(yīng)表1為第7行。從圖2左面列表可以看到,IOR、IOB端的電流、電壓分別是0mA、0V,IOG端的電流、電壓分別是7.2 mA、0.271 V。即電流相差7.2 mA。

LEVEL,對(duì)應(yīng)表1為第7行。從圖2左面列表可以看到,IOR、IOB端的電流、電壓分別是0mA、0V,IOG端的電流、電壓分別是7.2 mA、0.271 V。即電流相差7.2 mA。

②當(dāng)IOR、IOG、IOB三端的DAC輸入為0xFF時(shí),代表屏幕最白,此時(shí)對(duì)應(yīng)圖2為WHITE LEVEI,對(duì)應(yīng)表1為第2行。從圖2左面列表可以看到,IOR、IOB端的電流、電壓分別是18.67 mA、0.7 V,IOG端的電流、電壓分別是26.0 mA、0.975 V。即電流相差7.3 mA。

從表1,可以得到以下的結(jié)論:

①當(dāng)![]() 和

和![]() 都為高電平(為1)時(shí),IOG端口的白電平信號(hào)的電流,要比IOR、IOB端口同樣情況下的電流高出7.3mA左右;視頻信號(hào)電流、黑電平信號(hào)的電流,要比IOR、IOB端口同樣情況下的電流高出7.2 mA左右。

都為高電平(為1)時(shí),IOG端口的白電平信號(hào)的電流,要比IOR、IOB端口同樣情況下的電流高出7.3mA左右;視頻信號(hào)電流、黑電平信號(hào)的電流,要比IOR、IOB端口同樣情況下的電流高出7.2 mA左右。

②當(dāng)![]() 為低電平(為0)、

為低電平(為0)、![]() 任意時(shí),同樣的DAC輸入條件下,IOR、IOB、IOG三端的輸出信號(hào)電流大小是完全一樣的。

任意時(shí),同樣的DAC輸入條件下,IOR、IOB、IOG三端的輸出信號(hào)電流大小是完全一樣的。

③當(dāng)![]() 為低電平(為0)時(shí),無論DAC輸入是多少,IOR、IOG、IOB三端的輸出信號(hào)均對(duì)應(yīng)于

為低電平(為0)時(shí),無論DAC輸入是多少,IOR、IOG、IOB三端的輸出信號(hào)均對(duì)應(yīng)于![]() 高/低的同步無效/有效黑電平。

高/低的同步無效/有效黑電平。

3 VGA接口設(shè)計(jì)

根據(jù)需要,把LCD信號(hào)轉(zhuǎn)換為VGA信號(hào),轉(zhuǎn)換時(shí)必須根據(jù)VGA信號(hào)的時(shí)序進(jìn)行轉(zhuǎn)換。VGA信號(hào)一共包括5部分,分別是紅(R)、綠(G)、藍(lán)(B)三色信號(hào)和行(H)、場(chǎng)(V)同步信號(hào),紅(R)、綠(G)、藍(lán)(B)三色信號(hào)和行(H)、場(chǎng)(V)同步信號(hào)根據(jù)S3C2440的配置時(shí)序,由S3C2440以數(shù)字信號(hào)的形式輸出,之后由ADV7125對(duì)紅(R)、綠(G)、藍(lán)(B)三色信號(hào)進(jìn)行轉(zhuǎn)換,行(H)、場(chǎng)(V)同步信號(hào)直接進(jìn)入VGA接口中,不需要轉(zhuǎn)換。下面分別介紹VGA信號(hào)的時(shí)序、硬件連接、軟件設(shè)計(jì)以及注意事項(xiàng)。

3.1 VGA時(shí)序信號(hào)

以分辨率為640x480、刷新頻率為60 Hz、16位的彩色顯示模式為例,VGA信號(hào)的掃描時(shí)序如圖3所示。

在場(chǎng)掃描時(shí)序中,VSYNC為場(chǎng)同步信號(hào),Tvsync是指顯示器掃描1幀完整畫面需要的時(shí)間,大小為16 667μs;VSYNC信號(hào)每場(chǎng)有525行,其中480行為有效顯示行,45行是場(chǎng)消隱期。場(chǎng)消隱期包括場(chǎng)同步時(shí)間(低電平場(chǎng)同步脈沖)twv(2行/63μs)、場(chǎng)消隱前肩tHV(13行/412μs)、場(chǎng)消隱后肩tVH(30行/952 μs),共45行。

在行掃描時(shí)序中,HSYNC為行同步信號(hào),Thsync是指顯示器掃描一行需要的時(shí)間,大小為31.75μs,該周期通過Hsync(行同步脈沖)來同步,脈沖的寬度tWH=3.81μs。每顯示行包括800點(diǎn),其中640點(diǎn)為有效顯示區(qū),160點(diǎn)為行消隱期(是非顯示區(qū))。行消隱期包括行同步時(shí)間tWH(3.81μs),行消隱前肩tHC(0.516μS)和行消隱后肩tCH(1.786μs),共160個(gè)點(diǎn)時(shí)鐘。

3.2 S3C2440和ADV7125的電路連接

設(shè)計(jì)中主要使用S3C2440處理器的LCD控制器接口,它主要通過DMA方式占用系統(tǒng)總線,支持彩色TFT液晶屏,支持16 bbp無調(diào)色真彩。LCD接口數(shù)據(jù)的低8位,中間8位和高8位分別與ADV7125芯片的BLUE信號(hào)、GREEN信號(hào)和RED信號(hào)相連,這樣就完成了S3C2440處理器與ADV7125芯片之間數(shù)字信號(hào)的傳輸。ADV7125芯片的時(shí)鐘信號(hào)采用LCD接口的時(shí)鐘信號(hào),![]() 信號(hào)與VM(VSDN)信號(hào)相連接,

信號(hào)與VM(VSDN)信號(hào)相連接,![]() 同步信號(hào)接地。COMP端用于內(nèi)部參考運(yùn)放的補(bǔ)償,用0.1μF的陶瓷電容連接在COMP與模擬電源VAA之間,防止自激振蕩以增加穩(wěn)定性。采用AD1580作為參考電壓,AD1580輸出信號(hào)穩(wěn)定,能夠很好地滿足電路設(shè)計(jì)的需要。RSET引腳與地之間接一個(gè)530 Ω的電阻,用來控制視頻信號(hào)的滿幅度。在圖像系統(tǒng)中,不會(huì)自動(dòng)產(chǎn)生復(fù)合同步信號(hào)

同步信號(hào)接地。COMP端用于內(nèi)部參考運(yùn)放的補(bǔ)償,用0.1μF的陶瓷電容連接在COMP與模擬電源VAA之間,防止自激振蕩以增加穩(wěn)定性。采用AD1580作為參考電壓,AD1580輸出信號(hào)穩(wěn)定,能夠很好地滿足電路設(shè)計(jì)的需要。RSET引腳與地之間接一個(gè)530 Ω的電阻,用來控制視頻信號(hào)的滿幅度。在圖像系統(tǒng)中,不會(huì)自動(dòng)產(chǎn)生復(fù)合同步信號(hào)![]() ,利用本設(shè)計(jì)可以實(shí)現(xiàn)視頻同步信息編碼直接進(jìn)入綠色信道。如果不需要,把

,利用本設(shè)計(jì)可以實(shí)現(xiàn)視頻同步信息編碼直接進(jìn)入綠色信道。如果不需要,把![]() 輸入端與邏輯低電平相連。S3C2440和ADV7125的電路連接如圖4所示。其中VD0、VD1、…VD23、VDEN、CLK、HSYNC、VSYNC為S3C2440的輸出端。

輸入端與邏輯低電平相連。S3C2440和ADV7125的電路連接如圖4所示。其中VD0、VD1、…VD23、VDEN、CLK、HSYNC、VSYNC為S3C2440的輸出端。

3.3 電路連接需要注意的問題

ADV7125可以用于灰度視頻信號(hào)輸出。例如:僅用于1個(gè)通道進(jìn)行視頻輸出,這時(shí)其他兩個(gè)不用的視頻數(shù)據(jù)信道都應(yīng)該與邏輯0相連,不用的模擬輸出應(yīng)該與使用的信道一樣連接相同的負(fù)載。

為了實(shí)現(xiàn)ADV7125的最優(yōu)噪聲性能,對(duì)PCB的設(shè)計(jì)必須特別注意。ADV7125電源和地線上的噪聲應(yīng)該優(yōu)化。可以通過屏蔽數(shù)字輸入和提供好的退耦達(dá)到這一點(diǎn)。VAA和GND的引線長(zhǎng)度應(yīng)該盡量短,這樣可以減小電感環(huán)路。在設(shè)計(jì)PCB時(shí)應(yīng)盡量把模擬地與數(shù)字地分開,地線應(yīng)該通過1個(gè)磁珠與PCB大面積鋪地相連,并且磁珠應(yīng)該盡可能的靠近ADV7125器件的地引腳。電路中使用的電容應(yīng)該盡可能的靠近對(duì)應(yīng)引腳,并且電容的引線應(yīng)該盡可能的短,這樣可以減小引線電容。由于使用頻率非常高,時(shí)鐘引線應(yīng)盡可能地短,這樣可以減小噪聲的抖動(dòng)。視頻輸出信號(hào)應(yīng)該由數(shù)字地平面覆蓋,這樣可以增大高頻電源抑制比。

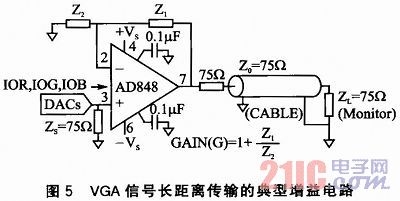

由于模擬RGB信號(hào)采用高阻電流源輸出方式,可以直接驅(qū)動(dòng)75 Ω的同軸傳輸線。長(zhǎng)于10 m的電纜可能會(huì)對(duì)高頻模擬輸出脈沖衰減。使用輸出緩沖可以補(bǔ)償電纜的失真。這些緩沖器在整個(gè)輸出電壓擺幅期間,必須有足夠的電流。常見的有AD84x系列的單片運(yùn)放。在較高的頻率下(如80 MHz),推薦使用AD848。其典型增益電路如圖5所示。

通過簡(jiǎn)單的計(jì)算可以得知其增益為:GAIN=1+Z1/Z2。改變緩沖電路的增益器件Z1、Z2來滿足所要求的視頻電平。

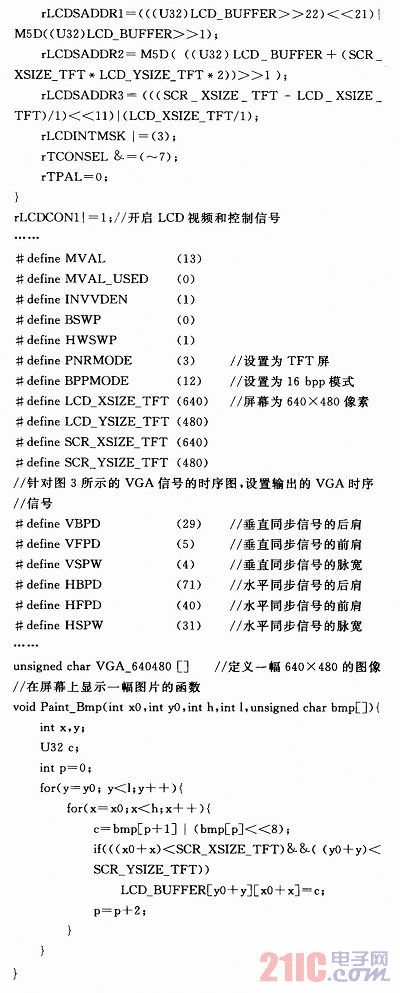

3.4 相關(guān)的軟件設(shè)置

下面以簡(jiǎn)單的測(cè)試程序?yàn)槔齺碚f明相關(guān)軟件的編寫。

軟件設(shè)計(jì)的基本流程如圖6所示。具體過程如下:

①首先對(duì)LCD的功能寄存器進(jìn)行初始化,主要設(shè)置LCD控制寄存器1~5,LCD緩沖區(qū)起始地址控制寄存器;屏蔽LCD中斷。

②其次對(duì)LCD的輸出時(shí)序(VGA信號(hào)時(shí)序)進(jìn)行設(shè)置。設(shè)置分辨率、周期、前(后)信號(hào)、同步脈沖。

③再次是對(duì)視頻信號(hào)進(jìn)行設(shè)置,主要是使能LCD視頻信號(hào)的輸出。

④用一幅圖像的輸出來測(cè)試VGA的顯示是否正常。

主要代碼如下所示:

結(jié)語

本文結(jié)合S3C2440處理器和ADV7125芯片的特點(diǎn),介紹了LCD轉(zhuǎn)VGA方案,該方案簡(jiǎn)單易行,適用于嵌入式系統(tǒng)設(shè)備的VGA信號(hào)輸出。ADV-7125芯片有多種頻率可供選擇。本設(shè)計(jì)也可以用于灰度級(jí)輸出的信號(hào)中,在此基礎(chǔ)上進(jìn)行一些簡(jiǎn)單的修改,可以滿足高分辨率,高刷新頻率的環(huán)境要求。