0 引言

基準(zhǔn)電壓源廣泛應(yīng)用于電源調(diào)節(jié)器、A/D和D/A轉(zhuǎn)換器、數(shù)據(jù)采集系統(tǒng),以及各種測(cè)量設(shè)備中。近年來,隨著微電子技術(shù)的迅速發(fā)展,低壓低功耗已成為當(dāng)今電路設(shè)計(jì)的重要標(biāo)準(zhǔn)之一。比如,在一些使用電池的系統(tǒng)中,要求電源電壓在3 V以下。因此,作為電源調(diào)節(jié)器、A/D和D/A轉(zhuǎn)換器等電路核心功能模塊之一的電壓基準(zhǔn)源,必然要求在低電源電壓下工作。

在傳統(tǒng)的帶隙基準(zhǔn)源設(shè)計(jì)中,輸出電壓常在1.25 V左右,這就限制了最小電源電壓。另一方面,共集電極的寄生BJT和運(yùn)算放大器的共模輸入電壓,也限制了PTAT電流生成環(huán)路的低壓設(shè)計(jì)。近年來,一些文獻(xiàn)力圖解決這方面的問題。歸納起來,前一問題可以通過合適的電阻分壓來實(shí)現(xiàn);第二個(gè)問題可以通過BiCMOS工藝來實(shí)現(xiàn),或通過低閾值電壓的MOS器件來實(shí)現(xiàn),但工藝上的難度以及設(shè)計(jì)成本將上升。

基于上面的考慮,本文首先對(duì)傳統(tǒng)的帶隙電壓源原理進(jìn)行分析,然后提出了一種比較廉價(jià)且性能較高的低壓帶隙基準(zhǔn)電壓源,采用電流反饋、一級(jí)溫度補(bǔ)償技術(shù)設(shè)計(jì)了低壓CMOS帶隙基準(zhǔn)源電路,使其電路能工作在較低的電壓下。本文介紹這種帶隙電壓基準(zhǔn)源的設(shè)計(jì)原理,給出了電路的仿真結(jié)果,并對(duì)結(jié)果進(jìn)行了分析。并基于CSMC 0.5μm Double Poly Mix Process對(duì)電路進(jìn)行了仿真,得到理想的結(jié)果。

l 低壓COMS基準(zhǔn)電壓源設(shè)計(jì)

1.1 傳統(tǒng)的帶隙基準(zhǔn)源

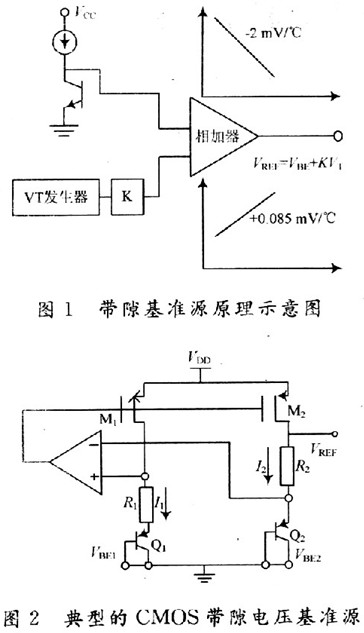

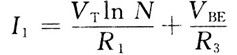

圖1為帶隙基準(zhǔn)電壓源的原理示意圖。雙極性晶體管的基極-發(fā)射極電壓VBE,具有負(fù)的溫度系數(shù),其溫度系數(shù)一般為-2.2 mV/K。而熱電壓VT具有正的溫度系數(shù),其溫度系數(shù)在室溫下為十0.085 V/K。將VT乘以常數(shù)K并和VBE相加就得到輸出電壓VREF:

![]()

將式(1)對(duì)溫度T微分并代入VBE和VT的溫度系數(shù)可求得K,它使VREF的溫度系數(shù)在理論上為零。VBE受電源電壓變化的影響很小,因而帶隙基準(zhǔn)電壓的輸出電壓受電源的影響也很小。

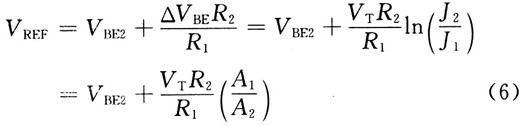

圖2是典型的CMOS帶隙電壓基準(zhǔn)源電路。兩個(gè)PNP管Q1,Q2的基極一發(fā)射極電壓差△VBE:

![]()

式中:J1和J2是流過Ql和Q2的電流密度。運(yùn)算放大器的作用使電路處于深度負(fù)反饋狀態(tài),使得節(jié)點(diǎn)1和節(jié)點(diǎn)2的電壓相等。即:

由圖2可得:

![]()

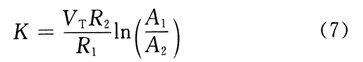

通過M1和M2的鏡像作用,使得I1和I2相等,結(jié)合式(4)和式(5)可得:

式中;A1和A2是Q1和Q2的發(fā)射極面積。比較式(5)和式(1),可得常數(shù)K為:

在實(shí)際設(shè)計(jì)中,K值即為式(7)表示。

傳統(tǒng)帶隙基準(zhǔn)源結(jié)構(gòu)能輸出比較精確的電壓,但其電源電壓較高(大于3 V),且基準(zhǔn)輸出范圍有限(1.2 V以上)。要在1.8 V以下的電源電壓得到1.2 V以下的精確基準(zhǔn)電壓,就必須對(duì)基準(zhǔn)源結(jié)構(gòu)上進(jìn)行改進(jìn)和提高。

1.2 低壓COMS基準(zhǔn)電壓源的電路設(shè)計(jì)

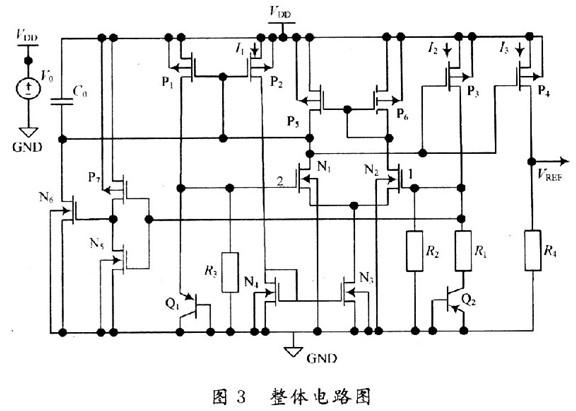

本設(shè)計(jì)基于CSMC-O.5μm-CMOS工藝(NMOS的閾值電壓為0.536 V,PMOS的閾值電壓為-0.736 V)。采用一級(jí)溫度補(bǔ)償、電流反饋技術(shù)設(shè)計(jì)的低壓帶隙基準(zhǔn)源電路如圖3所示。低壓帶隙基準(zhǔn)源的電流不僅用于提供基準(zhǔn)輸出所需的電流,也用于產(chǎn)生差分放大器所需的電流源偏置電壓,簡(jiǎn)化了電路和版圖設(shè)計(jì)。

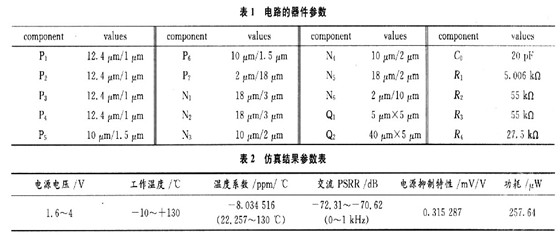

為了與CMOS標(biāo)準(zhǔn)工藝兼容,電路中PNP的e,b,c區(qū)分別采用P+,N-well,P-sub集電極接地。Q2和Q1的發(fā)射極面積比為8:1,流過Q1和Q2的電流相等,這樣△VBE等于VTln 8。流過電阻R1的電流與熱力學(xué)溫度成正比。三路鏡像電流源使得流過P2,P3,P4的電流相等(I1=I2=I3)。

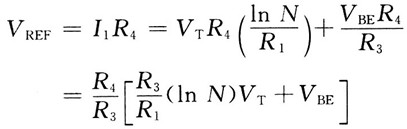

輸出電壓VREF為:

電路中的溫度補(bǔ)償系數(shù)K為:

通過調(diào)節(jié)R4的值,可以調(diào)節(jié)輸出電壓VREF的大小。在電源電壓變化時(shí),P2,P3,P4的漏源電壓值保持不變,與電源電壓無關(guān),其柵極電壓由運(yùn)放調(diào)節(jié)。為了降低電路的復(fù)雜度,應(yīng)用電流反饋原理,運(yùn)放采用簡(jiǎn)單的一階運(yùn)放,由于VDD的變化多于GND的變化,故運(yùn)放的輸入采用NMOS的差分對(duì)結(jié)構(gòu)。因?yàn)檎麄€(gè)電路在低壓下工作,故整個(gè)電路設(shè)計(jì)的重點(diǎn)是要保證低壓下運(yùn)放的正常工作。

由于帶隙基準(zhǔn)源存在兩個(gè)電路平衡點(diǎn),即零點(diǎn)和正常工作點(diǎn)。當(dāng)基準(zhǔn)源工作在零點(diǎn)時(shí),節(jié)點(diǎn)1、2的電壓等于零,基準(zhǔn)源沒有電流產(chǎn)生。固需要設(shè)計(jì)一個(gè)啟動(dòng)電路,避免基準(zhǔn)源工作在平衡零點(diǎn)。本設(shè)計(jì)的啟動(dòng)電路由N5、N6和P7構(gòu)成。當(dāng)電路工作在零點(diǎn)時(shí),N6管導(dǎo)通,迅速提高節(jié)點(diǎn)1、2的電壓,產(chǎn)生基準(zhǔn)電流,節(jié)點(diǎn)1的電壓通過P7和N5組成的反相器,使N6管完全截止,節(jié)點(diǎn)1、2的電壓回落在穩(wěn)定的工作點(diǎn)上,基準(zhǔn)源開始正常工作。

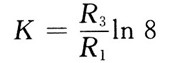

電路的器件參數(shù)如表1所示,P2,P3,P4管的尺寸較大,是為了降低電路中的1/f噪聲。電流鏡的負(fù)載管P5,P6和差分對(duì)管N1,N2的寬長(zhǎng)比較大,以抑制電路的熱噪聲。由于電路中的電阻值較大,故在工藝中用阱電阻實(shí)現(xiàn)。電容C0有助于電路的穩(wěn)定,同時(shí)還可以減小于運(yùn)放的寬度,有助于降低噪聲的影響。

2 仿真與結(jié)果分析

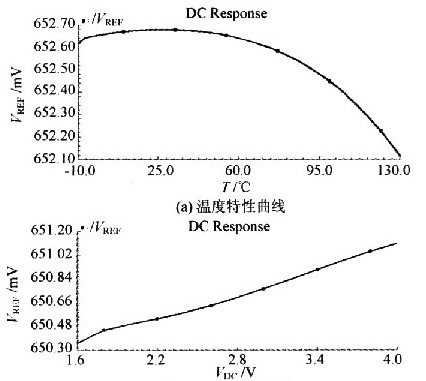

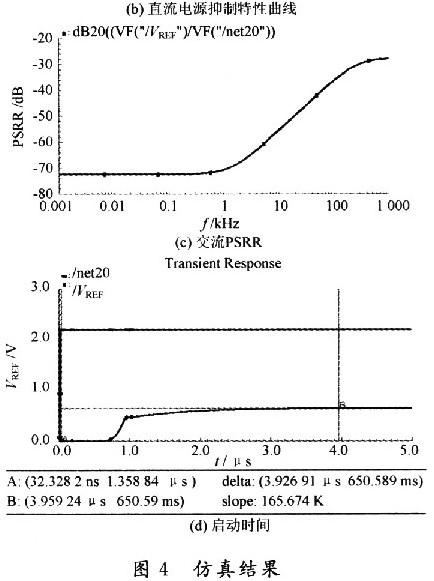

在Cadence設(shè)計(jì)平臺(tái)下的Spectre仿真器中基于CSMC 0.5 μm CMOS工藝模型對(duì)電路進(jìn)行了仿真。得到電路的溫度特性曲線、直流電源抑制特性曲線、交流PSRR特性曲線、啟動(dòng)時(shí)間曲線如圖4所示。各項(xiàng)仿真結(jié)果參數(shù)如表2所示。

3 結(jié)語

在應(yīng)用典型CMOS電壓基準(zhǔn)源的基礎(chǔ)上,綜合一級(jí)溫度補(bǔ)償、電流補(bǔ)償技術(shù),設(shè)計(jì)了帶隙電壓基準(zhǔn)源電路。該帶隙基準(zhǔn)源電路的電源工作范圍為1.6~4 V,工作溫度為-10~+130℃,基準(zhǔn)輸出電壓VREF為(650.5±0.5)mV,溫度系數(shù)可低至2.0 ppm/℃,電源抑制比為-70 dB。仿真結(jié)果證明了設(shè)計(jì)的正確性。