根據(jù)某工業(yè)現(xiàn)場電子設(shè)備數(shù)據(jù)記錄的要求,設(shè)計了一種基于近距離無線通信的嵌入式數(shù)據(jù)記錄系統(tǒng)。該系統(tǒng)分為數(shù)據(jù)存儲和數(shù)據(jù)下載兩大功能組成部分:數(shù)據(jù)存儲部分利用DSP和FPGA完成信號的采集和處理,并將其存儲到CF卡中;數(shù)據(jù)下載部分利用紅外和藍(lán)牙無線接口,在DSP的控制下實現(xiàn)數(shù)據(jù)的無線下載。

引言

“黑匣子”是比較流行的電子記錄設(shè)備之一,廣泛應(yīng)用于實時記錄飛機、船舶、汽車等行進(jìn)過程中的重要數(shù)據(jù)。記錄儀的數(shù)據(jù)下載方式通常有兩種:通過傳輸線纜下載和通過插拔存儲卡下載。

本文依據(jù)某工業(yè)現(xiàn)場電子設(shè)備數(shù)據(jù)記錄的需求,提出了一種基于近距離無線通信的數(shù)據(jù)記錄設(shè)備。該設(shè)備以紅外或藍(lán)牙方式下載數(shù)據(jù),與傳統(tǒng)的數(shù)據(jù)下載方式相比,下載數(shù)據(jù)時既不需要拆卸設(shè)備連接線纜或插拔存儲卡,又減少了連線和插拔存儲卡可能導(dǎo)致的接觸故障。

1 設(shè)計需求

在某工業(yè)現(xiàn)場電子設(shè)備工作過程中,要求記錄系統(tǒng)能夠?qū)崟r記錄設(shè)備的各種電氣信號及其工作時序,用于事后設(shè)備運行狀況的分析以及故障排查、定位。需要實時采集記錄的信號包括2路ARINC429信號、10路TTL數(shù)字信號以及16路模擬信號。采樣頻率應(yīng)大于或等于1 kHz,記錄時間為1 h左右。根據(jù)信號通道數(shù)量、數(shù)據(jù)采集速率和數(shù)據(jù)記錄時間,可估算出記錄系統(tǒng)的存儲容量應(yīng)大于500 MB。通常,微處理器內(nèi)部的存儲空間有限,故需要將采集到的數(shù)據(jù)存儲到存儲容量大、具有非易失性的外部存儲器中。本系統(tǒng)使用Sandisk公司的1 GB工業(yè)級CF卡作為存儲設(shè)備。

2 系統(tǒng)總體設(shè)計方案

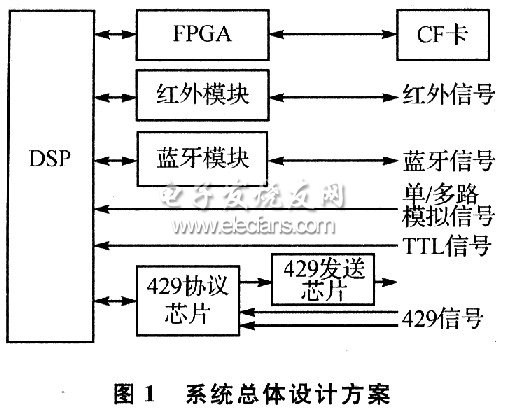

系統(tǒng)采用DSP和FPGA協(xié)同控制的方案,總體設(shè)計方案如圖1所示。DSP主要完成數(shù)據(jù)的實時采集和控制,F(xiàn)PGA的數(shù)據(jù)傳輸,以及與無線通信模塊的數(shù)據(jù)傳輸;FPGA則實現(xiàn)數(shù)據(jù)緩存和讀寫CF卡的邏輯時序控制。

DSP是主控制器。選用TI公司的16位定點DSP芯片TMS320F240。它的指令周期為50 ns,內(nèi)部具有544字的RAM、224K字的可尋址存儲空間、雙10位模/數(shù)轉(zhuǎn)換器、28個獨立可編程的多路復(fù)用I/O引腳、1個異步串行通信口(SCI),以及1個同步串行通信口(SPI)。其內(nèi)部資源可以滿

足系統(tǒng)對TTL信號和模擬信號的采集需求,通過外接ARINC429、紅外和藍(lán)牙專用接口芯片,實現(xiàn)ARINC429數(shù)據(jù)信號的采集和兩種無線方式的通信。

FPGA是輔助控制器,其核心為FIFO和邏輯控制電路,用于完成DSP和CF卡間數(shù)據(jù)傳輸。選用Altera公司CyclonelI系列的FPGA芯片EP2C20-Q240C8。它具有142個用戶可使用I/O引腳、52個M4K嵌入式陣列塊和18752個邏輯單元。DSP和FPGA豐富的內(nèi)部資源很好地滿足了系統(tǒng)設(shè)計的需要。

系統(tǒng)主要包括數(shù)據(jù)存儲和數(shù)據(jù)下載兩大功能:

①數(shù)據(jù)存儲。DSP實現(xiàn)對2路ARINC429信號、16路模擬信號和10路數(shù)字信號的實時采集,并將數(shù)據(jù)實時存入FPGA的FIFO中。當(dāng)FIFO存儲了一定量數(shù)據(jù)時,F(xiàn)PGA控制邏輯電路自動將FIFO中的數(shù)據(jù)寫入CF卡中。

②數(shù)據(jù)下載。首先,DSP將系統(tǒng)的藍(lán)牙和紅外模塊設(shè)置為從設(shè)備。當(dāng)接收到工作人員所持的帶有藍(lán)牙或紅外接口的地面設(shè)備發(fā)出的連接請求后,先進(jìn)行鑒權(quán),鑒權(quán)通過后與其建立連接。然后,F(xiàn)PGA控制邏輯電路讀出CF卡中數(shù)據(jù)并存人FIFO,DSP通過查詢或中斷方式將FIFO中的數(shù)據(jù)通過無線通信模塊發(fā)送給地面設(shè)備。

3 各功能模塊設(shè)計

3.1 FPGA功能模塊設(shè)計

使用FPGA實現(xiàn)異步FIFO模塊和CF卡讀寫模塊,是本設(shè)計的重點,也是難點。3.1.1異步FIFO模塊

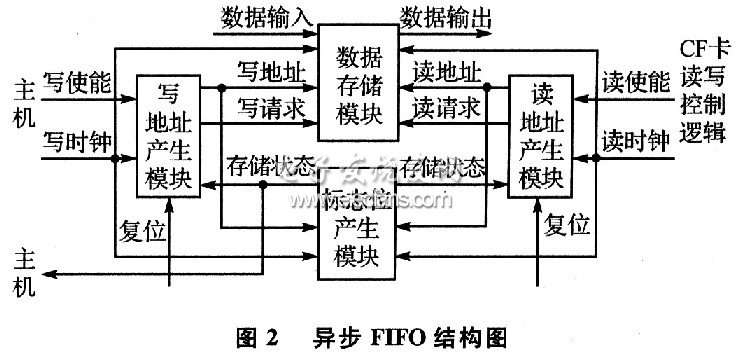

數(shù)據(jù)記錄設(shè)備的實時性強、數(shù)據(jù)量大。為了提高數(shù)據(jù)傳輸速度、避免數(shù)據(jù)堵塞,利用FPGA硬件設(shè)計上的靈活性,在其內(nèi)部構(gòu)建了一個寬度為16位、深度為512的異步FIFO模塊,作為DSP與CF卡之間數(shù)據(jù)傳輸?shù)闹欣^站。

異步FIFO的結(jié)構(gòu)圖如圖2所示。它包括4個模塊:數(shù)據(jù)存儲模塊、寫地址產(chǎn)生模塊、讀地址產(chǎn)生模塊和標(biāo)志位產(chǎn)生模塊。FIFO的讀寫采用讀時鐘和寫時鐘兩個時鐘。寫時鐘同步的信號有寫地址產(chǎn)生模塊生成的寫請求和寫地址;讀時鐘同步的信號有讀地址產(chǎn)生模塊生成的讀請求和讀地址。寫使能和讀使能分別由DSP與FPGA數(shù)據(jù)傳輸控制邏輯和CF卡讀寫控制邏輯生成。標(biāo)志位產(chǎn)生模塊由讀寫地址關(guān)系生成FIFO存儲狀態(tài)標(biāo)志,并反饋給主機DSP。DSP通過查詢該標(biāo)志來控制與FPGA的數(shù)據(jù)傳輸。

3.1.2 CF卡讀寫模塊

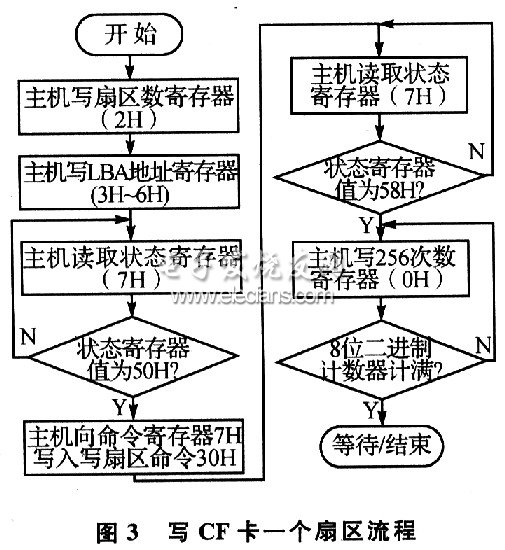

CF卡讀寫模塊分為CF卡讀控制模塊和CF卡寫控制模塊。CF卡讀或?qū)懩K的設(shè)計具有相似性。這里僅介紹寫CF卡的工作過程。

首先,設(shè)置CF卡的屬性寄存器。CF卡有4個屬性寄存器,通常只需設(shè)置“配置選擇寄存器”以選擇CF卡的讀寫模式。CF卡的讀寫模式有3種:I/O模式、Memory模式和True IDE模式。本設(shè)計使用16位的Memory模式讀寫CF卡。Memory模式是CF卡默認(rèn)的讀寫模式,所以在CF卡初始化過程中不需要設(shè)置“配置屬性寄存器”。

其次,設(shè)置CF卡的任務(wù)文件寄存器。本設(shè)計中使用的任務(wù)文件寄存器有:數(shù)據(jù)寄存器、扇區(qū)數(shù)寄存器、扇區(qū)號寄存器、低柱面號寄存器、高柱面號寄存器、驅(qū)動器選擇/磁頭寄存器和狀態(tài)/命令寄存器。對它們進(jìn)行沒置,可選擇扇區(qū)尋址方式,設(shè)定每次讀寫的扇區(qū)數(shù)和邏輯尋址地址,并獲取CF卡狀態(tài)以及輸入讀寫命令。

CF卡的尋址方式與計算機的硬盤操作方式類似。扇區(qū)的尋址方式有兩種:物理尋址方式(CHS)和邏輯尋址方式(LBA)。本設(shè)計使用LBA尋址,對應(yīng)28位LBA地址。

磁頭寄存器存放LBA地址的27~24位;柱面號寄存器存放LBA地址的23~8位;扇區(qū)號寄存器存放LBA地址的7~0位。

寫CF卡一個扇區(qū)的流程如圖3所示。每次向CF卡存儲數(shù)據(jù)時,應(yīng)該先獲取上次存儲到的扇區(qū)的LBA地址,從而獲得此次存儲的起始扇區(qū)地址。為了記錄每次存儲到的扇區(qū)的地址,將LBA地址為0的扇區(qū)保留,專用于記錄扇區(qū)地址。在開始一次寫操作之前,應(yīng)該先讀取LBA地址為O的扇區(qū),獲得上次存儲的LBA地址;然后加1獲得此次寫操作的LBA地址,并向指定的扇區(qū)寫數(shù)據(jù)。

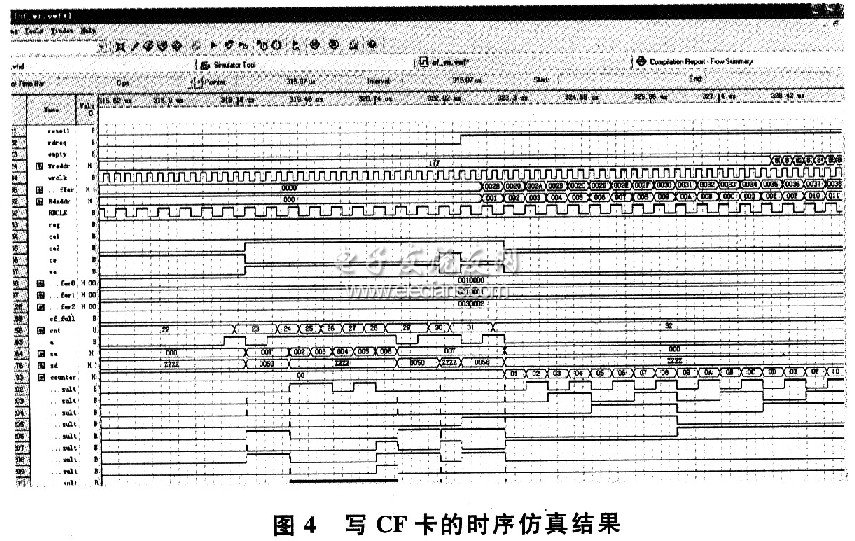

利用QuartusII作為FPGA開發(fā)平臺,使用VHDL硬件描述語言實現(xiàn)了FPGA與DSP的接口、異步FIFO的存儲以及CF卡的讀寫邏輯。在QuartusII自帶仿真工具下得到的寫CF卡時序仿真結(jié)果如圖4所示。

3.2 無線通信模塊設(shè)計

3.2.1 藍(lán)牙模塊設(shè)計

藍(lán)牙模塊采用BTM0604C2P。它內(nèi)嵌藍(lán)牙芯片BlueCore4-Ext,兼容藍(lán)牙2.0+EDR規(guī)范,最高支持3 Mbps的數(shù)據(jù)速率,外置天線,有效距離為10 m,具有標(biāo)準(zhǔn)的UART接口。

DSP與藍(lán)牙模塊之間通過HCI協(xié)議層建立連接。HCI(Host Controller Interface,主機控制器接口)協(xié)議,為DSP提供了一個訪問藍(lán)牙模塊內(nèi)部基帶控制器和鏈路管理器的命令接口,可以獲取藍(lán)牙芯片的配置參數(shù)。

本設(shè)計中,DSP和藍(lán)牙模塊之間采用UART方式進(jìn)行通信。DSP使用的控制信號除了異步串行通信收發(fā)信號SCIRXD和SCITXD外,還有4個控制信號,分別與藍(lán)牙模塊的LNK、CLR、RTS和CTS引腳相連。其中,LNK腳用于指示藍(lán)牙主機和從機連接是否建立,地面設(shè)備PC機為藍(lán)牙主機,DSP作為藍(lán)牙從機;CLR腳用于切換藍(lán)牙模塊的工作模式,包括參數(shù)設(shè)置模式和數(shù)據(jù)傳輸模式;RTS和CTS腳為“請求發(fā)送”和“清除發(fā)送”引腳,用于實現(xiàn)DSP和藍(lán)牙模塊之間的對話,使數(shù)據(jù)正常傳輸。

藍(lán)牙模塊的SLEEP引腳,既可以使藍(lán)牙模塊在休眠和喚醒狀態(tài)間切換,也可以用于清除藍(lán)牙模塊內(nèi)嵌芯片記憶的配對主機地址。這些功能的實現(xiàn)由按鍵控制,通過區(qū)別按鍵的時長加以區(qū)分所需實現(xiàn)的功能。藍(lán)牙模塊的復(fù)位信號RESET輸入低電平脈沖時有效,而且要求脈沖寬度大于5 ms。

3.2.2 紅外模塊設(shè)計

紅外模塊采用HP公司的紅外收發(fā)器芯片HSDL_1001和紅外編解碼器芯片HSDL_7001,二者均遵循IrDA 1.O協(xié)議。紅外信號的收發(fā)使用PWM方案,采用RZI編碼調(diào)制解調(diào),調(diào)制脈沖寬度為3/16位,調(diào)制頻率為38 kHz。由于硬件接口的限制,嵌入式系統(tǒng)中紅外通信的速率為9 600~ll5200 bps。紅外數(shù)據(jù)的傳輸以幀為基本單位,傳輸過程中采用1 6位的CRC碼進(jìn)行數(shù)據(jù)校驗。

系統(tǒng)采用Maxim公司的芯片MAX3110作為DSP的SPI接口和HSDL_7001的UART接口之間的轉(zhuǎn)換芯片。MAX3110和HSDL_7001均使用外部無緣晶體振蕩電路供電,所用的晶振大小分別為1.843 2 MHz和3.686 4 MHz。需要下載的數(shù)據(jù),首先經(jīng)過紅外編解碼器編碼,再通過紅外收發(fā)器上集成的發(fā)光二極管以紅外光信號的形式向PC機發(fā)送。

4 系統(tǒng)軟件設(shè)計

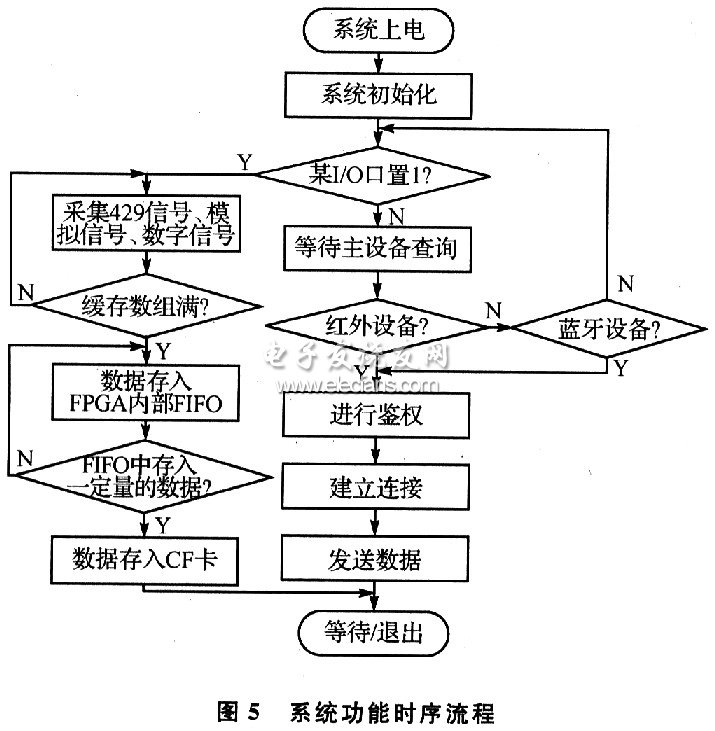

系統(tǒng)的功能時序流程如圖5所示。DSP部分程序用C語言編寫,結(jié)合硬件電路對數(shù)據(jù)采集、數(shù)據(jù)傳輸進(jìn)行處理和控制。主要的中斷應(yīng)用有

ARlNC429信號采集中斷和紅外通信請求中斷。系統(tǒng)的工作流程以時序控制流程為主線。系統(tǒng)初始化之后,進(jìn)行任務(wù)選擇與執(zhí)行。若特定的I/O口置1,則進(jìn)入數(shù)據(jù)存儲程序,采集數(shù)據(jù)并存至CF卡;若I/O口置O,則進(jìn)入數(shù)據(jù)下載程序,等待主設(shè)備的連接請求,鑒權(quán)并建立相應(yīng)的連接,讀取CF卡數(shù)據(jù),并通過無線通信模塊向主設(shè)備發(fā)送。

結(jié)語

該系統(tǒng)利用DSP與FPGA協(xié)同控制方式實現(xiàn)數(shù)據(jù)的采集和存儲,利用紅外和藍(lán)牙模塊實現(xiàn)數(shù)據(jù)的無線下載;用紅外和藍(lán)牙代替有線線纜和插拔存儲卡等傳統(tǒng)數(shù)據(jù)下載方式,操作方便,避免了傳統(tǒng)方式可能造成的機械故障。