在信號鏈中使用ADC的根本目的,是在設(shè)計中以及最終在系統(tǒng)層次上實現(xiàn)最佳的動態(tài)范圍、噪聲特性(信噪比或SNR)和線性度(無雜散動態(tài)范圍或SFDR)。本文首先將闡述緩沖型與無緩沖型ADC的區(qū)別(優(yōu)缺點),然后討論原始無緩沖ADC內(nèi)部采樣網(wǎng)絡(luò)的反沖(一般稱為“電荷注入”),以及如何驅(qū)動無緩沖型ADC。最后,本文將說明構(gòu)建適當(dāng)抗混疊濾波器(AAF)所需的特殊模擬輸入接口設(shè)計要求,并給出一個范例。

我是否需要使用無緩沖型ADC?

緩沖型與無緩沖型ADC之間存在很大差異。緩沖型的優(yōu)點比較直觀,緩沖器將模擬接口電路與內(nèi)部開關(guān)電容采樣工作隔離開來,這就為ADC驅(qū)動器提供一個受控的輸入阻抗,瞬態(tài)效應(yīng)(一般稱為“反沖”)大大減弱。反沖或電荷注入是指當(dāng)ADC的內(nèi)部采樣開關(guān)斷開和閉合時,殘余電荷被送回到輸入信號中。

緩沖器帶來的這些好處可以在一定程度上簡化模擬接口設(shè)計,并且支持更高的輸入帶寬。然而,緩沖器的缺點也是存在的,盡管不太明顯。緩沖器通常需要較高的電源電壓,這會帶來額外的電源設(shè)計問題。ADC的噪聲和線性度也會受到影響,因此在電源方面,整體ADC設(shè)計大受影響。

在系統(tǒng)層次上,多數(shù)高速ADC的輸入采用放大器驅(qū)動。因此,在常見的信號鏈應(yīng)用中,緩沖器的電源有點多余。如果模擬接口電路和放大器設(shè)置為直接驅(qū)動采樣網(wǎng)絡(luò),而不使用緩沖器,則整個系統(tǒng)可以得到更好的優(yōu)化。問題是如何處理提供給驅(qū)動器電路的原始采樣電容的電荷(反沖)。

去掉緩沖器是多數(shù)系統(tǒng)設(shè)計師傾向做出的妥協(xié),因為可以額外節(jié)省功耗,但這樣一來,設(shè)計師必須面對一個棘手的任務(wù)——在轉(zhuǎn)換器與放大器之間提供一個可以實現(xiàn)的模擬接口。不用怕,因為即使無緩沖型轉(zhuǎn)換器的阻抗隨著采樣狀態(tài)(跟蹤模式與保持模式)和中頻頻率而變化,但該設(shè)計在最終應(yīng)用中仍將有效。您只需在利用無緩沖型ADC進(jìn)行設(shè)計時,認(rèn)真遵守一些注意事項。

了解抗混疊問題

ADC是信號鏈中的一項值得注意的模擬功能。無論所選ADC是緩沖型還是無緩沖型,驅(qū)動放大器與轉(zhuǎn)換器之間都需要一個適當(dāng)?shù)腁AF設(shè)計,用以降低寬帶噪聲和雜散。相比于傳統(tǒng)線性模塊(如混頻器和放大器等),ADC具有一些非常獨特的特性,其中之一是混疊。

混疊是指所有頻率成分“折疊”到基帶或第一奈奎斯特區(qū)。如果在所需信號帶寬(目標(biāo)奈奎斯特區(qū))外有不需要的雜散和噪聲,混疊就會造成問題。為此,一般會在ADC輸入端之前使用一個抗混疊濾波器。驅(qū)動放大器、抗混疊濾波器和ADC內(nèi)部的采樣網(wǎng)絡(luò)構(gòu)成一個緊密交織的系統(tǒng),可以對其進(jìn)行優(yōu)化以有效滿足大多數(shù)應(yīng)用的要求,您只需要知道一些訣竅就能成功。

第一步是確定抗混疊濾波器的要求,包括阻帶抑制曲線和通帶紋波要求。這些要求一般由帶外成分決定,必須防止帶外成分混疊到目標(biāo)頻段內(nèi)。目標(biāo)是確定可以實現(xiàn)并且仍能滿足要求的最小濾波器階數(shù),使元件數(shù)量最少,整體系統(tǒng)復(fù)雜度最低。為便于討論,假設(shè)使用無源LC濾波器。

一旦確定濾波器后,下一步便是設(shè)置模擬接口的阻抗。較低的阻抗對ADC有利,因為它給采樣網(wǎng)絡(luò)帶來的驅(qū)動阻抗較低,但不利于驅(qū)動放大器。這一點在設(shè)計中很關(guān)鍵。多數(shù)驅(qū)動放大器設(shè)置為驅(qū)動大約75 Ω的阻抗(單端),這是AAF設(shè)計的一個良好開端。

無論何種階數(shù)或類型,LC濾波器在ADC輸入端應(yīng)有一個并聯(lián)電容,此電容對濾波器與ADC的接口至關(guān)重要。該并聯(lián)電容充當(dāng)?shù)谝痪彌_器,緩沖來自無緩沖型ADC的反沖電荷。電容越大,則對電荷反沖的抑制越好,ADC驅(qū)動性能也就越高。記住,可以在AAF中調(diào)整阻抗,以優(yōu)化ADC性能和/或放大器性能。

影響LC濾波器驅(qū)動無緩沖開關(guān)電容高速ADC的另一個因素是濾波器的輸出阻抗Q。濾波器驅(qū)動ADC的采樣網(wǎng)絡(luò),所以,該輸出阻抗是ADC驅(qū)動阻抗的一部分。如果濾波器驅(qū)動網(wǎng)絡(luò)的Q太高,則ADC內(nèi)部采樣網(wǎng)絡(luò)的電荷反沖會在模擬輸入端引起響鈴振蕩。這種振蕩如果沒有在一個時鐘周期內(nèi)消失,就會造成額外的失真。

多數(shù)ADC模擬接口設(shè)計實際上是集總元件網(wǎng)絡(luò),而不是匹配系統(tǒng)。這種“中頻片”成為“匹配”與集總元件分析——轉(zhuǎn)換器的“可用”帶寬、并聯(lián)電容要求、去Q、波長和走線長度限制——之間的過渡。了解這些變量后,我們將有多種不同的AAF權(quán)衡和設(shè)計方法可以考慮。

AAF設(shè)計示例

大多數(shù)模擬接口可以利用驅(qū)動放大器之后的LC抗混疊濾波器來設(shè)計。輸入頻率使得系統(tǒng)可以作為集總元件電路進(jìn)行分析,而不涉及到阻抗匹配問題。只要信號路徑距離小于模擬輸入波長的1/10,集總元件模型就是充分有效的。即使信號路徑距離較長,通常也不要求阻抗匹配。然而,較長的信號路徑距離會帶來其他問題。

板走線路徑會將寄生電感和電容引入LC濾波器。這可以通過濾波器設(shè)計來處理,即改變?yōu)V波器元件值,以補(bǔ)償印刷電路板(PCB)的寄生效應(yīng)。關(guān)鍵問題是要讓抗混疊濾波器的最終并聯(lián)電容盡可能靠近ADC輸入端,從而使采樣網(wǎng)絡(luò)中的電感最小,以免因為模擬接口的時鐘性質(zhì)而引起響鈴振蕩。

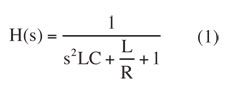

為了說明這一點,考慮一個簡單的二階LC AAF設(shè)計,它包括一個串聯(lián)電感、并聯(lián)電容和端接電阻,因而該濾波器部分的傳遞函數(shù)如下:

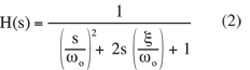

其通用二階形式為:

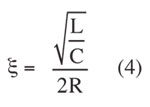

如果讓這兩個傳遞函數(shù)的系數(shù)相等,可以得到:

并且:

對于大多數(shù)應(yīng)用,帶寬和濾波器類型是固定的設(shè)計參數(shù)(本例為巴特沃茲型)。單憑這兩個參數(shù)并不能確定濾波器設(shè)計,最終的決定參數(shù)是阻抗水平,即濾波器的阻抗可以調(diào)整,以便有利于ADC驅(qū)動或放大器負(fù)載。

假設(shè)帶寬為200 MHz,濾波器類型為二階巴特沃茲響應(yīng)。放大器設(shè)計驅(qū)動150 Ω負(fù)載,因此R = 150 Ω、L = 155 nH、C = 4 pF。然而,如果4 pF并聯(lián)電容不足以緩沖電荷反沖,則可以加大放大器的負(fù)載為代價,降低AAF阻抗,反之亦然。

從實際考慮,AAF設(shè)計還存在其他限制,如電路板物理布局布線等。例如,有時可能無法讓放大器與ADC靠得非常近,這樣一來,電路板布線就成為AAF設(shè)計的一部分。走線路徑會增加額外的串聯(lián)電感和電容,從而影響濾波器的響應(yīng)。

這可以通過選擇適當(dāng)?shù)脑硖幚恚唇档碗姼兄担岆娐钒遄呔€來補(bǔ)償實際的AAF電感值。這樣,設(shè)計的最重要部分就是在不違背制造規(guī)則的前提下,讓并聯(lián)電容盡可能靠近ADC輸入端,因為該電容要“緩沖”電荷反沖(參見下圖)。

長走線的等效電路實際上會反映一些寄生電感。考慮上面的等效電路,它看起來像是一個不同的RLC模型。因此,這里的目標(biāo)是盡量降低電路中的額外走線電感“L”,從而使可能發(fā)生的反沖響鈴振蕩最小,以免產(chǎn)生失真和/或不同的濾波器曲線。這只是一個例子,說明放大器、AAF和ADC需要緊密配合才能使信號鏈有效工作。

結(jié)束語

高速ADC無論采用緩沖式架構(gòu),還是采用無緩沖式架構(gòu),都有各自的理由。無緩沖型高速ADC可能需要更復(fù)雜的模擬接口設(shè)計,但就功耗而言,它可以給整體系統(tǒng)效率帶來很大的好處。無緩沖型ADC設(shè)計要求將模擬接口設(shè)計與采樣網(wǎng)絡(luò)作為一個整體考慮,包括放大器、AAF和ADC的內(nèi)部采樣網(wǎng)絡(luò)。對于大多數(shù)應(yīng)用,只要認(rèn)真考慮上述變量,就可以圓滿完成任務(wù)。