電路板已經成為當今電子產品的重要組成部分,隨著電子技術及印制板制造技術的發(fā)展,現(xiàn)代電子產品日趨復雜,印制電路板的密度日趨增加,隨之而來的是印制板的測試及修理也愈加困難。為了提高印制電路板的檢測及維修的自動化程度,設計電路板的自動測試系統(tǒng)是非常必要的。

目前,印制電路板自動測試技術發(fā)展迅速,印制板在線測試系統(tǒng)(ATE)廣泛應用于印制板光板及各種產品的印制電路板的生產、檢測和維修等環(huán)節(jié)。由于用戶的測試要求、測試對象各不相同,其具體性能(或功能)、測試原理及測試方法也各不相同,它需要量體裁衣、單臺定制才能滿足用戶的要求,并且系統(tǒng)的通用性較差,資源可重復利用率低。鑒于上述狀況,本文設計了一款較為通用的自動測試系統(tǒng),用來測試電路板是否工作正常,實現(xiàn)了對多款電路板的在線測試。

1 系統(tǒng)的總體結構

1.1 系統(tǒng)總體考慮

本系統(tǒng)的主要目的是測試電路板是否工作正常,是通過對電路板上關鍵信號進行測試來達到的。因此,本系統(tǒng)的任務就是對電路板上的關鍵信號進行采集,通過PC 端的軟件進行分析得出測試結果。系統(tǒng)分為針床、信號采集和傳輸模塊、測試軟件3個部分。作為一個通用的測試系統(tǒng),在3 個部分中均考慮了較強的通用性。

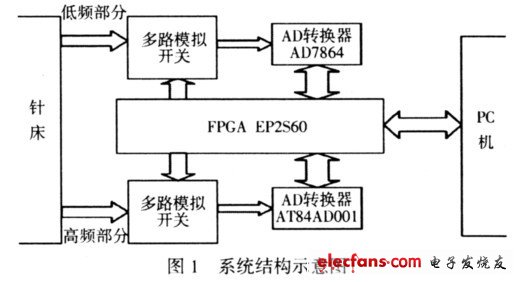

1.2 系統(tǒng)結構

本自動測試系統(tǒng)的結構框圖見圖1。系統(tǒng)的工作原理是:通過針床將待測信號導出,F(xiàn)PGA 通過控制多路模擬開關將待測信號采集進來,將數(shù)據(jù)通過相應協(xié)議傳送到PC 機,用自動測試軟件測試各個信號是否正常。

由于待測信號的頻率相差較大,有直流信號,也有頻率高于103 MHz 的脈沖信號,以及在其間的多種頻率的信號,因此本系統(tǒng)采用低頻和高頻2 組信號采樣電路,來適應不同信號采集的需要。

1.3 主要芯片介紹

本系統(tǒng)中用到的主要芯片有:主芯片EP2S63,AD 采樣芯片AD7864 和AT84AD331。以下對這3 種芯片進行簡要介紹:

EP2S63 是ALTERA 公司的Strati 系列的FPGA,該系列的FPGA 采用先進的93 nm 生產工藝;將FPGA 性能推向了新高度,該系列是業(yè)界最快、密度最高的FPGA。EP2S63 擁有多達84個專用LVDS 差分邏輯接收通道,每個LVDS 通道數(shù)據(jù)傳輸速率最高達1 Gb/s。其內部具有專門的高速數(shù)字鎖相環(huán)電路,能夠產生可供ADC 電路使用的時鐘信號。

AD7864 是一種較低速、低功耗、可以4 通道同時采樣的12b A/D轉換器。它擁有12 位A/D轉換器,可同時采樣4 個輸入通道,并具有4 個采樣、保持放大器;單電源供電(+5 V),多個轉換電壓范圍, 對于每一個模擬輸入通道均有過壓保護電路;4 通道同時工作時,最大采樣率為133 kHz。

AT84AD331 是Atmel 公司生產的高速采集芯片。該器件集成了兩路(I 和Q)獨立的ADC,具有8 b 轉換精度,每個通道具有l Gs/s 的采樣率,在交錯模式下采樣率達2 Gs/s。本芯片基于高速應用場合的要求,模擬輸入、數(shù)字時鐘輸入、數(shù)字時鐘輸出、數(shù)據(jù)輸出,同步時鐘輸出都采用差分方式。數(shù)據(jù)輸出采用LVDS標準,其傳輸率可達1 Gb/s,使用其內部的多路分離器,可以降低輸出數(shù)據(jù)率,也可以方便地與多種類型的高速FPGA 直接相連。

采用1∶2 模式時,輸出數(shù)據(jù)速率降為533 Mb/s,可以滿足多數(shù)FPGA 接收數(shù)據(jù)的要求。

2 系統(tǒng)詳細設計

2.1 針床設計

針床是電路板測試系統(tǒng)的重要部件,是電路板信號導出的平臺。針床的通用性較差,一般是每種電路板對應一個特定的針床,這使系統(tǒng)的通用性受到很大的限制。為使針床具有一定的通用性,本系統(tǒng)中對針床的相關部件進行了一些改進:

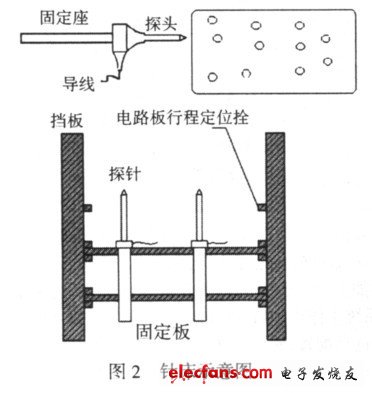

(1)探針設計。探針見圖2 a。本探針是以目前市場上的探針為基礎、自行設計的內含彈簧的探針,易于固定,信號導出方便:

探針的一端為探頭,是與電路板接觸,并導出信號的部分;另一端是固定座,是絕緣體,中空,內含彈簧,使探頭能夠伸縮;中間為信號的導出端子。為減少各個信號間的干擾,導線均采用屏蔽線。為適應不同信號要求,按粗細和允許的信號帶寬要求探針分為多種型號,使用時根據(jù)需要對探針型號進行選擇。

(2)探針的固定:在本系統(tǒng)的針床上,探針的固定是采用兩塊相同的探針固定板和4 塊擋板組成,固定板和探針的固定示意圖見圖2 b 和圖2c:固定板的大小與待測板相同,板上固定孔位置需根據(jù)電路板的技術文件來確定,孔的大小需根據(jù)選取探針的型號來決定。擋板可以在整個針床的底座上進行移動調整,以適應不同尺寸電路板的固定要求;擋板的寬度,前后兩個為233 mm,左右兩個為73 mm。

2.2 信號采集

電路板上輸出的待測信號主要有三類:電源信號、脈沖數(shù)字信號、電平變換信號。此外還有一些頻率較高的模擬信號,如音視頻信號,此類信號一般不作為關鍵測試信號,若需測試時可按高頻信號進行采集。其中電源信號和電平變換信號均可視為直流信號來采集,用AD7864 完成采集。而脈沖數(shù)字信號的頻率較高,動輒就幾十兆赫茲甚至上百兆赫茲,需要用高速的AD(本系統(tǒng)中用的是AT84AD331) 來進行采集,并且需要對頻率進行測量。因此本系統(tǒng)信號采集分為低頻和高頻兩個部分,下面分別敘述:

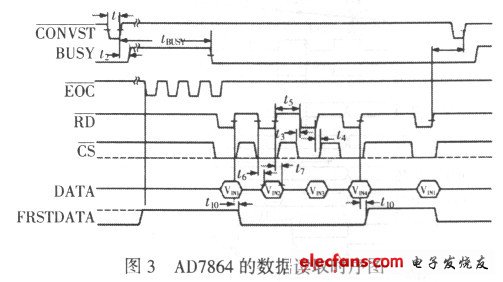

(1)低頻部分。本部分主要采集的是電源信號和電平變換信號,采用AD7864 作為采集芯片。AD7864 具有片內時鐘、讀寫允許邏輯、多種通道選擇方式以及內部精確的2。5 V 參考電壓,這使得其與高速處理器的接口變得非常簡單。AD7864 轉換后的數(shù)據(jù)讀取采用轉換后讀取數(shù)據(jù)的方式,其讀取時序見圖3。

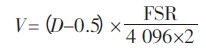

采集到的數(shù)據(jù)為D3~D11 共12 位,需根據(jù)采集到的數(shù)據(jù)來計算電壓值,計算公式如下:

當D11 位為3 時,電壓為正值,計算公式為:

當D11 位為1 時,電壓為負值,計算公式為:

以上兩式中D 為讀取的12 位數(shù)據(jù),FSR 為AD7864 的測量范圍,本例中為23 V(測量范圍為V)。

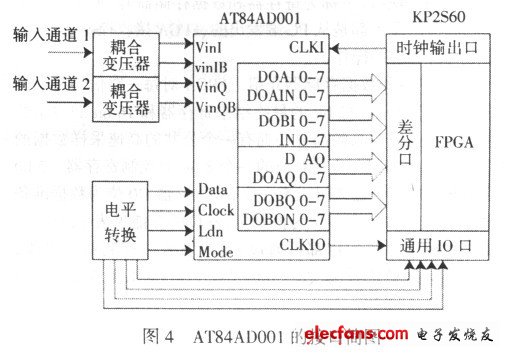

(2)高頻部分。主要是對脈沖數(shù)字信號的采集,包括頻率測量和信號采集兩個部分。脈沖數(shù)字信號的頻率是確定電路板是否工作正常的重要參數(shù),因此確定脈沖信號的頻率是否正常是本測試系統(tǒng)的必要工作。本系統(tǒng)是將待測信號接入FPGA 與53MHz 的高精度時鐘同時開始計數(shù),一段時間后,通過兩個信號的計數(shù)值來計算脈沖信號頻率的。信號采集是以AT84AD331 作為采集芯片。AT84AD331 與EP2S63 的連接見圖4。

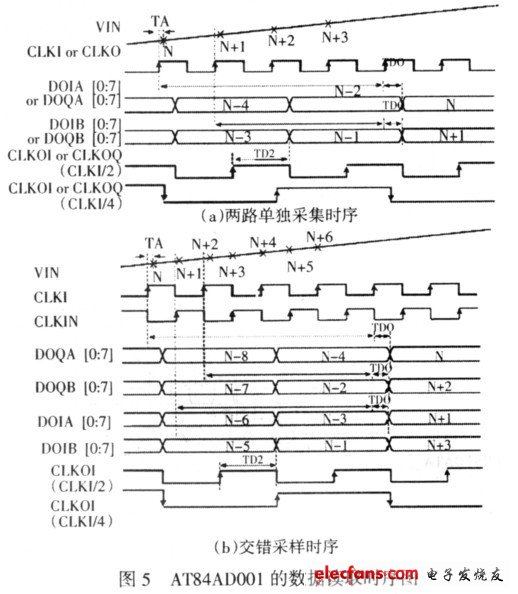

AT84AD331 可以配置成I 路和Q 路單獨使用,此時可以同時采集兩路信號,最高采樣率為1 Gs/s;也可以配置成I和Q路的交錯采樣,此時只能采集1 路信號,等效采樣率為2 Gs/s,使用時可以根據(jù)需要對該芯片進行在線配置。FPGA 對AT84AD331數(shù)據(jù)讀取時序見圖5。

由于AT84AD331 輸入信號為差分信號,且信號峰峰值要求不超過533 mV。電路板上的待測信號都是單端的并且峰峰值一般在4 V~5 V 之間。本系統(tǒng)中采用了13∶1 的變壓器耦合輸入方式,可以完成單端信號到差分信號的轉換,并且使信號電壓滿足要求。

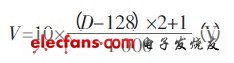

在FPGA 內部完成對LVDS 信號的讀取、組合、排序以及存儲等操作。一般情況下存儲的采樣點的值在1 333 以內,然后對這些采樣點的值進行計算,可以得到實際電壓值,計算公式如下:

2.3 數(shù)據(jù)傳輸和控制協(xié)議

系統(tǒng)中待測信號較多,低頻和高頻部分分別是32 個,而數(shù)據(jù)采集芯片都只有一個,各個信號都是由FPGA 控制模擬開關分時地進行采集的。為使各個通道的數(shù)據(jù)存儲、傳輸和控制有序地進行,在FPGA 中為每一個信號都設置了工作狀態(tài)控制模塊和數(shù)據(jù)存儲模塊(以下稱為寄存器和數(shù)據(jù)存儲器)。本系統(tǒng)中所有控制過程的命令都是從PC 端發(fā)出的,F(xiàn)PGA 接收控制指令后,按指令進行相應的操作。

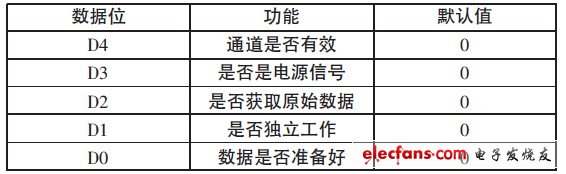

(1)寄存器和數(shù)據(jù)存儲器介紹。FPGA 對每一路信號都設有5 bit 的控制寄存器、12 bit 的最終結果寄存器和16 bit 的原始數(shù)據(jù)存儲器。此外在高頻部分還擁有一個公共的高速采樣數(shù)據(jù)的存儲器,大小為1 kB,及其對應的一個8 bit 的控制寄存器。5 bit的控制寄存器每個通道只設有一個,該寄存器D3 位為數(shù)據(jù)準備好標志(1 有效),其余4 位為控制位,各位的功能見表1,每一位都是1 為肯定,每一位都可通過PC 端發(fā)來的控制指令更改,F(xiàn)PGA 只能向D3 位寫1 ,表示數(shù)據(jù)已經準備好。上電或復位后該寄存器值為33333B。

表1 5bit控制寄存器的位功能

12 bit 的最終結果寄存器每個通道也只設有一個,該寄存器的值是向PC 機發(fā)送的最終結果。該寄存器的數(shù)據(jù)在低頻和高頻部分,存放的數(shù)據(jù)不同:低頻部分存放的是13 次采樣結果的平均值,高頻部分存放的是計算后的頻率值。

16 bit 的原始數(shù)據(jù)存儲器,其低頻和高頻部分的數(shù)量是不相同的:高頻部分一般是2 個,分別用來存放標準和待測時鐘的計數(shù)值;低頻部分為13 個,用來存放13 個采樣點的值,12 bit 的最終結果寄存器的值是根據(jù)這13 個數(shù)據(jù)的平均值。

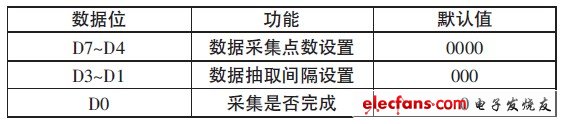

高速采樣數(shù)據(jù)存儲器是高頻部分的32 路共有的,由于波形采樣的數(shù)據(jù)量比較大,本系統(tǒng)設計時在同一時刻只允許采樣1 路信號,采樣點數(shù)可以設定(最多為1 K),待這些數(shù)據(jù)全部發(fā)送出后,才可以開始下一次采集。對應的控制寄存器的位功能見表2。

表2 高速采樣控制寄存器的位功能

其中D7~D4 為數(shù)據(jù)采集的點數(shù)設置,3333B 表示64 個,1111 表示1 324 個,步進為64。D3~D1 為數(shù)據(jù)抽取的間隔設置,333 表示抽取間隔為3,全部數(shù)據(jù)有效;111 表示抽取間隔為28,即每隔28 個點抽取一個點,步進為4。設置這幾位的目的是為了適應信號頻率的要求,防止采集數(shù)據(jù)不足一周期的狀況發(fā)生。D3位為標志位,功能和操作與5 bit 的寄存器的對應位完全相同。本寄存器分高4 位和低4 位兩次設置。

(2)控制命令介紹。本系統(tǒng)中的控制命令都是由PC 機發(fā)出的,共8 個命令:選擇控制寄存器1(低頻部分);選擇控制寄存器2(高頻部分);選擇控制寄存器3(高速采樣部分);寫控制寄存器數(shù)據(jù);讀取數(shù)據(jù)1(低頻部分);讀取數(shù)據(jù)2(高頻部分的頻率值);讀取波形采樣數(shù)據(jù);開始/停止測試。

PC 機發(fā)送的控制字都是8 位的,其中高3 位為控制命令字,用來區(qū)分8 個命令,低5 位為輔助功能,具體見表3。FPGA 接收到主機發(fā)來的命令信號后,按命令執(zhí)行相應的操作。

表3 控制命令的位功能

(3) 數(shù)據(jù)傳輸過程簡述。系統(tǒng)中與PC 機的通信采用的是RS232 接口,數(shù)據(jù)的傳輸完全符合RS232 標準。現(xiàn)將數(shù)據(jù)的傳輸過程簡述如下:系統(tǒng)啟動后,首先進行自檢,以確定系統(tǒng)工作是否正常;系統(tǒng)工作正常后,PC 機通過測試軟件對FPGA 內部的各個寄存器進行配置;然后發(fā)送開始命令,開始對有效的各個信號進行采集;采集完成后向PC 機返回信息,PC 機根據(jù)需要通過測試軟件從FPGA 讀取相應通道的數(shù)據(jù),將數(shù)據(jù)計算后與標準值進行比較并得出測試結果。也可以根據(jù)需要讀取某一通道的原始數(shù)據(jù)以及采集某一通道信號的波形。在FPGA 內部還擁有關鍵信號(電源)的監(jiān)測:任何一路電源信號不正常則重新進行采集,若3 次采集結果均不正常則直接關閉電路板的供電電源,避免損壞電路板,并向PC 發(fā)送電源不正常的消息,并給出出現(xiàn)異常的通道號。

2.4 測試軟件設計

測試軟件是本系統(tǒng)的人機接口部分,在本系統(tǒng)中需包括如下功能:設置各個通道信號的參數(shù)值,并能保存和讀取設置的參數(shù);顯示各個通道的信號測試結果,并能夠保存;能夠采集并顯示某一通道的信號波形。

擁有上述功能即可進行測試,至于界面方面可以根據(jù)個人的習慣和愛好進行設計。本系統(tǒng)的測試軟件實現(xiàn)了上述的功能,至于界面并未追求美觀,其功能大致如下:

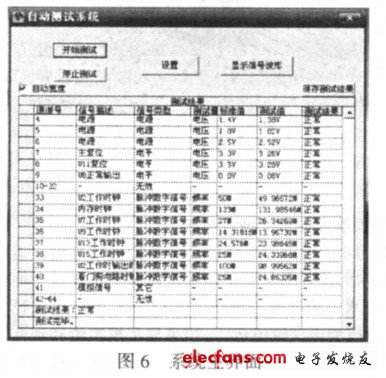

系統(tǒng)主界面見圖6,除了“開始停止”鍵外,有設置、查看信號波形和保存結果3 個按鈕,還有一個結果的輸出窗口。

設置窗口見圖7,本窗口中可以設置每一路信號的屬性,也可以直接調出以前保存的設置,設置完成后即可按該設置進行測試。設置完成后,可以將本次的設置保存成文件,以便下次直接調出。

查看信號波形的設置和顯示窗口見圖8。

3 結語

本文設計的電路板自動測試系統(tǒng)通用性強、使用方便、工作穩(wěn)定,可以應用于多款電路板的測試;對不同的電路板,只需制作2 塊對應的固定板即可。系統(tǒng)已經對123 mm×133 mm 和253mm×213 mm 兩款電路板進行測試,結果令人滿意。該系統(tǒng)具有一定的推廣價值。