中心議題:

- 同步整流基礎(chǔ)知識

- 優(yōu)化同步整流MOSFET

解決方案:

1. 引言

電源轉(zhuǎn)換器的封裝密度日益提高和節(jié)能標(biāo)準(zhǔn)越來越嚴(yán)格,要求不斷提高電源級的能效。隔離式電源轉(zhuǎn)換器的次級整流產(chǎn)生的嚴(yán)重的二極管正向損耗是主要的損耗,因此,只有利用同步整流(SR)才可能達(dá)到這些標(biāo)準(zhǔn)要求的能效水平。用MOSFET替代二極管引發(fā)了新的挑戰(zhàn)——優(yōu)化系統(tǒng)能效和控制電壓過沖。本應(yīng)用筆記介紹了通過利用英飛凌OptiMOS™3解決方案的優(yōu)化表(適用于30 V、40 V、60 V、75 V、80 V、100 V、120 V和150 V等應(yīng)用)幫助選擇最佳MOSFET的方法。

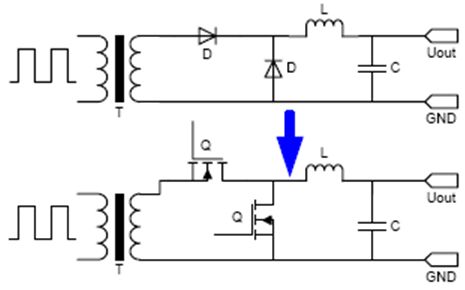

圖1. 二極管整流與同步整流之比較

. 同步整流基礎(chǔ)知識

要選擇最優(yōu)的MOSFET來實(shí)現(xiàn)同步整流,必須充分理解MOSFET的功耗產(chǎn)生機(jī)制。首先,必須區(qū)分開隨負(fù)載而變化的導(dǎo)通損耗與基本保持不變的開關(guān)損耗。導(dǎo)通損耗取決于MOSFET的RDS(on)和內(nèi)部體二極管的正向電壓VSD。隨著輸出電流的提高,導(dǎo)通損耗(RDS(on)損耗)也會(huì)相應(yīng)地增加。為確保兩個(gè)SR MOSFET之間互鎖,以避免出現(xiàn)直通電流,必須實(shí)現(xiàn)一定的死區(qū)時(shí)間。因此,在開啟一次側(cè)之前,必須關(guān)斷相應(yīng)的MOSFET。由于該MOSFET正在導(dǎo)通全部續(xù)流電流,因此,這些電流將不得不從MOSFET溝道轉(zhuǎn)而流向內(nèi)部的體二極管,并由此產(chǎn)生額外的體二極管損耗。體二極管的導(dǎo)通時(shí)間很短,僅為50 ns至100 ns左右,因而,當(dāng)輸出電壓比體二極管的正向電壓高得多時(shí),這些損耗可以忽略不計(jì)。

取決于電源轉(zhuǎn)換器的開關(guān)頻率和輸出負(fù)載,開關(guān)損耗對MOSFET的總功耗有很大影響。MOSFET開啟時(shí),必須對柵極進(jìn)行充電,以產(chǎn)生柵極電荷Qg。MOSFET關(guān)斷時(shí),則必須將柵極中的電荷放電至源極,這就意味著Qg將消散在柵極電阻和柵極驅(qū)動(dòng)器中。對于特定MOSFET技術(shù),柵極驅(qū)動(dòng)損耗會(huì)隨著RDS(on)的降低而增加,因?yàn)楣杵酱驫g就越多。

在總開關(guān)損耗中占很大比例的另一種損耗與MOSFET的輸出電容Coss和反向恢復(fù)電荷Qrr有關(guān)。MOSFET關(guān)斷時(shí),必須將Qrr移走,并且必須將輸出電容充電至次級變壓器電壓。這個(gè)過程會(huì)導(dǎo)致反向電流峰值,該電流將耦合到交換環(huán)路的電感中。所以,這些電量將被轉(zhuǎn)移至MOSFET的輸出電容,加上之前存儲的電量,將由此產(chǎn)生電壓尖峰。這些電量將觸發(fā)LC振蕩電路。LC振蕩電路的性能取決于印刷電路板的感應(yīng)系數(shù)和MOSFET的輸出電容Coss。LC電路的寄生串聯(lián)電阻將減弱振蕩。由于這種在關(guān)斷過程中產(chǎn)生的感應(yīng)電量直接取決于MOSFET Coss(相應(yīng)地,當(dāng)輸出電容被充電至次級變壓器電壓時(shí),則為輸出電荷Qoss),因此,總Coss決定了容性關(guān)斷損耗。對于柵極電荷也是如此,Qoss會(huì)隨著RDS(on)的降低而增加。因此,總是能找到可以實(shí)現(xiàn)最高效率的導(dǎo)通損耗與開關(guān)損耗之間的平衡點(diǎn)。

大致上,對于OptiMOS™3產(chǎn)品而言,Qrr可以忽略不計(jì),因?yàn)槠鋵偣牡挠绊懳⒑跗湮ⅰT谶@種情況下,Qrr僅被視為MOSFET體二極管的反向恢復(fù)電荷,而數(shù)據(jù)手冊中的Qrr則是按照J(rèn)EDEC標(biāo)準(zhǔn)測得的,因此,除體二極管Qrr之外,還包含MOSFET的部分輸出電荷。此外,其他因素也會(huì)導(dǎo)致應(yīng)用中的實(shí)際Qrr值低于數(shù)據(jù)手冊所提供的Qrr值。數(shù)據(jù)手冊中的值是在對體二極管施以允許的最高M(jìn)OSFET漏極電流、體二極管導(dǎo)通時(shí)間長達(dá)500 μs并且di/dt值固定為100A/μs的條件下測得的。在實(shí)際應(yīng)用中,通常電流僅為最高漏極電流的三分之一左右甚至更低,體二極管導(dǎo)通時(shí)間在20ns至100ns范圍內(nèi),并且di/dt可能高達(dá)800A/μs。

3. 優(yōu)化同步整流MOSFET

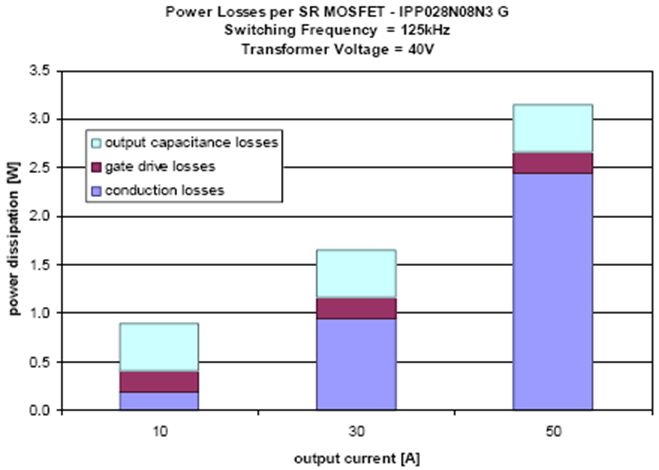

要優(yōu)化SR MOSFET的效率,必須找到開關(guān)損耗與導(dǎo)通損耗之間的最佳平衡點(diǎn)。在輕負(fù)載條件下,RDS(on)導(dǎo)通損耗占總功耗的比例極低。在這種情況下,在整個(gè)負(fù)載范圍內(nèi)基本保持不變的開關(guān)損耗是主要損耗。但是,當(dāng)輸出電流較高時(shí),導(dǎo)通損耗則成為最主要的損耗,其占總功耗的比例也最高,請參見圖2。

圖2. 功耗構(gòu)成與輸出電流的關(guān)系

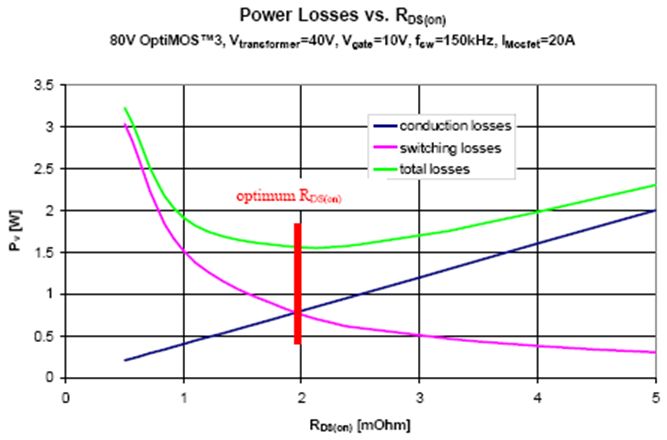

在選擇最適當(dāng)?shù)腗OSFET時(shí),必須特別注意RDS(on) 的取值范圍,如圖3所示。當(dāng)RDS(on)超出最優(yōu)值時(shí),總功耗將隨RDS(on)的提高而線性增加。但當(dāng)RDS(on) 降至低于最優(yōu)值時(shí),總功耗也會(huì)因輸出電容的快速增加而急劇上升。此外,在圖3中可以看出,可實(shí)現(xiàn)最低功耗的RDS(on)值范圍相當(dāng)寬。在本例中,當(dāng)RDS(on)在1毫歐姆至3毫歐姆范圍內(nèi)時(shí),總功耗始終大致相同。但是,在此范圍之外,RDS(on)僅下降0.5毫歐姆,便會(huì)令總功耗提高一倍,從而嚴(yán)重降低電源轉(zhuǎn)換器的效率。

圖3. 功耗與RDS(on)值的關(guān)系

對于優(yōu)化SR,另一個(gè)重要的問題是正確選擇MOSFET封裝。只要將TO-220封裝替換為SuperSO8封裝即可實(shí)現(xiàn)效率提升。這是因?yàn)椋琒uperSO8封裝的電阻占總RDS(on)的比例更低。在降低RDS(on)的同時(shí),保持輸出電容不變,能夠降低FOMQoss。FOMQoss是特定MOSFET解決方案的性能指標(biāo)(FOMQoss= RDS(on) * Qoss)。因此,降低FOMQoss可以降低開關(guān)損耗,從而提高系統(tǒng)能效。

4. 應(yīng)當(dāng)按何種負(fù)載電流優(yōu)化MOSFET?

要在整個(gè)負(fù)載范圍內(nèi)實(shí)現(xiàn)均衡的效率,必須借助四象限SR器件優(yōu)化表對MOSFET電流做出合理的選擇。采用滿負(fù)載優(yōu)化,可以在輸出電流較高時(shí)實(shí)現(xiàn)良好的效率。但是,當(dāng)負(fù)載較低時(shí),這種方法會(huì)大大降低效率,并且所需并聯(lián)MOSFET的數(shù)量將多得不能接受。因此,必須找到最優(yōu)MOSFET電流,以在整個(gè)輸出電流范圍內(nèi)實(shí)現(xiàn)相對恒定的效率值。

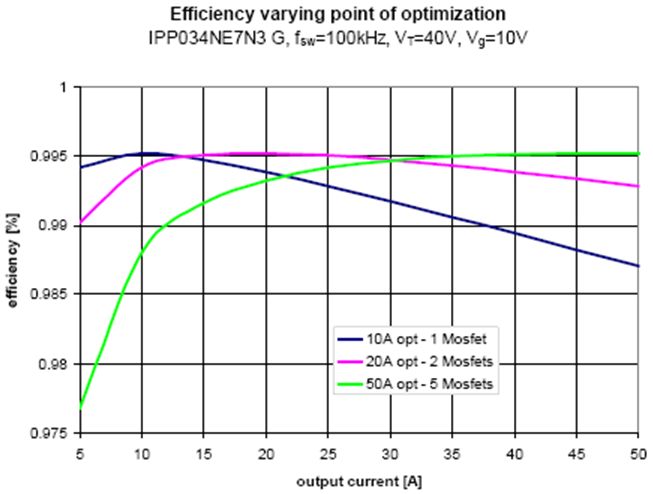

為闡明這個(gè)問題,圖4顯示了不同優(yōu)化方法得到的效率。圖中所示效率曲線為,當(dāng)變壓器電壓為40V、柵極驅(qū)動(dòng)電壓為10V、開關(guān)頻率為100kHz時(shí)計(jì)算得到的12V同步整流級的效率。在75V優(yōu)化表中選擇 IPP034NE7N3,按10 A MOSFET電流進(jìn)行設(shè)計(jì),所得到的優(yōu)化方案僅需一個(gè)MOSFET。如圖4所示,這種優(yōu)化方案能夠在低電流時(shí)實(shí)現(xiàn)很高的效率,而在高電流時(shí)效率卻極低。按50 A進(jìn)行優(yōu)化設(shè)計(jì),所得到的最佳方案則需要5個(gè)MOSFET。采用這種優(yōu)化方案,低電流時(shí)的效率將低得不能接受,但在滿負(fù)載時(shí)可以達(dá)到最高效率。因此,對該設(shè)置而言,最佳優(yōu)化方案是采用兩個(gè)并聯(lián)的MOSFET,從而獲得整體均衡的效率。

通常,按最高輸出功率的20%至30%對MOSFET進(jìn)行優(yōu)化,可以獲得均衡的總體效率。對于強(qiáng)調(diào)輕負(fù)載效率的系統(tǒng),可以按最高電流的10%至20%的低電流進(jìn)行優(yōu)化;而對于高負(fù)載設(shè)計(jì),則適于按最高電流的60%進(jìn)行優(yōu)化。應(yīng)當(dāng)避免按100%輸出負(fù)載進(jìn)行優(yōu)化,因?yàn)檫@會(huì)嚴(yán)重降低系統(tǒng)的低負(fù)載效率,并大大增加所需并聯(lián)的MOSFET數(shù)量。

圖4. 不同優(yōu)化方法實(shí)現(xiàn)的效率不盡相同

5. 借助四象限SR器件優(yōu)化表選擇MOSFET

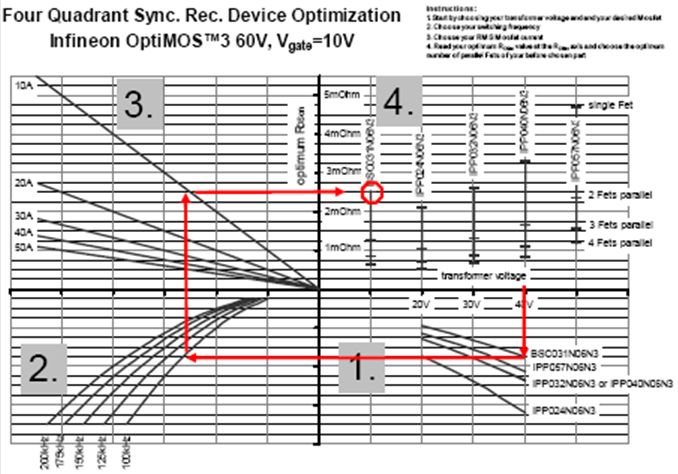

為了幫助開發(fā)人員更輕松地為SR應(yīng)用選擇最優(yōu)MOSFET,下面介紹一個(gè)四象限SR器件優(yōu)化表。借助這個(gè)優(yōu)化表,可以根據(jù)三個(gè)應(yīng)用參數(shù)找到最適合的器件:次級變壓器電壓、開關(guān)頻率和RMS MOSFET電流。為便于理解,圖5給出了一個(gè)實(shí)際的例子。

圖5. 四象限SR器件優(yōu)化表

使用優(yōu)化表時(shí),首先從次級變壓器電壓開始。在所用電壓值位置,畫一條垂直的直線。在兩條線相交處可以選出特定的MOSFET。通過一條水平的直線和一條垂直的直線,便可選擇開關(guān)頻率和MOSFET電流。如前面所討論,按最好從滿負(fù)載的20%至30%的電流值開始進(jìn)行選擇。此時(shí),可以在正Y軸上讀取最優(yōu)RDS(on)值。在第四個(gè)象限中,顯示了并聯(lián)MOSFET的最佳數(shù)量。在第四個(gè)象限中,必須選擇之前在第一個(gè)象限中選定的MOSFET型號。然后,按同樣的參數(shù)(變壓器電壓、開關(guān)頻率和電流RMS)對另一個(gè)型號的MOSFET重復(fù)執(zhí)行這個(gè)選擇過程。比較兩次選擇所得到的最優(yōu)RDS(on)值,最優(yōu)RDS(on)值越低的MOSFET所產(chǎn)生的功耗也越低,因而是更加高效的解決方案。

這個(gè)MOSFET選擇方法,是在假定應(yīng)用具備最優(yōu)開關(guān)性能的條件下計(jì)算得到的。如果發(fā)生了諸如動(dòng)態(tài)開啟或雪崩等二階效應(yīng),那么這個(gè)優(yōu)化表可能不準(zhǔn)確。此外,硬開關(guān)轉(zhuǎn)換器拓?fù)淇蓪?shí)現(xiàn)最佳結(jié)果。任何諧振軟開關(guān)拓?fù)渚赡軐?dǎo)致失配,因?yàn)榭梢曰厥绽瞄_關(guān)過程產(chǎn)生的部分電量。在這種情況下,實(shí)際最優(yōu)RDS(on) 值將低于計(jì)算得到的值。請注意,一次側(cè)采用準(zhǔn)諧振拓?fù)洌ɡ缦嘁芞VS全橋)也可使二次側(cè)的同步整流實(shí)現(xiàn)硬開關(guān)性能,從而也可以利用這種設(shè)計(jì)優(yōu)化表來進(jìn)行優(yōu)化。

從這種優(yōu)化表得到的所有結(jié)果,均以理想的MOSFET性能為前提。根據(jù)經(jīng)驗(yàn),實(shí)際應(yīng)用的結(jié)果與按理想狀況計(jì)算得到的結(jié)果有所不同。因此,利用這種優(yōu)化表得到的結(jié)果應(yīng)作為最優(yōu)器件選擇的參考,以防止MOSFET性能不足或過高。如果利用這種優(yōu)化表得到的結(jié)果是在兩個(gè)不同的并聯(lián)MOSFET數(shù)量之間,那么,數(shù)量較低的方案是適于低負(fù)載的優(yōu)化方案,而數(shù)量較高的方案則是更適于高功率的優(yōu)化方案。此外,任何與同步整流級并聯(lián)的緩沖網(wǎng)絡(luò)均會(huì)影響器件的選擇,因此,在設(shè)計(jì)時(shí)也必須予以考慮。

要在整個(gè)負(fù)載范圍內(nèi)實(shí)現(xiàn)總體優(yōu)化,僅一次計(jì)算是不夠的。除按特定負(fù)載值(電流值)計(jì)算最優(yōu)MOSFET之外,還需要按不同負(fù)載電流在這個(gè)四象限優(yōu)化表上進(jìn)行多次計(jì)算,以擴(kuò)大優(yōu)化范圍。同時(shí),還要根據(jù)實(shí)際應(yīng)用要求,調(diào)整所得結(jié)果。