0 引言

Delta-Sigma A/D轉(zhuǎn)換器具有高分辨率、高集成度、成本低和使用方便的特點,近年來,因數(shù)字化產(chǎn)品對高分辨率A/D,D/A轉(zhuǎn)換器需求的激增而得到廣泛地應(yīng)用。Delta-Sigma A/D轉(zhuǎn)換器的構(gòu)想出現(xiàn)已有很多年了,早期因受集成電路制造技術(shù)的限制,未在產(chǎn)品中廣泛使用,隨著集成電路制造成本不斷降低,該技術(shù)的應(yīng)用漸多,目前已成為高精度ADC的主流技術(shù)。隨著該技術(shù)的趨熱,有更多人想了解其工作原理,但目前國內(nèi)的教材對其涉及還不多,期刊論文多側(cè)重數(shù)學(xué)演繹,文獻中未見有詳盡的仿真實例。

除了制造專用ADC,該技術(shù)還易于用FPGA實現(xiàn),邏輯電路可以完全集成在FPGA內(nèi)部,只需要很少的外圍元件,就可以用FPGA直接進行混合信號處理。由于FPGA可擴展和可重配置的特性,特別適合產(chǎn)品研發(fā)和小規(guī)模生產(chǎn)的場合,另外用FPGA在單一芯片上實現(xiàn)多路Sigma-Delta A /D轉(zhuǎn)換也很容易。

Delta-Sigma有時稱其為Sigma-Delta,或∑-△。

1 Delta-Sigma A/D轉(zhuǎn)換器原理

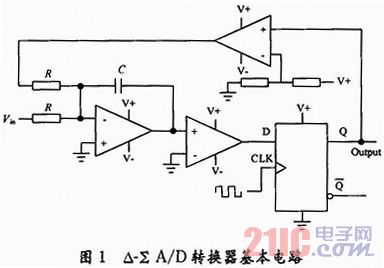

在△-∑A/D轉(zhuǎn)換器中,模擬輸入電壓信號被連接到一個積分器的輸入端。在輸出端對應(yīng)輸入大小產(chǎn)生一個電壓變化率,或者斜坡。然后用比較器將該斜坡電壓與地電位(0V)進行比較。比較器的行為就像1位A/D轉(zhuǎn)換器,根據(jù)積分器的輸出是正或負(fù)產(chǎn)生1位的輸出(“高”或“低”)。比較器的輸出通過一個以很高頻率時鐘驅(qū)動的D觸發(fā)器被鎖存,并且反饋到積分器的另一個輸入通道,向0V方向趨勢驅(qū)動積分器。基本電路如圖1所示。

在圖1中,最左邊的運放是積分器。積分器饋入的下一個運放是比較器,或1位A/D轉(zhuǎn)換器。接下來是D觸發(fā)器,在每個時鐘脈沖鎖存比較器的輸出,發(fā)送“高”或“低”信號到電路頂部的下一個比較器。最后這個比較器用于轉(zhuǎn)換信號極性,將觸發(fā)器的0 V/5 V邏輯電平輸出轉(zhuǎn)換到V+/V-電壓信號再反饋到積分器。

如果積分器輸出是正,第一次比較器將輸出一個“高”信號給觸發(fā)器的D輸入。在下一個時鐘脈沖,“高”信號將從Q線輸出到最后一個比較器的放大器輸入。最上面的那個比較器將看見一個輸入電壓大于+1/2 V的閾值電壓,它向正方向飽和,發(fā)送一個滿V+信號到積分器的另一個輸入端。這個V+反饋信號向負(fù)方向驅(qū)動積分器輸出。如果輸出電壓一直為負(fù),反饋環(huán)將發(fā)送一個矯正信號(V-)回到積分器的頂部輸入,向正方向驅(qū)動它。這就是△-∑行為的概念:第一個比較器感知在積分器輸出和0 V電壓之間的差(△),積分器求模擬輸入信號與最上面比較器輸出的和(∑)。

2 PSpice仿真

通過PSpice仿真模擬實驗,可以更容易和更清楚地理解△-∑A/D轉(zhuǎn)換器的工作原理。下面采用PSpiee仿真△-∑A/D轉(zhuǎn)換器。本文使用CaptLire CIS Lite Edition 9.2繪制電路圖,用PSpice Lite Version 9.2進行仿真。

2.1 繪制電路圖

先用OrCAD Capture繪制△-∑A/D轉(zhuǎn)換器電路圖,如圖2所示。信號源采用FREQ=100 kHz的正弦信號。偏移VOFF=0,幅度先設(shè)置為0 V,AMPL=0。

為方便起見圖中所有的運算放大器都使用uA741模型,因為這個模型很容易找到,實際項目中根據(jù)需要選用合適的運放。D觸發(fā)器使用74LS74。在CaptureCIS Lite Edition 9.2和PSpice Lite Version 9.2中沒有74LS系列的元件符號庫74ls.olb也沒有仿真庫74ls.lib,可以從下面的網(wǎng)站下載:

http://power.teipat. gr/download/OrCAD/OrCAD%20Libraries/Library%20for%20Capture/PSPICE/

74LS系列是低功耗肖特基型TTL器件,輸入高電平最小為2.0 V,輸入低電平最大為0.8 V;輸出高電平最小位2.7 V,輸出低電平最大為0.5 V。采用R3和R4分壓將U2的輸出電壓轉(zhuǎn)換為0~3.75 V電壓,以適應(yīng)TTL輸入電平。74LS模型只接受正電壓作為電平信號,所以可以不理會比較器U2的負(fù)電壓輸出。R6和R7分壓15 V為2.5 V作為參考電壓,將74LS74的TTL輸出電平通過U3轉(zhuǎn)換為V+/V-的電壓信號。D觸發(fā)器的時鐘由DSTM1提供。從74LS74的產(chǎn)品手冊可知,當(dāng)LCR和PRE端都為高電平時,在時鐘的上升沿,D觸發(fā)器將輸入端D的數(shù)據(jù)送到輸出端Q,并鎖存到下一個時鐘的上升沿。這個高電平由DSTM2提供。圖3是在Stimulus Editor中顯示的STM1和STM2的波形,雙擊波形可以對它進行編輯。

2.2 輸入信號電壓幅度為0 V的情況

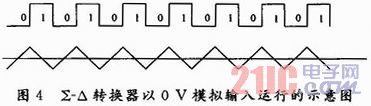

從功能上說,△-∑A/D轉(zhuǎn)換器的轉(zhuǎn)換結(jié)果是一個由觸發(fā)器輸出的串行比特流。如果模擬輸入是0 V,積分器將不會有趨向正或負(fù)的斜坡,積分器只響應(yīng)反饋電壓。在這種情況下,觸發(fā)器輸出將持續(xù)在“高”和“低”之間震蕩輸出,反饋系統(tǒng)前后搜索,試圖維持積分器輸出在0 V。圖4是∑-△轉(zhuǎn)換器以0 V模擬輸入運行的示意圖,圖中方波是D觸發(fā)器輸出,三角波是積分器輸出的。

圖5是∑-△轉(zhuǎn)換器以0 V模擬輸入運行的仿真圖。

圖5中,方波是D觸發(fā)器輸出的串行比特流,幅度較大的三角波是積分器的輸出波形。仿真配置文件設(shè)置如圖6所示。

2.3 輸入信號電壓幅度不為0 V的情況

如果施加一個小的負(fù)模擬輸入電壓,積分器將有一個向負(fù)方向傾斜它的輸出的趨勢。反饋只能以一個固定的電壓(電源電壓)在一定的時間內(nèi)校正積分器的傾斜,這樣觸發(fā)器的比特流輸出將和前面不完全相同。圖7是∑-△轉(zhuǎn)換器以小負(fù)模擬輸入運行的示意圖。

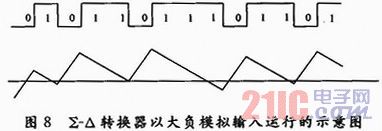

施加一個較大的負(fù)模擬輸入信號到積分器,它的輸出向正方向傾斜的更陡。這樣,反饋系統(tǒng)將輸出比以前更多的1,以帶領(lǐng)積分器輸出回到0 V。圖8為∑-△轉(zhuǎn)換器以較大負(fù)模擬輸入運行的示意圖。

用平均串行比特流的方法可以從該電路獲得并行二進制數(shù)輸出。例如,用一個計數(shù)電路搜集在一個給定時鐘脈沖中觸發(fā)器輸出1的總數(shù)(正輸入電壓數(shù)輸出0的總數(shù)),該計數(shù)器的值可以用來表示模擬輸入電壓。圖9是∑-△轉(zhuǎn)換器以5 V模擬輸入運行的仿真圖。

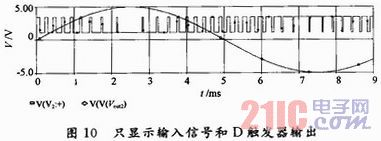

圖中,正弦波是輸入信號,方波是D觸發(fā)器輸出的串行比特流,三角波是積分器的輸出波形。圖10只顯示輸入信號和D觸發(fā)器輸出。

從圖10中可以清楚地看到輸入信號對輸出脈沖寬度和頻率的調(diào)制,輸出是占空比隨模擬輸入電壓大小變化的1,0位流。

3 PSpice仿真對不同電壓幅度的輸入信號積分器參數(shù)的調(diào)整

對不同幅度的輸入信號,需要調(diào)制積分器的參數(shù),以提高A/D轉(zhuǎn)換的精度。圖11是理想積分器及其輸入/輸出公式,其中RC是積分器的積分常數(shù)。

![]()

對應(yīng)本文的電路R1、R5和C1決定積分器的時間常數(shù),R1C1是輸入信號的積分常數(shù),R5C1是反饋信號的積分常數(shù)。改變電阻或電容值會改變轉(zhuǎn)換精度。改變C1會同時改變輸入信號和反饋信號的時間常數(shù),當(dāng)輸入信號的幅值范圍變化時通過改變R1來提高轉(zhuǎn)換精度要好一些。通過對R1的參數(shù)掃描可以看出積分器時間常數(shù)對轉(zhuǎn)換精度的影響。

通過參數(shù)掃描分析可知,電阻增加,減小了輸入信號的強度,脈沖直接的間距減小,脈沖之中包含更少的“0”或“1”,說明轉(zhuǎn)換精度降低。但是R1也不能太小,如果R1太小在對應(yīng)輸入信號幅值較高處會丟失一些脈沖,也就是丟失了數(shù)據(jù)。時間常數(shù)的選取要根據(jù)實際需求中輸入信號波形的幅值范圍進行反復(fù)仿真以獲取最佳參數(shù),并用實際電路測試來確定。

4 小信號輸入的仿真例子

前面在說明∑-△轉(zhuǎn)換器原理時輸入信號電壓幅值為5 V,實際應(yīng)用中很多情況下輸入信號是毫伏量級的,下面對幅值為0.05 V(50 mV)的正弦信號進行仿真。用參數(shù)仿真的方法確定R1=1.1kΩ。仿真結(jié)果如圖12所示。

5 結(jié)語

∑-△A/D轉(zhuǎn)換器具有非常高的分辨率,而且噪聲很低,因為它采用了過采樣的技術(shù),因此對于前端的抗混疊濾波器的要求也大大降低,一般一個簡單的RC低通濾波器就足夠了。這類ADC的線性度也非常好,目前已成為實現(xiàn)高精度A/D轉(zhuǎn)換的主要方式,但是它付出的代價是采樣速率的降低。另外,由于內(nèi)部濾波器對于模擬信號的突變和通道的切換需要相對長的建立時間,而且輸出的數(shù)據(jù)與模擬輸入之間有較長的延時,所以這類A/D轉(zhuǎn)換器適用于那些模擬信號近似于直流或變化很慢的應(yīng)用,如溫度測量、壓力測量等,近年來在音頻領(lǐng)域也有應(yīng)用。