采用時(shí)間交替模數(shù)轉(zhuǎn)換器(ADC),以每秒數(shù)十億次的速度采集同步采樣模擬信號(hào),對于設(shè)計(jì)工程師來說,這是一項(xiàng)極大的技術(shù)挑戰(zhàn),需要非常完善的混合信號(hào)電路。時(shí)間交替的根本目標(biāo)是通過增加轉(zhuǎn)換器,在不影響分辨率和動(dòng)態(tài)性能的前提下使采樣頻率增倍。

本文探討時(shí)間交替模數(shù)轉(zhuǎn)換器的主要技術(shù)難點(diǎn),并提供切實(shí)可行的系統(tǒng)設(shè)計(jì)指導(dǎo),包括可解決上述問題的創(chuàng)新性元件功能和設(shè)計(jì)方法。本文還提供從7Gsps雙轉(zhuǎn)換器芯片“交替解決方案”測得的FFT結(jié)果。最后,文章還描述了實(shí)現(xiàn)高性能所需的應(yīng)用支持電路,包括時(shí)鐘源和驅(qū)動(dòng)放大器。

對更高采樣速度的需求不斷增加

何時(shí)提高采樣頻率會(huì)更加有益,其中的原因又是什么呢?這個(gè)問題有多種答案。模數(shù)轉(zhuǎn)換器的采樣速度基本上直接決定了可以在一個(gè)采樣瞬間進(jìn)行數(shù)字化的瞬時(shí)帶寬。尼奎斯特和香農(nóng)采樣定理證明了最大可用采樣帶寬(BW)相當(dāng)于采樣頻率Fs的一半。

3GSPS模數(shù)轉(zhuǎn)換器實(shí)現(xiàn)了在一次采樣期內(nèi)采集1.5GHz模擬信號(hào)頻譜。如果采樣速度翻倍,尼奎斯特帶寬也倍增至3GHz。通過時(shí)間交替實(shí)現(xiàn)采樣帶寬倍增對于很多應(yīng)用來說都是有益的。例如,無線電收發(fā)器架構(gòu)可以增加信息信號(hào)載波數(shù),從而增加系統(tǒng)數(shù)據(jù)輸出量。采樣頻率倍增還可以提高采用飛行時(shí)間(TOF)原理的LIDAR測量系統(tǒng)的分辨率。實(shí)際上,通過縮短有效采樣期可以降低飛行時(shí)間測量值的不確定性。

數(shù)字示波器還需要高采樣頻率Fs/輸入頻率FIN比值,以準(zhǔn)確采集復(fù)合模擬或數(shù)字信號(hào)。要采集輸入頻率的諧波部分,就要求采樣頻率必須是輸入頻率(最大值)的倍數(shù)。例如,如果示波器采樣頻率不夠高,且更高階諧波位于模數(shù)轉(zhuǎn)換器的尼奎斯特帶寬外,方形波將顯示為正弦形。

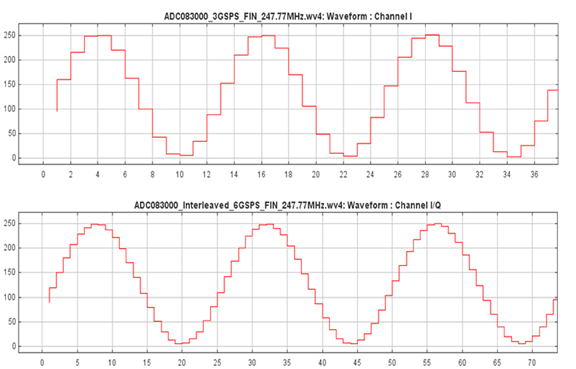

圖1說明了示波器前端雙倍采樣頻率的益處。6GSPS采樣波形是采樣模擬輸入更準(zhǔn)確的表示形式。很多其他測試儀器系統(tǒng)(例如質(zhì)譜儀和伽馬射線望遠(yuǎn)鏡)依靠較高的過采樣/FIN進(jìn)行脈沖波形測量。

圖1:以3GSPS和6GSPS采樣的247.77MHz信號(hào)的時(shí)域值圖。

增加采樣頻率還具有其他優(yōu)點(diǎn)。過采樣信號(hào)還實(shí)現(xiàn)了通過數(shù)字濾波在數(shù)字域改善增益的特點(diǎn)。實(shí)際上,模數(shù)轉(zhuǎn)換器噪聲底可在更大輸出帶寬上擴(kuò)散。倍增固定輸入帶寬的采樣率在動(dòng)態(tài)范圍使噪聲改善了3dB。采樣頻率每倍增一次,將為動(dòng)態(tài)范圍提供一個(gè)附加3dB。

時(shí)間交替技術(shù)的難點(diǎn)

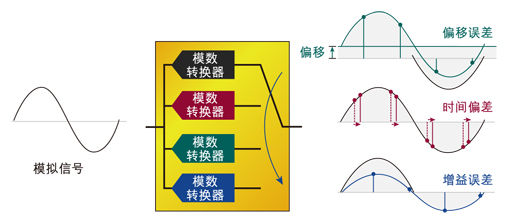

時(shí)間交替的主要難點(diǎn)是通道間采樣時(shí)鐘邊沿的精確校準(zhǔn)和IC間固有變化的補(bǔ)償。精確匹配各單獨(dú)模擬數(shù)據(jù)轉(zhuǎn)換器間的增益、偏移和時(shí)鐘相位是一項(xiàng)很大的挑戰(zhàn),主要因?yàn)檫@些參數(shù)都取決于頻率。除非能夠?qū)崿F(xiàn)這些參數(shù)的精確匹配,否則動(dòng)態(tài)性能和分辨率將會(huì)降低。圖2顯示了三個(gè)主要誤差源。

圖2:交替模數(shù)轉(zhuǎn)換器產(chǎn)生的增益、偏移和時(shí)間誤差。

采樣時(shí)鐘相位調(diào)整

通常,雙通道交替轉(zhuǎn)換器系統(tǒng)需要模數(shù)轉(zhuǎn)換器輸入采樣時(shí)鐘的時(shí)間移動(dòng)1/2個(gè)時(shí)鐘周期。但是,ADC083000結(jié)構(gòu)使用芯片內(nèi)交替,其時(shí)鐘頻率等于采樣率的一半,即3GSPS的時(shí)鐘頻率為1.5GHz。因此,對于采用兩個(gè)ADC083000的雙通道系統(tǒng),模數(shù)轉(zhuǎn)換器輸入采樣時(shí)鐘邊沿必須移動(dòng)1/4個(gè)時(shí)鐘周期或錯(cuò)開90(。即1.5GHz時(shí)鐘對應(yīng)于166.67ps。

可以相對準(zhǔn)確地計(jì)算出對應(yīng)1/4時(shí)鐘周期相移的時(shí)鐘信號(hào)走線長度。對于FR4印刷電路板材料,信號(hào)以20cm/ns(即50ps為1cm)的速度傳播。例如,如果傳輸?shù)揭粋€(gè)模數(shù)轉(zhuǎn)換器的時(shí)鐘走線比另一個(gè)長3cm,這將產(chǎn)生150ps的相移。難點(diǎn)在于精確符合附加的16.67ps時(shí)移。

ADC083000具有集成的時(shí)鐘相位調(diào)整功能,使用戶可以向輸入采樣時(shí)鐘添加延時(shí),以相對于另一模數(shù)轉(zhuǎn)換器的采樣時(shí)鐘實(shí)現(xiàn)相移。可以通過SPI總線,采用兩個(gè)內(nèi)部寄存器手動(dòng)調(diào)整模數(shù)轉(zhuǎn)換器的時(shí)鐘相位。只能沿一個(gè)方向?qū)崿F(xiàn)相移,增加延時(shí)。設(shè)計(jì)工程師應(yīng)確定兩個(gè)分立模數(shù)轉(zhuǎn)換器中的位置,確定哪一個(gè)“在前”并調(diào)整其相位,使其采樣邊沿與另一模數(shù)轉(zhuǎn)換器采樣邊沿呈90o,從而可實(shí)現(xiàn)亞皮秒調(diào)整分辨率。

通道間增益和偏移匹配

在雙轉(zhuǎn)換器交替系統(tǒng)中,通道增益失配產(chǎn)生的誤差電壓會(huì)導(dǎo)致Fs/2-FIN和Fs/4±FIN發(fā)生圖像雜散信號(hào)(假設(shè)輸入信號(hào)在第一尼奎斯特頻帶內(nèi))。8位轉(zhuǎn)換器具有28或256個(gè)編碼。假設(shè)轉(zhuǎn)換器全輸入范圍為Vp-p,,LSB大小等于1V/256=3.9mV。我們可以得出1/2LSB精確度需要的增益匹配為0.2%。

ADC083000的輸入全范圍電壓或增益可以使用9位數(shù)據(jù)分辨值進(jìn)行線性且單調(diào)的調(diào)整。調(diào)整范圍是標(biāo)稱700mVp-p差分值的±20%,或560mVp-p至840mVp-p。

840mV-560mV=280mV.

29=512步幅

280mV/512=546.88μV

此微調(diào)允許比上述要求大0.2%的增益匹配。

相鄰?fù)ǖ篱g的偏移失配將產(chǎn)生誤差電壓,導(dǎo)致Fs/2處發(fā)生偏移雜散信號(hào)。由于偏移雜散信號(hào)位于尼奎斯特頻帶邊沿,雙通道系統(tǒng)的設(shè)計(jì)人員通常可以據(jù)此計(jì)劃系統(tǒng)頻率,并著力于增益和相位匹配。

但是,假設(shè)需要的偏移匹配也是1/2LSB,ADC083000的輸入偏移可以使用9位分辨率從標(biāo)稱零偏移線性且單調(diào)的調(diào)整為45mV偏移。因此,每個(gè)編碼步幅提供0.176mV偏移,9位分辨率實(shí)現(xiàn)1/2LSB精確度。

數(shù)字輸出的同步化

從兩個(gè)模數(shù)轉(zhuǎn)換器輸出的數(shù)據(jù)流同步化對于實(shí)現(xiàn)優(yōu)異采樣速度和帶寬組合至關(guān)重要。也就是說,如果各轉(zhuǎn)換器間未實(shí)現(xiàn)輸出同步,就無法采集有意義的數(shù)據(jù)。千兆采樣率模數(shù)轉(zhuǎn)換器可多路分離輸出數(shù)據(jù),以降低數(shù)字輸出數(shù)據(jù)傳輸率。用戶可以選擇使數(shù)據(jù)傳輸率分離為1/2或1/4,這取決于采用的FPGA技術(shù)的處理能力。

輸出采集時(shí)鐘(DCLK)也被分離,可在SDR或DDR模式中配置。但是,多路分離帶來新的考量問題,因?yàn)楝F(xiàn)在增加了輸入采樣時(shí)鐘和各模數(shù)轉(zhuǎn)換器DCLK輸出之間的協(xié)調(diào)不確定性。為了克服這個(gè)問題,ADC083000可以精確復(fù)位采樣時(shí)鐘輸入與DCLK輸出的關(guān)系,這由用戶提供的DCLK_RST脈沖確定。這允許一個(gè)系統(tǒng)中采用多個(gè)模數(shù)轉(zhuǎn)換器,使其DCLK(和數(shù)據(jù))輸出在與采樣共享輸入時(shí)鐘相同的時(shí)間點(diǎn)躍遷,從而實(shí)現(xiàn)多個(gè)模數(shù)轉(zhuǎn)換器之間的同步。

數(shù)字交替方法

模擬校準(zhǔn)是實(shí)現(xiàn)高動(dòng)態(tài)范圍、高整體集成解決方案的行之有效的方法,其集成的時(shí)鐘相位、增益和偏移調(diào)整功能可提供高精確度。

模擬校準(zhǔn)的可行替代方法是用于交替數(shù)據(jù)的數(shù)字校正算法。此方法尋求在數(shù)字域校正數(shù)據(jù)轉(zhuǎn)換器失配,而不需要任何模擬偏移、增益或相位校正。理論上,這些算法可獨(dú)立工作,不需要實(shí)現(xiàn)校準(zhǔn)或了解輸入信號(hào)。此外,數(shù)字偏移、增益和相位校正因素的匯合時(shí)間也是關(guān)鍵系統(tǒng)指標(biāo)。

SP Devices公司開發(fā)的算法經(jīng)過驗(yàn)證是符合這些條件的一種數(shù)字后處理方法。SP Devices的ADX技術(shù)持續(xù)提供模數(shù)轉(zhuǎn)換器的增益、偏移和時(shí)間偏差誤差的后臺(tái)估計(jì)值,而不需要任何特殊校準(zhǔn)信號(hào)或后期微調(diào)。此算法對于校正靜態(tài)和動(dòng)態(tài)失配誤差很有效。

ADX技術(shù)估計(jì)誤差,并使用抑制的全部失配誤差重新構(gòu)建信號(hào)。IP-core的誤差校正算法對于任何輸入信號(hào)類型均有效。該數(shù)字信號(hào)處理的結(jié)果超出ADX核心的時(shí)間交替頻譜,并消除了與失配相關(guān)的明顯交替失真雜散信號(hào)。

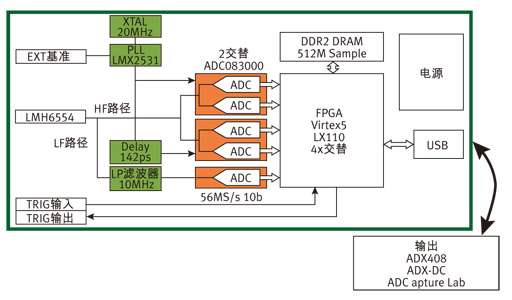

配備兩個(gè)ADC0830003GSPS、8位模數(shù)轉(zhuǎn)換器的美國國家半導(dǎo)體參考板展示了SP Devices的算法。數(shù)據(jù)轉(zhuǎn)換器使用板上FPGA中內(nèi)嵌的ADX技術(shù)實(shí)現(xiàn)交替。圖3為7GSPS數(shù)字化卡的框圖。

圖3:含LMX2531和LMH6554的ADQ108系統(tǒng)框圖。

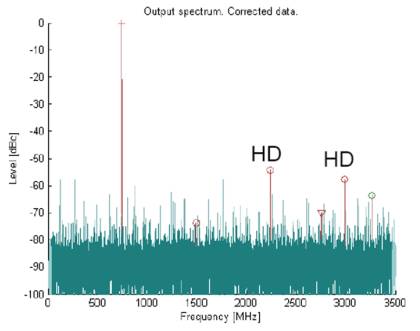

圖4是SPDevicesADQ108數(shù)據(jù)采集卡的輸出頻譜性能圖。值得注意的是雜散峰值部分是由于諧波失真所致,交替雜散信號(hào)已大幅減少。關(guān)于數(shù)據(jù)采集卡的其他詳細(xì)信息,請參見:http://spdevices.com/index.php/adq108。

圖4:采用ADX技術(shù)的模數(shù)轉(zhuǎn)換器組合頻譜。