電壓調(diào)節(jié)技術(shù)與頻率調(diào)節(jié)技術(shù)的結(jié)合使用為時鐘切換添加了新原則,以確保新時鐘頻率擁有安全的電壓電平。此外,電壓調(diào)節(jié)功能需要在SoC內(nèi)創(chuàng)建電壓域。這將在兩個可變電壓域之間或可變電壓域和靜態(tài)電壓域之間創(chuàng)建電壓域接口。跨越接口的可變電壓電平差為接口設(shè)計帶來了獨特挑戰(zhàn)。時鐘、信號電平轉(zhuǎn)換以及電壓域隔離等問題都必須仔細(xì)考慮,以確保最短延遲和信號完整性。

先進電源控制器

作為美國國家半導(dǎo)體PowerWise技術(shù)的一部分,先進電源控制器(APC)旨在協(xié)助調(diào)節(jié)電壓域的電壓控制。APC支持閉環(huán)自適應(yīng)電壓調(diào)節(jié)(AVS)和開環(huán)動態(tài)電壓調(diào)節(jié)(DVS)。APC支持動態(tài)頻率調(diào)節(jié)功能,帶有至?xí)r鐘管理單元(CMU)的接口,可為SoC提供時鐘信號。電壓電平可通過PowerWise接口(PWI)傳送給芯片外協(xié)同電源單元。硬件性能監(jiān)控電路(HPM)用于AVS閉環(huán)電壓控制。APC根據(jù)HPM提供的芯片性能信息,決定最佳的供電電壓,以實現(xiàn)目標(biāo)性能水平。在決定電壓電平時,SoC制程變化、SoC晶粒溫度變化、穩(wěn)壓器偏置或偏差以及系統(tǒng)靜態(tài)電阻壓降都會自動得到補償。DVS模式則依照預(yù)先設(shè)定的電壓頻率對照表進行操作。

參考設(shè)計

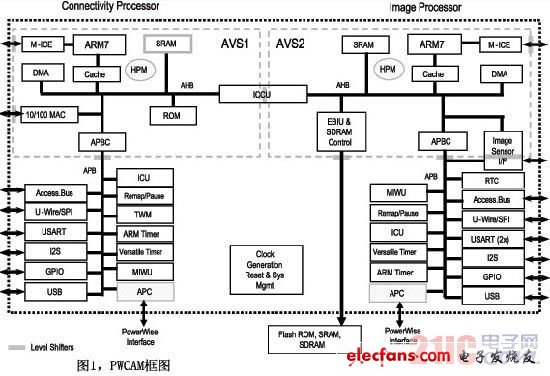

PowerWise Camera(PWCAM)參考設(shè)計測試芯片用于技術(shù)驗證和演示。PWCAM是模擬通用雙處理器架構(gòu)。圖1是PWCAM的框圖。PWCAM包含兩套獨立的基于ARM7的處理器系統(tǒng):連接處理器和圖像處理器。每套系統(tǒng)都有一組AHB和APB外設(shè)。每個CPU、AHB和APB都是由同一系統(tǒng)時鐘驅(qū)動,時鐘頻率高達(dá)96MHz。連接處理器和圖像處理器通過核間通信單元(ICCU)進行通信。這個通信單元是異步AHB-AHB橋。只有圖像處理器可以直接訪問外部存儲器。設(shè)計目標(biāo)是為了將獨立的頻率和電壓調(diào)節(jié)功能引入連接處理器和圖像處理器,這要求對APC的設(shè)計和集成進行恰當(dāng)區(qū)分。

AVS中的時鐘切換

對于電壓調(diào)節(jié)與頻率調(diào)節(jié)功能整合而言,最重要的要求是在頻率還未切換之前,確保新頻率所需電壓到位。如果調(diào)高時鐘頻率,在時鐘切換為新頻率之前,電壓必須提升至足夠高的水平。如果調(diào)低時鐘頻率,時鐘可以立即切換為新頻率,因為電壓電平已經(jīng)足夠。為了滿足這個要求,時鐘調(diào)節(jié)控制必須通過APC。APC利用目標(biāo)索引和當(dāng)前索引等接口協(xié)議,來批準(zhǔn)實際系統(tǒng)時鐘切換。

AVS電壓域分區(qū)

一般而言,電壓調(diào)節(jié)與時鐘頻率調(diào)節(jié)總是結(jié)合在一起。時鐘域邊界自然成為AVS電壓域邊界的選擇。時鐘域邊界的異步接口使得多電壓AVS部署變得更為簡單。然而,由于性能原因,有時可能需要采用同步接口。將IP塊集成進AVS電壓域通常需要IP塊級的分區(qū)改變,以便分隔電壓域。很多IP塊包含不只一個時鐘域。例如,外設(shè)塊包含一個內(nèi)部總線接口時鐘和另一個外設(shè)時鐘。內(nèi)部總線時鐘根據(jù)系統(tǒng)時鐘進行調(diào)節(jié),而外設(shè)時鐘則按照固定頻率運行。相對于對IP進行重新分區(qū)以將IP塊集成到AVS電壓域內(nèi),有時讓IP塊固定頻率部分以最低AVS電壓電平進行操作,從而使整個IP塊集成到AVS電壓域內(nèi),更為容易。

PWCAM分區(qū)需要考慮這些因素。圖1給出帶有電壓域邊界的PWCAM,用于控制AVS的嵌入式APC和HPM,以及需要信號水平轉(zhuǎn)移的接口。此外,連接處理器內(nèi)的SRAM也進行分區(qū),以便由存儲器保留電壓供電。存儲器保留電壓可以在進行頻率調(diào)節(jié)時追蹤AVS電壓,但有下限箝位電壓,確保即使邏輯部分?jǐn)嚯娀蛟诓缓线m電壓電平下,SRAM始終保持有效數(shù)據(jù)。

電平轉(zhuǎn)換及斷電信號箝位

有兩種電壓域接口,一種是靜態(tài)電壓域和AVS電壓域之間的接口;另一種是兩個獨立AVS電壓域之間的接口。信號穿越電壓域邊界,需要將電平轉(zhuǎn)換以便目的域能正確識別。

PWCAM 采用的電平轉(zhuǎn)換策略確保進出域的信號都有位于AVS域邊界的電平轉(zhuǎn)換器。除了執(zhí)行電平轉(zhuǎn)換之外,電平轉(zhuǎn)換器還可起到屏蔽作用,將信號保持在相應(yīng)的電壓域內(nèi),最大限度減少信號完整性問題。如果AVS電壓域支持?jǐn)嚯姽δ埽到y(tǒng)在斷電狀態(tài)下將輸入及輸出箝定在已知狀態(tài)非常重要。這種箝位功能很容易就能整合到電平轉(zhuǎn)換器內(nèi)。

電壓域邊界的同步定時

自適應(yīng)調(diào)節(jié)電壓域里的信號定時根據(jù)電壓電平的變化而變化。如果電壓域采用同步接口,在設(shè)計信號路徑和時鐘路徑時,要仔細(xì)考慮定時路徑的可變特性。

AC定時路徑

如果任何交流定時路徑(輸入路徑或輸出路徑)的部分在調(diào)節(jié)電壓域內(nèi),輸入設(shè)置/保持時間或輸出有效時間在調(diào)節(jié)電壓范圍內(nèi)大幅度波動。如果技術(shù)規(guī)格無法承受這樣大的變動,則必須采取措施將這種變動減至最少。類似一般定時優(yōu)化技術(shù),通常是使取樣反轉(zhuǎn)盡量接近電壓域邊界。

內(nèi)部定時路徑

與可變定時相關(guān)的內(nèi)部路徑是指兩個電壓域之間的反轉(zhuǎn)至反轉(zhuǎn)(flop to flop)定時路徑,而其中至少有一個是電壓調(diào)節(jié)域。由于電壓調(diào)節(jié)功能與時鐘頻率調(diào)節(jié)功能結(jié)合在一起,因此當(dāng)電壓向下調(diào)節(jié)時,會有更多的設(shè)置時間。時鐘路徑的可變定時則會使調(diào)節(jié)電壓域與靜態(tài)電壓域之間的時鐘偏差也隨之改變。電壓下調(diào)幅度越大,時鐘偏差也越大。最后所得到的結(jié)果是信號路徑的周期時間會縮短,而且也會出現(xiàn)保持時間的問題。添加時間延遲補償電路以便為所有可能出現(xiàn)的定時時間轉(zhuǎn)變作出補償并不可行,因為時鐘的偏差幅度太大,實在無法預(yù)測。為了解決這個可變定時時間問題,關(guān)鍵是添加時鐘同步功能,以盡量減少時鐘偏差,更重要的是,使時鐘偏差幅度可以預(yù)測。

AVS/DVS設(shè)計考慮因素

與典型系統(tǒng)設(shè)計相比,進行多電壓調(diào)節(jié)電路設(shè)計需注意以下幾方面:額外的資料庫特征化和定時驗證點;在設(shè)計體系、分區(qū)和編碼等方面進行電壓域考慮,協(xié)助正確布局;電平轉(zhuǎn)換器插入及校驗;掃描插入、緩沖插入及ECO都必須考慮電壓域。

結(jié)論

由于電平調(diào)節(jié)的自適應(yīng)性,多電壓AVS對于功率優(yōu)化是非常有效的。采用多個調(diào)節(jié)電壓域,確實會使設(shè)計及實施變得更為復(fù)雜。但PWCAM測試芯片的例子表明,只要進行適當(dāng)規(guī)劃和執(zhí)行,其復(fù)雜程度在可控范圍內(nèi)。功耗的大幅度降低表明這種努力是值得的。