高速設(shè)計(jì)往往易被忽視或者相當(dāng)重要。系統(tǒng)電路板布局已成為設(shè)計(jì)本身的一個(gè)主要組成部分,因此,我們必須了解影響高速信號(hào)鏈路設(shè)計(jì)性能的機(jī)制。

盡管身為工程師,但我們也很可能“制造”較多麻煩。因此,切忌過分挑剔而使CAD工程師陷入設(shè)計(jì)困境,這并不能給性能帶來(lái)任何改善。

不要忘記裸露焊盤

裸露焊盤有時(shí)會(huì)被忽視,而它對(duì)充分發(fā)揮信號(hào)鏈路性能和幫助器件散熱卻非常重要。裸露焊盤在ADI公司我們通常稱之為引腳0,是目前大多數(shù)器件下方的焊盤。它是一個(gè)重要的接點(diǎn),一般芯片的所有內(nèi)部接地都是通過它而連接到器件下方的中心點(diǎn)。

您是否已注意到目前有許多轉(zhuǎn)換器和放大器都缺少接地引腳?裸露焊盤就是其原因所在。關(guān)鍵是要將此引腳妥善固定(即焊接)到印刷電路板(PCB),而實(shí)現(xiàn)魯棒的電氣和熱連接,否則,系統(tǒng)設(shè)計(jì)可能遭到各種破壞。

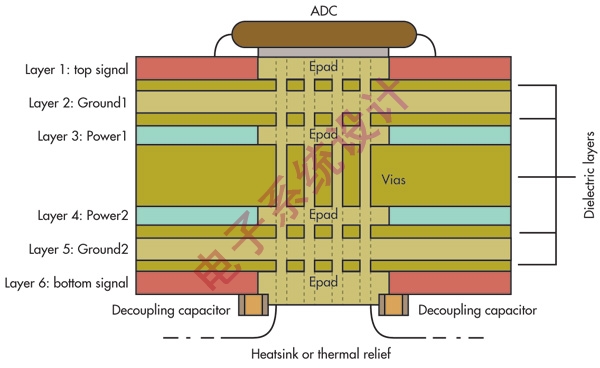

利用裸露焊盤實(shí)現(xiàn)最佳電氣和熱連接基本分為三個(gè)步驟。首先,在可能的情況下,在PCB的各層上都復(fù)制裸露焊盤,這將為所有接地和接地層提供較厚的熱連接而實(shí)現(xiàn)快速散熱。

此步驟與大功率器件和具有多通道的應(yīng)用相關(guān)。在電氣方面,這將為所有接地層提供良好的等電位連接。您甚至還可以在底層復(fù)制裸露焊盤(圖1),這可作為去耦用熱風(fēng)焊盤接地點(diǎn)和安裝底側(cè)散熱器的位置。

圖1:在每一層上復(fù)制裸露焊盤能夠幫助創(chuàng)建魯棒的電氣和散熱接地連接,同時(shí),還能為熱風(fēng)焊盤和底側(cè)去耦增加附加區(qū)域。

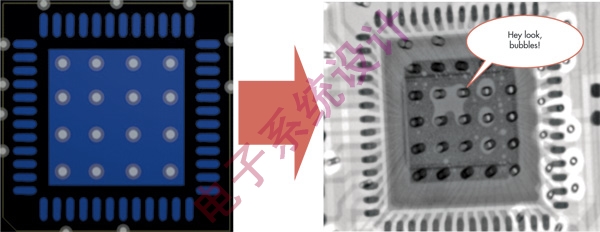

其次,將裸露焊盤分割成棋盤似的多個(gè)相同部分。這可以通過兩種方式實(shí)現(xiàn):在敞開的裸露焊盤上使用絲網(wǎng)印刷交叉陰影線或者阻焊膜。此步驟可以確保器件與PCB之間的魯棒連接。在回流焊組裝工藝中,無(wú)法確定焊錫膏如何流動(dòng)并最終將器件連接到PCB。

圖2:如果裸露焊盤未被分割并且通孔未被填充,回流焊過程中將會(huì)形成空洞。

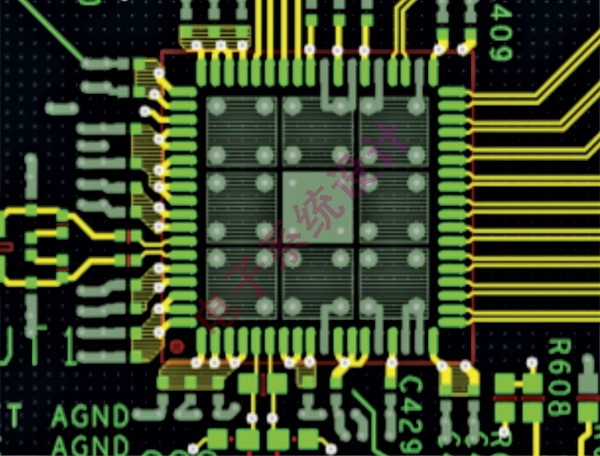

出現(xiàn)的問題是,連接可能存在但分布卻不均勻。可能僅僅得到一個(gè)連接并且連接很小,或者更糟糕的是,此連接位于拐角處。將裸露焊盤分割成較小部分,能夠確保每個(gè)區(qū)域都有一個(gè)連接點(diǎn),從而實(shí)現(xiàn)更魯棒的、均勻連接的裸露焊盤(圖2和圖3)。

圖3:分割PCB上的裸露焊盤有助于在電路板裝配過程中PCB與IC粘合得更緊密。

最后,應(yīng)當(dāng)確保各部分都有過孔連接到地。各區(qū)域通常都很大,足以放置多個(gè)過孔。組裝之前,務(wù)必用焊錫膏或者環(huán)氧樹脂填充每個(gè)過孔,這一步非常重要,可以確保裸露焊盤焊錫膏不會(huì)回流到這些過孔空洞中,而降低正確連接的機(jī)率。

去耦和平面電容

有時(shí)我們會(huì)忽略使用去耦的目的,而僅僅在電路板上分散許多數(shù)值的電容,使較低阻抗的電源連接到地。但問題依然存在:到底需要多少電容?

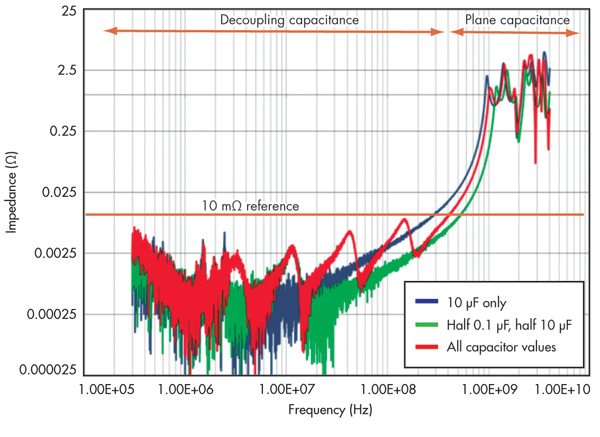

許多文獻(xiàn)表示,應(yīng)使用多個(gè)電容和多個(gè)數(shù)值來(lái)降低輸電系統(tǒng)(PDS)的阻抗,但這并非完全正確。事實(shí)上,僅需選擇正確數(shù)值和正確“種類”的電容,就能降低PDS的阻抗。

比如我們要設(shè)計(jì)10mΩ的參考平面,如果在系統(tǒng)電路板上使用多個(gè)電容值,便可降低在500MHz頻率范圍內(nèi)的阻抗,如圖4中的紅色曲線所示。

圖4:標(biāo)準(zhǔn)的去耦電容可以幫助降低高達(dá)500MHz的PDS阻抗,而頻率超過500MHz時(shí)則由平面電容解決。了解所用電容可以降低設(shè)計(jì)中所用電容的數(shù)量和類型。

然而,讓我們?cè)倏匆幌戮G色曲線,其在同樣的設(shè)計(jì)上僅使用了0.1μF和10μF兩種電容。這證明了如果使用恰當(dāng)?shù)碾娙荩瑒t不需要采用如此多的電容值。這也有助于節(jié)省布局和物料清單(BOM)成本。

然而,并非所有的電容“生來(lái)平等”,即使來(lái)源于同一供應(yīng)商,其工藝、尺寸和樣式也有差別。如果未使用正確的電容,則不論是采用多個(gè)電容還是采用幾種不同類型的電容,其結(jié)果都會(huì)給PDS帶來(lái)反作用。

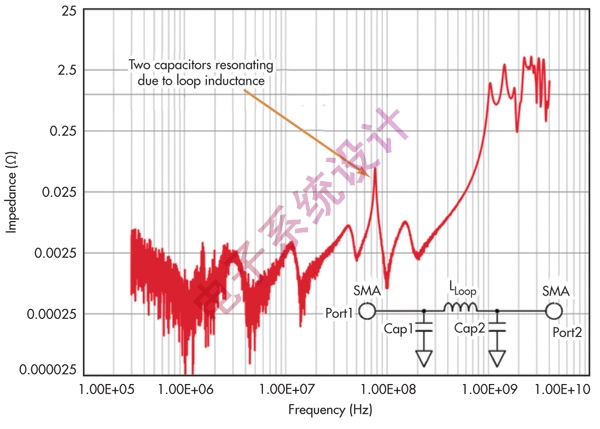

放置電容或者使用不同的電容工藝和型號(hào)都有可能形成電感環(huán)路,它們將對(duì)系統(tǒng)內(nèi)的頻率做出不同響應(yīng)以及彼此之間發(fā)生諧振(圖5)。

了解系統(tǒng)所用電容類型的頻率響應(yīng)非常重要。隨便選用電容會(huì)讓設(shè)計(jì)低阻抗PDS系統(tǒng)的努力付諸東流。

要設(shè)計(jì)出合格的PDS,需要使用各種電容(再見圖4)。PCB上使用的典型電容值只能將直流或者接近直流的約500MHz頻率范圍內(nèi)的阻抗降低。在500MHz以上時(shí),電容將由PCB形成的內(nèi)部電容決定。電源平面和接地平面是否疊置得足夠緊密?

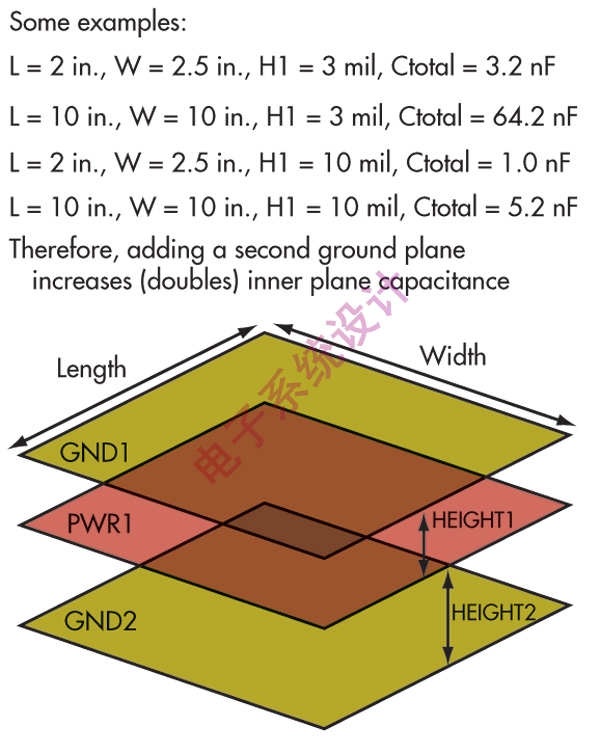

為此,請(qǐng)?jiān)O(shè)計(jì)一個(gè)支持較大平面電容的PCB層疊結(jié)構(gòu)。例如,六層堆疊結(jié)構(gòu)可能包含頂部信號(hào)層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號(hào)層。規(guī)定第一接地層和第一電源層在層疊結(jié)構(gòu)中彼此靠近。將這兩層的間距設(shè)定為2~4mil,將形成一個(gè)固有的高頻平面電容。

圖5:通過了解電容類型和布局可將環(huán)路電感降至最小,從而防止出現(xiàn)較高的PDS阻抗。

此電容的最大優(yōu)點(diǎn)在于它免費(fèi),您只需要在PCB制造筆記中進(jìn)行說明即可。如果必須分割電源平面,并在同一平面上具有多個(gè)VDD電源軌,則應(yīng)使用盡可能大的電源平面。不要留下空洞,同時(shí)還應(yīng)注意敏感電路。這將使該VDD平面的電容達(dá)到最大。

如果設(shè)計(jì)允許存在額外的層(本例中由六層變?yōu)榘藢樱瑒t應(yīng)將兩個(gè)額外的接地平面放在第一和第二電源平面之間。在核心間距同樣為2~3mil的情況下,層疊結(jié)構(gòu)的固有電容將會(huì)加倍(圖6)。此結(jié)構(gòu)更易于設(shè)計(jì),然后,可添加更多分立高頻電容以保持低阻抗。

圖6:通過設(shè)計(jì)具有鄰近電源平面和地平面的PCB堆疊結(jié)構(gòu),可在PCB中得到高頻電容。這將在較高頻率下滿足較低阻抗。

對(duì)于PDS而言,將響應(yīng)電源電流需求時(shí)出現(xiàn)的電壓紋波降至最低非常重要,但這點(diǎn)卻常被忽略。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源或接地平面以及良好的PCB層疊,可以將因電路電流需求而產(chǎn)生的電壓紋波降至最低。

根據(jù)使用的去耦策略,如果系統(tǒng)設(shè)計(jì)的開關(guān)電流為1A且PDS的阻抗為10mΩ,則最大電壓紋波為10mV。計(jì)算公式很簡(jiǎn)單:V=IR。

憑借完美的PCB堆疊,便可覆蓋高頻范圍,同時(shí),在電源平面的起始入口點(diǎn)和大功率或浪涌電流器件周圍使用傳統(tǒng)去耦,便可覆蓋低頻范圍(《500MHz)。這將確保PDS阻抗在整個(gè)頻率范圍內(nèi)均為最低。

沒有必要在各處都布置電容,也沒有必要為了把電容布置在正對(duì)著每個(gè)IC的位置,而破壞所有的制造規(guī)則。如果需要采用這種過激的措施,則說明電路中存在其它問題。

圖7:注意:作為噪聲層的PCB堆疊可能位于下方,從而可能耦合信號(hào)到敏感的模擬電路、層或者平面。

平面耦合

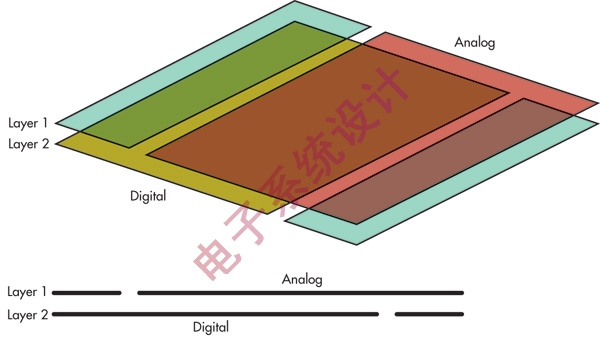

一些布局不可避免地具有重疊電路平面(圖7)。有些情況下可能是敏感的模擬平面(無(wú)論是電源、接地還是信號(hào)),下一層則是高噪聲的數(shù)字平面。大多數(shù)設(shè)計(jì)人員認(rèn)為這無(wú)關(guān)緊要,因?yàn)樵撈矫嫖挥诹硪粚印R虼耍覀儊?lái)做一個(gè)簡(jiǎn)單測(cè)試。

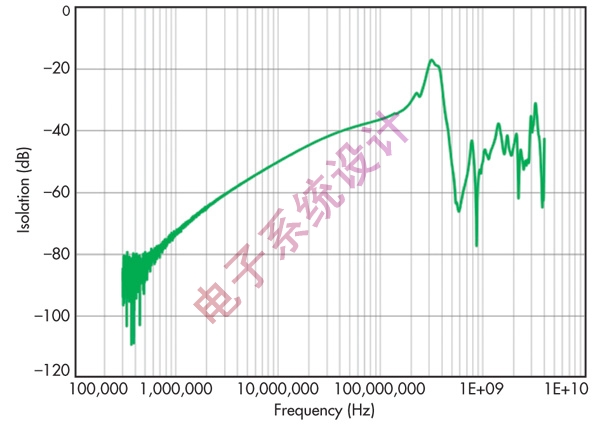

以某一層為例,在任一平面上注入信號(hào)。現(xiàn)在將與該相鄰層交叉耦合的另一層連接至頻譜分析儀。可以看到有多少信號(hào)耦合到了相鄰層吧?即使兩者間距為40mil,在某種意義上它卻仍是電容,因此,在某些頻率下仍會(huì)耦合信號(hào)至相鄰平面(圖8)。

圖8:高頻處,標(biāo)準(zhǔn)FR4材料上的層間耦合可能無(wú)處不在(40~60dB),請(qǐng)注意隔離。對(duì)于特定設(shè)計(jì)可能足夠,但隔離應(yīng)視應(yīng)用而定。

舉例來(lái)說,某層上的高噪聲數(shù)字平面具有高速開關(guān)的1V信號(hào),這意味著,另一層上將會(huì)“看到”1mV的耦合(約60dB的隔離)。對(duì)具有2Vp-p滿量程擺幅的12位模擬數(shù)字轉(zhuǎn)換器(ADC),這是2個(gè)最低有效位(LSB)的耦合。對(duì)于特定系統(tǒng)而言,這可能不成問題,但應(yīng)注意,如果提升2位(從12位增至14位),靈敏度只會(huì)提高四倍,即8個(gè)LSB。

忽略這種平面間耦合,很可能使系統(tǒng)失效,或者影響設(shè)計(jì)性能。這里必須指出的是,兩個(gè)平面間存在的耦合可能超出想象。

在感興趣的頻譜內(nèi)發(fā)現(xiàn)噪聲耦合時(shí)應(yīng)注意這一點(diǎn)。有時(shí)布局決定了非預(yù)期信號(hào)或是平面將被交叉耦合到不同的層,在調(diào)試敏感系統(tǒng)時(shí)請(qǐng)記住這一點(diǎn)。該問題可能出現(xiàn)在下面一層。

分離地

全球模擬信號(hào)鏈設(shè)計(jì)人員最常提出的問題是,使用ADC時(shí)是否應(yīng)該將地平面分離成AGND和DGND地平面?簡(jiǎn)單回答是:視情況而定。

詳細(xì)回答則是:通常不分離。在大多數(shù)情況下,盲目分離地平面只會(huì)增加返回電流的電感,因此,它所帶來(lái)的壞處大于好處。還記得公式V=L(di/dt)嗎?隨著電感增加,電壓噪聲會(huì)提高。

隨著電感增加,您一直努力降低的PDS阻抗也會(huì)增加。隨著增加ADC采樣速率的需求繼續(xù)增長(zhǎng),增加開關(guān)電流的方法卻只有這些。因此,除非有理由分離地平面,否則請(qǐng)保持這些接地連接。

關(guān)鍵是電路合理分割,這樣就不必分離地平面(圖9)。請(qǐng)注意,如果布局允許將各電路保持在各自區(qū)域內(nèi),便無(wú)需分離地平面。如此分割可以提供星型接地,因此,可將返回電流局限在特定的電路部分。例如,受尺寸限制的影響而使得電路板無(wú)法實(shí)現(xiàn)良好布局分割的情況。這可能是為了符合傳統(tǒng)設(shè)計(jì)或尺寸要求而必須將惡劣的總線電源或高噪聲的數(shù)字電路放在特定區(qū)域的緣故。這種情況下,分離地平面是實(shí)現(xiàn)良好性能的關(guān)鍵。

PCB布局實(shí)現(xiàn)高速ADC設(shè)計(jì)" border="0" height="272" src="http://files.chinaaet.com/images/2012/01/14/378d9d77-392e-4ed0-8009-90c41fe5aa35.jpg" width="600" />

圖9:對(duì)于每一應(yīng)用地平面分離可能并無(wú)必要,因?yàn)轸敯舻母咚僭O(shè)計(jì)建立在固態(tài)PCB電路分區(qū)周圍而將電流局限在特定區(qū)域。

然而,為使整體設(shè)計(jì)有效,還必須在電路板的某個(gè)地方用一個(gè)電橋或是連接點(diǎn)將這些地連接在一起。因此,應(yīng)將連接點(diǎn)均勻地分布在分離的地平面上。

最終,PCB上的連接點(diǎn)往往成為使返回電流通過,而不會(huì)導(dǎo)致性能降低或者強(qiáng)行將返回電流耦合至敏感電路的最佳位置。如果此連接點(diǎn)位于轉(zhuǎn)換器附近或下方,則根本無(wú)需分離接地。

本文小結(jié)

由于關(guān)于最佳布局的評(píng)論太多,所以在布局上的考慮總是令人困惑。技術(shù)和原則一直是ADI“設(shè)計(jì)文化”的一部分。在工程師傾向于借鑒以往設(shè)計(jì)經(jīng)驗(yàn)的同時(shí),產(chǎn)品的上市壓力也使設(shè)計(jì)人員不愿去更改或是嘗試新事物。他們拘泥于風(fēng)險(xiǎn)權(quán)衡,直至系統(tǒng)內(nèi)出現(xiàn)了重大問題。

在評(píng)估板、模塊和系統(tǒng)層面,簡(jiǎn)單的單一接地適合于所有情況。良好的電路分割才是關(guān)鍵,這也將影響到平面和相鄰層的布局。請(qǐng)注意,如果敏感平面在高噪聲數(shù)字平面之上,則有可能發(fā)生交叉耦合。

組裝也是重要因素。提供給PCB車間或組裝車間的制造筆記應(yīng)善加利用,從而確保IC裸露焊盤和PCB之間具有可靠連接。因組裝不良而導(dǎo)致的系統(tǒng)性能欠佳不計(jì)其數(shù)。

不過,靠近電源平面入口點(diǎn)和轉(zhuǎn)換器VDD引腳的去耦總是有利的。對(duì)于增加的、固有高頻去耦,應(yīng)利用4密爾(mil)或間距更小的緊密電源平面和地平面。此方法不會(huì)帶來(lái)額外成本,只需花五分鐘更新PCB制造筆記。

在設(shè)計(jì)高速、高分辨率轉(zhuǎn)換器布局時(shí),無(wú)法照顧到所有的具體特性。每一應(yīng)用各不相同,有的甚至更為獨(dú)特。不過,上述關(guān)鍵點(diǎn)卻可以幫助設(shè)計(jì)人員加深對(duì)未來(lái)系統(tǒng)設(shè)計(jì)的理解。