單片機(jī)雙機(jī)并行通信中所遇問題及解決方法

摘要: 本系統(tǒng)采用的CPLD為 ATMEL公司生產(chǎn)的ATF1540AS器件,該器件是一種高性能、高密度復(fù)合可編程邏輯器件,簡(jiǎn)稱CPLD,它利用ATMEL 的電可擦除存儲(chǔ)器技術(shù),有 64個(gè)邏輯宏單元和68個(gè)I/O端口,很容易和多個(gè)TTL、SSI、MSI、LSI和經(jīng)典的PLDS組合使用。每個(gè)宏單元包括積項(xiàng)和積項(xiàng)多路選擇器、 OR/XOR/CASCADE邏輯、觸發(fā)器、輸出選擇和使能、輸入邏輯陣列五個(gè)部分。ATF1504AS的增強(qiáng)選路開關(guān)增加了可用的門計(jì)數(shù),提高了管腳鎖存設(shè)計(jì)修改的成功率。

Abstract:

Key words :

1 引言

本系統(tǒng)主要應(yīng)用于雙CPU電腦刺繡機(jī)中。為了減輕下位機(jī)的控制負(fù)擔(dān),更好的完成花樣的刺繡。其次為下一步脫機(jī)工作做準(zhǔn)備(即在機(jī)器刺繡的同時(shí),為刺繡下一個(gè)花樣做準(zhǔn)備工作),這樣一來,可以進(jìn)一步提高工作效率。由于系統(tǒng)在最初研發(fā)中遭遇程序跑飛問題的困擾,于是提出了采用CPLD(可編程邏輯器件)的方式,以解決通訊干擾問題。

本系統(tǒng)采用的CPLD為 ATMEL公司生產(chǎn)的ATF1540AS器件,該器件是一種高性能、高密度復(fù)合可編程邏輯器件,簡(jiǎn)稱CPLD,它利用ATMEL 的電可擦除存儲(chǔ)器技術(shù),有 64個(gè)邏輯宏單元和68個(gè)I/O端口,很容易和多個(gè)TTL、SSI、MSI、LSI和經(jīng)典的PLDS組合使用。每個(gè)宏單元包括積項(xiàng)和積項(xiàng)多路選擇器、 OR/XOR/CASCADE邏輯、觸發(fā)器、輸出選擇和使能、輸入邏輯陣列五個(gè)部分。ATF1504AS的增強(qiáng)選路開關(guān)增加了可用的門計(jì)數(shù),提高了管腳鎖存設(shè)計(jì)修改的成功率。

2 系統(tǒng)結(jié)構(gòu)

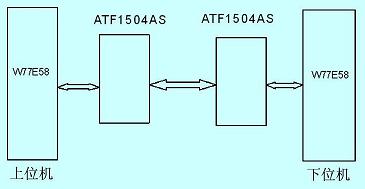

系統(tǒng)的CPU采用W77E58,由ATF1504AS構(gòu)成通信接口,系統(tǒng)框圖如圖1所示。

圖1 雙機(jī)通信框圖

2.1 問題提出

電腦刺繡機(jī)為達(dá)到良好的人機(jī)界面交互功能,采用上下位機(jī)方式,下位機(jī)主要進(jìn)行繡花動(dòng)作的控制,上位機(jī)主要進(jìn)行花樣的跟蹤。為了實(shí)現(xiàn)繡花的同時(shí)在液晶屏上進(jìn)行繡花跟蹤,單CPU方式存在系統(tǒng)資源透支, CPU處理數(shù)據(jù)將十分困難,于是提出了采用雙CPU的工作方式,但同時(shí)帶來一個(gè)問題—雙CPU的通信問題。

2.2 解決方案

(1) 采用串行通信方式

優(yōu)點(diǎn):在由單片機(jī)組成的多機(jī)方式中,串行接口方式是最常用的。串行通信方式接口電路簡(jiǎn)單,可以方便實(shí)現(xiàn)長(zhǎng)距離傳輸。抗干擾能力比較好。

缺點(diǎn):傳輸數(shù)據(jù)慢,不適合實(shí)時(shí)數(shù)據(jù)傳輸。在數(shù)據(jù)傳輸要求高的情況下,容易造成瓶頸堵塞現(xiàn)象。

(2) 采用并行通信方式

優(yōu)點(diǎn):并行通信傳輸數(shù)據(jù)快,適合進(jìn)行實(shí)時(shí)控制。

缺點(diǎn):抗干擾能力差,不適合長(zhǎng)距離傳輸,最大距離不超過5m。

由于本系統(tǒng)對(duì)數(shù)據(jù)傳輸?shù)膶?shí)時(shí)性要求比較高,并且上下位機(jī)之間的距離不超過3m,進(jìn)行適當(dāng)?shù)目垢蓴_措施,完全可以達(dá)到系統(tǒng)的要求,所以確定采用并行通信方式。

2.3 具體措施

(1) 采用ATF1504AS(可編程邏輯器件)進(jìn)行并行通信,減少分立器件所產(chǎn)生的雜散電容而帶來的噪聲干擾。

(2) 在輸入數(shù)據(jù)端加斯密特電路(74LS14),將外部傳輸線上耦合噪聲濾除掉。從而提高總線接收的抗干擾性能。

(3) 采用三態(tài)門驅(qū)動(dòng)方式可以提高總線的抗干擾能力,因?yàn)槿龖B(tài)門有三種狀態(tài)輸出,既所謂的低阻高電平、低阻低電平、高阻態(tài)(禁態(tài))。由于三態(tài)門的輸入具有的三態(tài)性,所以使三態(tài)門的信號(hào)源的負(fù)擔(dān)減輕。有利于提高速度和抗干擾能力。

3 雙CPU通信原理設(shè)計(jì)

3.1 雙CPU通信原理圖

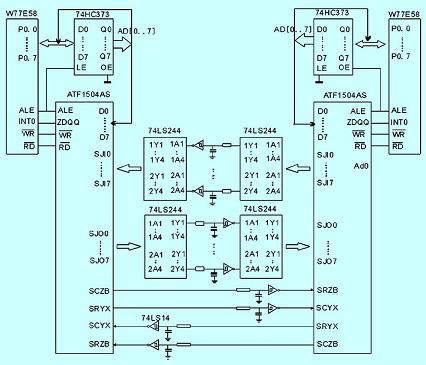

從圖2雙CPU通信原理圖中可以看出,在輸入接口上都接上74LS14斯密特電路和74LS244三態(tài)門驅(qū)動(dòng)器,以提高抗干擾能力。在SRZB、SCYX(上位機(jī))及SRZB、SCYX(下位機(jī))的握手信號(hào)線上接入74LS14斯密特電路,以提高抗干擾能力。

圖2 雙機(jī)通信原理圖

3.2 ATF1504AS內(nèi)部原理圖

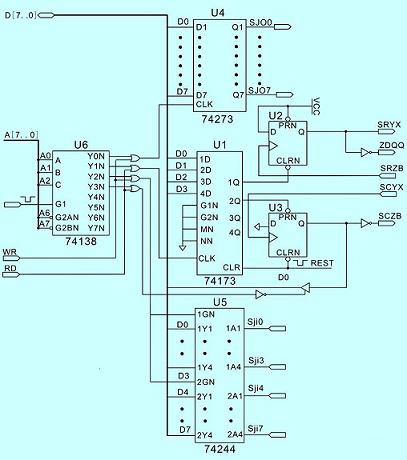

由于篇幅有限,僅列出上位機(jī)的ATF1504AS的內(nèi)部原理圖如圖3,下位機(jī)的ATF1504AS的內(nèi)部原理圖與此相類似。

圖3 ATF1504AS內(nèi)部原理圖

4 系統(tǒng)工作原理

4.1 上位機(jī)輸入數(shù)據(jù)

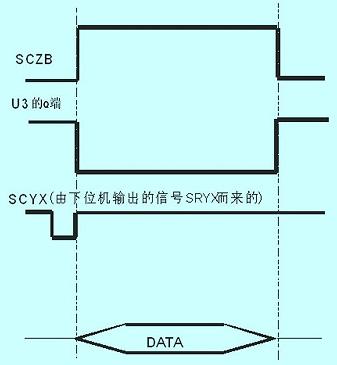

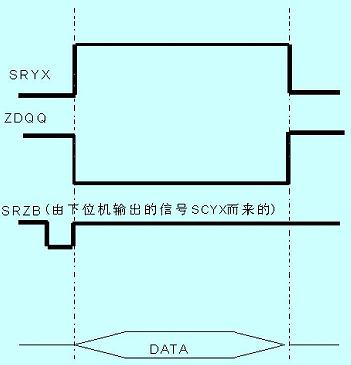

如圖3所示。在輸入數(shù)據(jù)以前,通過對(duì)U1(74173)給U2(D觸發(fā)器)進(jìn)行初始化,即對(duì)U2的CLRN端輸入一上升沿的脈沖,使U2清零。此時(shí)上位機(jī) SRYX端為低電平,ZDQQ端為高電平。此時(shí)為接收數(shù)據(jù)做好準(zhǔn)備。當(dāng)下位機(jī)接收到上位機(jī)的SRYX端輸出的低電平時(shí),就可以發(fā)送數(shù)據(jù)到鎖存器中,緊接著給上位機(jī)的SRZB端輸出一個(gè)上升沿脈沖,U2的Q端(SRYX端)輸出正脈沖,ZDQQ端經(jīng)過反相器輸出負(fù)脈沖。上位機(jī)在檢測(cè)到ZDQQ端為低電平時(shí),將數(shù)據(jù)線上的數(shù)據(jù)取出。緊接著通過對(duì)UI給U2進(jìn)行進(jìn)行初始化,完成對(duì)一個(gè)字節(jié)的讀取,并為讀取下一個(gè)字節(jié)做好準(zhǔn)備。上位機(jī)輸入數(shù)據(jù)信號(hào)波形圖如圖5所示。

圖4 上位機(jī)輸出數(shù)據(jù)時(shí)信號(hào)波形圖

圖5 上位機(jī)輸入數(shù)據(jù)時(shí)信號(hào)波形圖

4.2 上位機(jī)輸出數(shù)據(jù)

如圖3所示在輸出數(shù)據(jù)以前,通過對(duì)U1 (74173)給U3(D觸發(fā)器)進(jìn)行初始化,即對(duì)U3的PRN端輸入一上升沿的脈沖,使U3輸出置1。此時(shí)上位機(jī)的SCZB端經(jīng)反相器輸出低電平,U3 的Q端為高電平。此時(shí)為發(fā)送數(shù)據(jù)做好準(zhǔn)備。當(dāng)上位機(jī)的SCYX端接收輸入的上升沿脈沖時(shí),U3的Q端為低電平,當(dāng)CPU檢測(cè)到Q端為低電平時(shí),就可以發(fā)送數(shù)據(jù)到鎖存器中,緊接著通過上位機(jī)的SCZB端向下位機(jī)SRZB端輸出一個(gè)上升沿脈沖。表示已發(fā)送數(shù)據(jù),接著通過對(duì)U1給U2進(jìn)行進(jìn)行初始化。完成對(duì)一個(gè)字節(jié)的輸出,并為輸出下一個(gè)字節(jié)做好準(zhǔn)備,上位機(jī)輸出數(shù)據(jù)信號(hào)波形圖如圖4所示。

5 軟件設(shè)計(jì)

5.1 程序流程設(shè)計(jì)

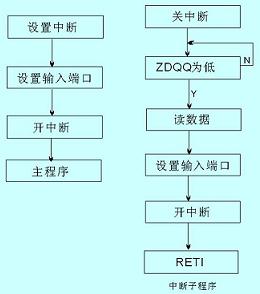

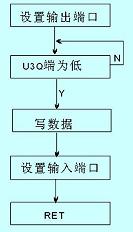

圖6示出輸入數(shù)據(jù)流程圖,圖7示出輸出數(shù)據(jù)流程圖。

圖6 輸入數(shù)據(jù)流程

圖7 數(shù)據(jù)輸出程序流程圖

5.2 部分程序清單

(1) 輸入數(shù)據(jù)程序清單

ORG 0000H

JMP START

ORG 0003H

JMP RESEVE

START: MOV TCON,#0 ;設(shè)置中斷INT0

MOV TMOD,#11H

CALL SZSRDK ;設(shè)置輸入端口

MOV IE,#81H

MOV IP,#1 ;開中斷

..

..

..

RESEVE: CLR EA ;開中斷

PUSH PSW

PUSH DPH

PUSH DPL

RESEV1: JB ZDQQ,RESEV1

;判ZDQQ是否為低

MOV DPTR,#ADDR0

;為U5(輸入數(shù)據(jù)端口)的地址

MOVX A, @DPTR

..

..

CALL SZSRDK

POP DPL

POP DPH

POP PSW

SETB EA

RETI

SZSRDK: CLRN EQU 2CH.0

CLR CLRN ;

MOV DPTR,#ADDR1

;為U1的地址

MOV A,2CH

MOVX @DPTR,A

SETB CLRN

MOV A,2CH

MOV DPTR,#ADDR1

MOVX @DPTR,A

RET

(2) 輸出數(shù)據(jù)程序清單

SEND: MOV DPTR,#ADDR3

MOVX A,@DPTR

JB ACC.0,SEND

;為U3的Q端輸出

MOV DPTR,#ADDR4

;為U4(輸出端口)的地址

MOVX @DPTR,A

CALL SZSCDK

RET

SZSCDK: PRN EQU 2CH.1

SETB PRN

MOV DPTR,#ADDR1

;為U1的地址

MOV A,2CH

MOVX @DPTR,A

CLR PRN

MOV DPTR,#ADDR1

MOV A,2CH

MOVX @DPTR,A

RET

6 結(jié)束語(yǔ)

設(shè)計(jì)中采用了AT1504AS器件,該器件實(shí)現(xiàn)了硬件設(shè)計(jì)軟件化,方便了硬件設(shè)計(jì),縮短了設(shè)計(jì)周期,降低了設(shè)計(jì)成本,應(yīng)用也十分方便,該系統(tǒng)經(jīng)過采取以上措施后,以達(dá)到最初的設(shè)計(jì)要求。現(xiàn)產(chǎn)品已投放市場(chǎng),市場(chǎng)的反映良好。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。