基于FPGA的SoC外部組件控制器IP的設(shè)計

摘要: 組件控制器的設(shè)計是SOC設(shè)計的重要組成部分。采用FPGA是完成組件控制器設(shè)計的有效手段。通過LCD控制器的設(shè)計和仿真,說明基于FPGA的組件控制器可以用一條指令完成原來許多條指令才能完成的操作,可以大大提高系統(tǒng)的運行效率。因此,這是一項有意義的工作。本文作者創(chuàng)新點在于把FPGA設(shè)計和SOC的組件控制器聯(lián)系起來,并通過一個具體例子介紹了如何設(shè)計單指令驅(qū)動的組件控制器。

Abstract:

Key words :

1 引言

嵌入式系統(tǒng)已經(jīng)發(fā)展成為應(yīng)用最廣的計算機系統(tǒng)。SoC(System on a Chip)則是嵌入式系統(tǒng)的研究和開發(fā)熱點。SOC的核心概念是把整個系統(tǒng)集成到一片半導(dǎo)體芯片上。目前SoC的中文名稱還不統(tǒng)一,可被叫做集成系統(tǒng)芯片、系統(tǒng)芯片或片上系統(tǒng)等。基于可編程器件FPGA(Field programmable Gate Arrays)的SoC可被稱作SoPC(System on a Programmable Chip)或PSoC(Programmable SoC)。基于FPGA的設(shè)計為可重配置(reconfigurable)的SoC的開發(fā)帶來了方便。SOC運用現(xiàn)代計算機和微電子學(xué)的高技術(shù),實現(xiàn)單片系統(tǒng)集成,減小了體積、提高了運行效率、增強了可靠性、降低了功耗、減少了成本,因此被稱作嵌入式系統(tǒng)應(yīng)用的理想結(jié)構(gòu)和高端形式。

IP(IntellectualProperty)是SoC設(shè)計不可或缺的部分。在某種程度上,可以說SOC=MP+IP。微處理器MP(Microprocessor)是SOC的核心。IP是SOC各種功能實現(xiàn)的模塊。IP模塊也被稱作IP核,IP核又可分為硬核、軟核、固核。由于SOC是針對某種應(yīng)用或?qū)ο笤O(shè)計的專用系統(tǒng),系統(tǒng)的實現(xiàn)很大程度上依賴于功能模塊的設(shè)計。此外,許多MP核可以在市場上買到。因此,IP模塊的開發(fā)已成為許多用戶設(shè)計SOC的主要工作。

本文側(cè)重于介紹IP模塊中組件控制器的設(shè)計和實現(xiàn)。一個基于FPGA的LCD控制器設(shè)計作為例子被介紹。這個組件控制器設(shè)計屬于固核IP設(shè)計,也就是軟硬結(jié)合的方法。設(shè)計內(nèi)容主要包括電路結(jié)構(gòu)、VHDL框架和仿真結(jié)果。該設(shè)計實現(xiàn)了面向可重配置SOC的單指令驅(qū)動LCD操作。

2 SoC組件與組件控制器

SoC組件是SoC為實現(xiàn)某種操作功能所需要的器件或設(shè)備。這些組件可以是內(nèi)部的也可以是外部的,如LCD、鍵盤、設(shè)備驅(qū)動器等是外部組件,電子轉(zhuǎn)換器、變換器、放大器等則屬于內(nèi)部組件。無論是內(nèi)部,還是外組件,其控制單元都要被設(shè)計在SOC內(nèi)部。作為一個系統(tǒng)的核心,SOC要完成運行、操作或控制功能,必須有相應(yīng)的組件配合。而多數(shù)組件,尤其是外部組件在SOC內(nèi)都要有一個對應(yīng)的控制器。所以,為了實現(xiàn)應(yīng)用對象操作,SOC要設(shè)計相當(dāng)數(shù)量的組件控制器。組件控制器的設(shè)計,對SOC而言就是一些IP模塊的設(shè)計。

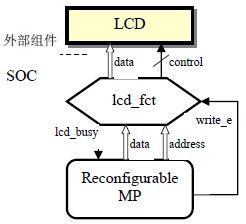

SoC與外部組件的基本關(guān)系見圖1。相對于外部組件而言,SoC由微處理器核MP(microprocessor)和相關(guān)的控制器IP構(gòu)成。為了得到最優(yōu)的控制效率,SoC的MP常常被設(shè)計成可重配置(reconfigurable)的MP。這意味著用戶可對MP的一些配置進行修改和添加以適應(yīng)應(yīng)用系統(tǒng)的需要,如用戶可以對MP的指令系統(tǒng)進行重新配置,設(shè)計加入用戶需要的專用指令。為了區(qū)別于一般的MP,圖1中的給出了SoC-MP來代表用于SoC的MP核

圖1 SOC與外部組件的基本關(guān)系

SoC的組件控制器與專用指令配合可以實現(xiàn)一些復(fù)雜操作的單指令運行,從而大大提高了SOC應(yīng)用系統(tǒng)的操作速度和運行效率。這也正是嵌入式系統(tǒng)的專用設(shè)計特性和高效控制優(yōu)勢的體現(xiàn)。

盡管SoC的IP核分為硬核、軟核、固核,對于非專業(yè)集成電路設(shè)計的用戶來說,多數(shù)采用基于FPGA的設(shè)計方法。實際上也就是軟硬結(jié)合的IP固核設(shè)計。本文介紹的是一種用VHDL硬件描述語言在FPGA上設(shè)計SOC外部組件控制器IP的方法。

3 LCD控制器的設(shè)計

液晶顯示器LCD(Liquid Crystal Display)是SoC的一種外部組件,會經(jīng)常被用到。為了實現(xiàn)SoC對LCD的高效管理,要設(shè)計一個LCD控制器IP模塊。這個模塊被命名為lcd_fct。外部組件LCD與SOC的關(guān)系與控制結(jié)構(gòu)可參考圖2。

對照圖1可以看出,圖2中的lcd_fct是外部組件控制器IP,它位于LCD和MP之間,通過數(shù)據(jù)(data)、地址線(address)、控制(control,write_e)和信號線(lcd_busy)等與MP和LCD建立聯(lián)系。

圖2 外部組件LCD的SOC控制結(jié)構(gòu)

在這個設(shè)計中對LCD控制器lcd_fct的要求是:lcd_fct接受來自MP的指令,如初始化、清屏和顯示等。lcd_fct按照指令的要求產(chǎn)生一系列控制信號和相應(yīng)的時序來控制LCD模塊完成相應(yīng)的操作。實際上,lcd_fct對LCD模塊的操控主要包括LCD初始化、清屏、傳送顯示數(shù)據(jù)和地址。

當(dāng)lcd_fct的輸入信號reset是低電平時,復(fù)位電路(ResetCircuit)開始工作,進行初始化操作、對標(biāo)志和狀態(tài)清零、設(shè)定相關(guān)常數(shù)等。

時鐘調(diào)節(jié)電路(ClockRegulator)主要為定時器提供具有高質(zhì)量波形的時鐘。為滿足運行中不同時序的需要,lcd_fct中設(shè)計了微秒定時器(μsTimer)和毫秒定時器(msTimer)。定時的時間常數(shù)被放在時間常數(shù)寄存器(TimeConstantRegister)中。

從MP來的地址(addrin)和控制(write_e)信息被送到譯碼器(Decoder)。譯碼器根據(jù)不同的地址和控制信息產(chǎn)生相應(yīng)的指令標(biāo)志,如復(fù)位、清零等。并把指令標(biāo)志送給控制電路(ControlCircuit)。

控制電路(ControlCircuit)是lcd_fct的核心。它控制數(shù)據(jù)輸入寄存器(Data_inRegister)、數(shù)據(jù)輸出寄存器(Data_outRegister)、狀態(tài)寄存器(StateRegister)、控制寄存器(ControlRegister)和時間常數(shù)寄存器(TimeConstantRegister)。控制電路根據(jù)指令標(biāo)志和時序來操作不同的寄存器,實現(xiàn)lcd_fct的管理和運行。

數(shù)據(jù)輸入寄存器接受來自MP的數(shù)據(jù)并根據(jù)需要送數(shù)據(jù)到數(shù)據(jù)輸出寄存器。數(shù)據(jù)輸出寄存器把數(shù)據(jù)通過數(shù)據(jù)線lcd_db送到LCD模塊的數(shù)據(jù)總線上。這個數(shù)據(jù)既可能是要顯示的數(shù)據(jù),也可能是指令。

控制寄存器產(chǎn)生操作LCD的控制信號,如LCD中選信號(lcd_e)、LCD內(nèi)部寄存器選擇信號(lcd_rs)和LCD讀寫信號(lcd_r_w)。

狀態(tài)寄存器在LCD處于工作下,會產(chǎn)生LCD繁忙信號(lcd_busy)。這意味著,LCD此時不會接受其它指令。與其它信號不同,lcd_busy是發(fā)送給MP的。

實際上lcd_fct的運行操作主要是對各種控制、狀態(tài)和數(shù)據(jù)信號進行管理。

4 FPGA設(shè)計和仿真

在lcd_fct的FPGA設(shè)計中,主要采用的VHDL語言的程序設(shè)計[7]、MAXPlus-II仿真以及SOC和LCD的實際連接調(diào)試。lcd_fct的HVDL設(shè)計框架如下:

Library

Entity lcd_fct is Port();

End lcd_fct;

Architecture struct of lcd_fct is Signal Constant

Begin

Res: process;

Clk: clk_div;

LCD: process;

Begin

If init then Initialization;

Elsif clr then Clear LCD;

Elsif addr then Write address to LCD RAM;

Elsif data then Write data to LCD RAM;

End if;

End process;

Us: ustimer;

Ms: mstimer;

End truct;

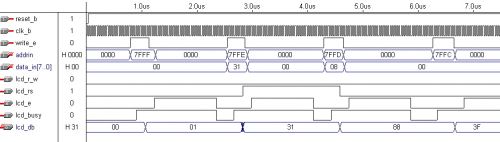

LCD控制器IP模塊lcd_fct的仿真結(jié)果如圖3所示。在圖中左側(cè)的信號就是lcd_fct的輸入/輸出信號。

圖3 lcd_fct的功能仿真

當(dāng)把write_e設(shè)置成高電平時,指令寫入lcd_fct。對于讀寫控制信號lcd_r_w來說,低電平為寫操作,高電平為讀操作。由于該仿真都是lcd_fct對LCD進行寫操作,lcd_r_w始終為低電平。圖中通過addrin的變化來代表不同的指令。

在addrin等于7FFF時,lcd_db被賦值01。這意味著LCD被清屏。當(dāng)addrin等于7FFE,且data_in送入31時,lcd_db被賦值31,LCD就會顯示“1”。Addrin被設(shè)置成7FFD,且data_in等于8時,被顯示的字符將出現(xiàn)在顯示屏的第8個字符的位置,實現(xiàn)了定位顯示功能。

當(dāng)addrin被賦值7FFC時,LCD被初始化。初始化包括功能設(shè)置、關(guān)閉顯示、打開顯示、清屏、顯示移位和工作方式設(shè)置等操作。

由此可見,只要在SOC的MP中加入適當(dāng)?shù)闹噶睿梢詫ddrin進行控制,SOC就可以完成對LCD的管理。由于本設(shè)計中SOC的MP是可重配置MP,添加或修改指令是不存在問題的。仿真表明,lcd_fct的設(shè)計達到了設(shè)計目標(biāo),操作結(jié)果是令人滿意的。一般的LCD程序控制完成一項操作(如初始化)需要執(zhí)行多條軟件指令。用FPGA設(shè)計的lcd_fct只要一條指令就能完成相應(yīng)的操作,而且是硬件運行,效率提高了許多倍。

5 結(jié)論

組件控制器的設(shè)計是SOC設(shè)計的重要組成部分。采用FPGA是完成組件控制器設(shè)計的有效手段。通過LCD控制器的設(shè)計和仿真,說明基于FPGA的組件控制器可以用一條指令完成原來許多條指令才能完成的操作,可以大大提高系統(tǒng)的運行效率。因此,這是一項有意義的工作。

本文作者創(chuàng)新點在于把FPGA設(shè)計和SOC的組件控制器聯(lián)系起來,并通過一個具體例子介紹了如何設(shè)計單指令驅(qū)動的組件控制器。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。