引 言

Flash存儲器又稱閃速存儲器,是20世紀(jì)80年代末逐漸發(fā)展起來的一種新型半導(dǎo)體不揮發(fā)存儲器。它兼有RAM和ROM的特點(diǎn),既可以在線擦除、改寫,又能夠在掉電后保持?jǐn)?shù)據(jù)不丟失。

NOR Flash是Flash存儲器中最早出現(xiàn)的一個品種,與其他種類的Flash存儲器相比具有以下優(yōu)勢:可靠性高、隨機(jī)讀取速度快,可以單字節(jié)或單字編程,允許CPU直接從芯片中讀取代碼執(zhí)行等。因此NOR Flash存儲器在嵌入式系統(tǒng)應(yīng)用開發(fā)中占有非常重要的地位。本文以SST公司的NOR Flash芯片SST39SF040和MCS-51單片機(jī)為例,針對大容量NORFlash在8位低檔單片機(jī)中應(yīng)用的特殊性,詳細(xì)介紹了其接口硬件和接口軟件的設(shè)計方法。

1 SST39SF040芯片介紹

SST39SF040是SST公司最近推出的一種基于SuperFlash技術(shù)的NOR Flash存儲器,屬于SST公司并行閃速存儲器系列;適用于需要程序在線寫入或大容量、非易失性數(shù)據(jù)重復(fù)存儲的場合。

1.1 芯片內(nèi)部功能結(jié)構(gòu)和外部引腳

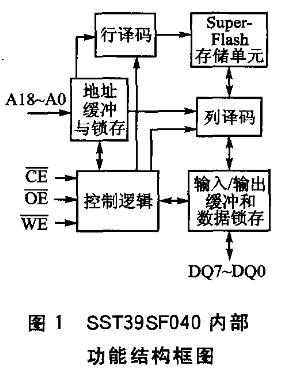

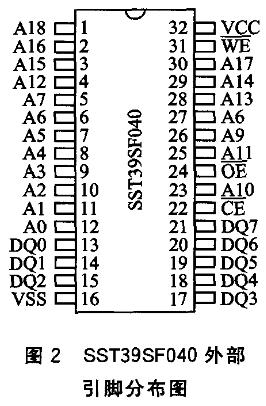

圖1是SST39SF040的內(nèi)部功能結(jié)構(gòu)框圖,由Super-Flash存儲單元、行譯碼器、列譯碼器、地址緩沖與鎖存器、輸入/輸出緩沖和數(shù)據(jù)鎖存器以及控制邏輯電路等部分組成。圖2是其外部引腳分布圖,其中A18~A0為地址線,CE為芯片選通信號,OE可作為讀信號,WE為寫信號,DQ7~DQ0為數(shù)據(jù)線。

1.2 芯片的主要特性

① 容量為512 KB,按512K×8位結(jié)構(gòu)組織。

② 采用單一的5 V電源供電,編程電源VPP在芯片內(nèi)部產(chǎn)生。

③ 芯片可反復(fù)擦寫100 000次,數(shù)據(jù)保存時間為100年。

④ 工作電流典型值為10 mA,待機(jī)電流典型值為30μA。

⑤ 扇區(qū)結(jié)構(gòu):扇區(qū)大小統(tǒng)一為4 KB。

⑥ 讀取、擦除和字節(jié)編程時間的典型值:數(shù)據(jù)讀取時間為45~70 ns;扇區(qū)擦除時間為18 ms,整片擦除時間為70 ms;字節(jié)編程時間為14μs。

⑦ 有記錄內(nèi)部擦除操作和編程寫入操作完成與否的狀態(tài)標(biāo)志位。

⑧ 具有硬、軟件數(shù)據(jù)保護(hù)功能。

⑨ 具有地址和數(shù)據(jù)鎖存功能。

1.3 芯片的操作

1.3.1 芯片的軟件操作命令序列

SST39SF040的軟件操作可以分成兩類:普通讀操作和命令操作。

普通讀操作非常簡單,與RAM的讀操作類似,當(dāng)OE和CE信號同時為低電平時,即可從芯片讀出數(shù)據(jù)。

芯片的命令操作包括芯片的識別、字節(jié)編程、扇區(qū)擦除以及整片擦除等。這些操作分別由各自的軟件操作命令序列來完成,如表1所列。其中,BA為待編程字節(jié)的地址,Data為字節(jié)編程數(shù)據(jù),SAX為待擦除扇區(qū)的地址。命令中的地址只有低15位有效,高4位可任意設(shè)置為“0”或“1”。

SST39SF040的軟件操作命令序列實際上是由一個或多個總線寫操作組成的。以SST39SF040的扇區(qū)擦除為例,其操作過程包括3個步驟:第1步,開啟擦除方式,用表1中給出的第1至第5周期的總線寫操作來實現(xiàn);第2步,裝載扇區(qū)擦除命令(30H)和待擦除扇區(qū)的地址,用其對應(yīng)的第6周期的總線寫操作來實現(xiàn);第3步,進(jìn)行內(nèi)部擦除。內(nèi)部擦除時間最長為25 ms。

總線寫操作時,OE必須保持為高電平,CE和WE應(yīng)為低電平。地址和數(shù)據(jù)的鎖存由CE和WE兩個信號的邊沿進(jìn)行控制。它們當(dāng)中后出現(xiàn)的下降沿將鎖存地址,先出現(xiàn)的上升沿將鎖存數(shù)據(jù)。

1.3.2 字節(jié)編程和擦除操作的狀態(tài)檢測

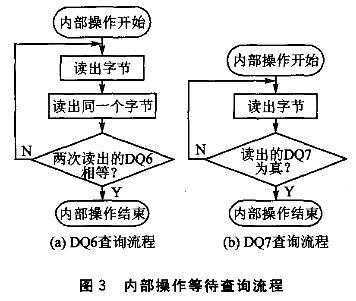

芯片在進(jìn)行內(nèi)部字節(jié)編程或擦除操作時都需要花費(fèi)一定的時間,雖然可以采用固定的延時來等待這些操作的完成,但為了優(yōu)化系統(tǒng)的字節(jié)編程和擦除操作時間,以及時判斷內(nèi)部操作的完成與否,SST39SF040提供了兩個用于檢測的狀態(tài)位,即跳變位DQ6和數(shù)據(jù)查詢位DQ7。在芯片進(jìn)行內(nèi)部操作時,只要根據(jù)圖3的流程對DQ6或者DQ7進(jìn)行查詢就能及時作出判斷。

2 SST39SF040與MCS-51的接口設(shè)計

2.1 硬件設(shè)計

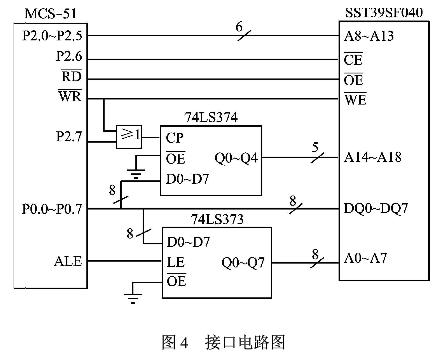

硬件設(shè)計就是搭建合適的接口電路,將SST39SF040連接到MCS-51的系統(tǒng)總線上。根據(jù)SST39SF040和MCS-51系列單片機(jī)的結(jié)構(gòu)特性,我們發(fā)現(xiàn)SST39SF040的數(shù)據(jù)線和讀、寫信號線可以很容易地連接到MCS-51的系統(tǒng)總線上,所以要考慮的主要問題是SST39SF040地址線的連接。由于其容量已經(jīng)超出了MCS-51的尋址范圍,19根地址線無法全部連接到MCS-51的地址總線上,因此必須在該系統(tǒng)中進(jìn)行進(jìn)一步的存儲器擴(kuò)展。存儲器擴(kuò)展通常可利用單片機(jī)空閑的I/O口線作為頁面地址輸出引腳來實現(xiàn)。但是許多應(yīng)用系統(tǒng)當(dāng)中,單片機(jī)的I/O口線都是非常緊張的,在沒有多余的I/O口線時,頁面地址就必須提前從數(shù)據(jù)總線輸出并存放在鎖存器中備用。具體做法是:將鎖存器直接掛在數(shù)據(jù)總線上,為其安排一個I/O地址,從而構(gòu)成頁面寄存器,在訪問存儲器時,提前將頁面地址作為數(shù)據(jù)寫入頁面寄存器即可。

根據(jù)以上分析可設(shè)計出SST39SF040與MCS-51之間的接口電路,如圖4所示。本系統(tǒng)中,將512 KB的存儲器分為32頁面,每頁大小為16 KB。由此可得,頁面地址需要5位,頁內(nèi)偏移量需要14位。頁面地址的給出是在進(jìn)行存儲器訪問之前完成的,具體的方法是:用一條“MOVX"’命令將頁面地址輸出到鎖存器74LS374中,再由74LS374將頁面地址保持在存儲器的地址引腳A14~A18上。頁內(nèi)偏移量則直接在存儲器的讀寫命令中給出,執(zhí)行命令時,低8位地址A0~A7從P0口輸出到74LS373中保持;地址A8~A13則由單片機(jī)的P2.0~P2.5直接提供。以上分時輸出的地址信號A0~A18將在讀/寫控制信號開始作用后,同時有效,以實現(xiàn)對SST39SF040的512KB全地址空間的訪問。P2.6和P2.7分別用作SKT39SF040和鎖存器74LS374的片選信號,SST39SF040的片選信號地址范圍是8000H~BFFFH,74LS374的片選信號地址范圍是4000H~7FFFH。

2.2 軟件設(shè)計

軟件設(shè)計就是編寫對SST39SF040的操作程序,包括字節(jié)讀出、扇區(qū)或整片擦除以及字節(jié)編程等。下面給出第1個扇區(qū)的擦除程序,其中DELAY25為25 ms延時子程序,其他操作程序可參照編寫。

程序編寫過程中的難點(diǎn)是,如何將SST39SF040中待訪問的單元地址進(jìn)行分解并對應(yīng)到讀寫命令中去。以扇區(qū)擦除操作的第1個命令為例,該命令的功能是將數(shù)據(jù)AAH寫入地址5555H中。對于地址5555H,其最高5位A18~A14是01H,低14位A13~A0為1555H。最高5位地址決定的頁面號必須先作為數(shù)據(jù)寫入鎖存器74LS374中,再將數(shù)據(jù)AAH寫入該頁中由低14位地址決定的單元。寫入頁面號時,指令中的地址可在4000H~7FFFH范圍內(nèi)任選一個,即選中鎖存器74LS374;寫人數(shù)據(jù)AAH時,指令中的地址可由低14位地址1555H加上8000H得到,其值為9555H。

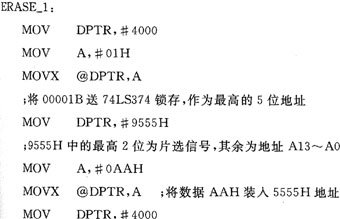

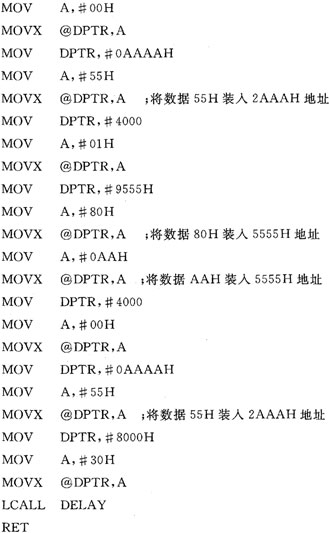

第1扇區(qū)擦除程序代碼如下:

結(jié) 語

本文從硬件和軟件兩個方面對大容量NOR Flash存儲器與8位單片機(jī)的接口技術(shù)進(jìn)行了分析、探討,給出了具體的設(shè)計方案。其思想和方法對嵌入式系統(tǒng)的應(yīng)用設(shè)計具有較高的參考價值,筆者已將它應(yīng)用到一款考勤機(jī)產(chǎn)品的設(shè)計開發(fā)當(dāng)中。