1 引言

數(shù)字信號處理技術(shù)在高分辨率圖象、視頻處理及無線通信等領(lǐng)域的廣泛應(yīng)用, 導致對高速、高精度、基于標準CMOS 工藝的可嵌入式ADC 的需求量與日俱增。對于迅速發(fā)展的基于IP 設(shè)計的片上系統(tǒng)集成技術(shù), 功耗低、面積小、可嵌入的ADC 核心模塊逐漸成為數(shù)模混合信號IC 設(shè)計的關(guān)鍵。伴隨技術(shù)的發(fā)展, ADC 的結(jié)構(gòu)出現(xiàn)了多種實現(xiàn)方案, 如過采樣Σ- △型、全并行( Flash) 、流水線和逐次逼近( Successive-approximatiON RegiSTer) 等結(jié)構(gòu)。其中, FlashADC 轉(zhuǎn)換器和Σ- Δ ADC 轉(zhuǎn)換器,它們分別滿足高速、高精度兩個極端的需求。而逐次逼近轉(zhuǎn)換器( SARADC) 具有中等速度( 5 MS/s 以下) 、中等精度( 8~18 位) 、低功耗和低成本的綜合優(yōu)勢,在更加廣闊的領(lǐng)域中得到了應(yīng)用。

由于SARADC 能夠適應(yīng)多種模擬輸入方式( 單級、雙級、差分) , 在開關(guān)、多通道應(yīng)用中能保證零數(shù)據(jù)延遲,而且速度、精度適中, 功耗、成本低, 因此, 在工業(yè)控制方面應(yīng)用廣泛, 適用于測量各種物理量的傳感器。例如, 在傳感器網(wǎng)絡(luò)中, 成千上萬個傳感器節(jié)點由1 塊電池或者幾平方毫米的太陽能電池供電, 這就要求傳感器節(jié)點面積小、成本低, 而且長時間工作消耗的能量也很小, SAR ADC 可滿足這種應(yīng)用需求。SAR ADC 還廣泛應(yīng)用于醫(yī)學儀器的成像系統(tǒng), 例如CT 掃描儀、MRI 和X 射線系統(tǒng)。SAR ADC零延遲、較高采樣速率和較好DAC 指標的優(yōu)勢, 保證了成像系統(tǒng)的高刷新速率和高成像分辨率; 而且,這種ADC 面積小、功耗低等優(yōu)勢在便攜式醫(yī)學儀器、安防安檢系統(tǒng)應(yīng)用中也得到了充分發(fā)揮。

然而, ADC 的精度和線性度會受到元件匹配度和系統(tǒng)失調(diào)以及噪聲等因素的限制, 因此通常需要采用自動失調(diào)消除、數(shù)字校準等技術(shù)以改善其性能。

激光矯正技術(shù)通常用以提高轉(zhuǎn)換器中元件的匹配度, 但也同時受到封裝時的機械應(yīng)力、制造工藝以及生產(chǎn)成本等問題的影響。

本文提供了一種基于二進制加權(quán)電容陣列DAC 的數(shù)字校準算法, 將校準誤差在芯片測試時測出并燒寫到ROM中, 并在ADC 應(yīng)用時將ROM中的數(shù)據(jù)讀出對應(yīng)加載到電容陣列中, 實現(xiàn)對DAC 的校準; 同時采用了高效的比較器消除失調(diào)技術(shù), 大大提高了ADC 的精度。

2 SAR ADC概述

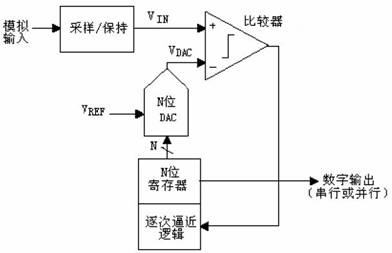

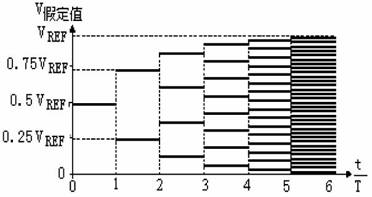

實現(xiàn)逐次逼近式ADC 的方式千差萬別, 但其基本結(jié)構(gòu)非常簡單。如圖1 所示, 模擬輸入電壓( VIN) 由采樣/ 保持電路保持。如圖2 所示, 為實現(xiàn)二進制算法, N 位寄存器首先設(shè)置在中間刻度( 即:100 …….00, MSB 位1) .這樣, 數(shù)字模擬轉(zhuǎn)換器( DAC) 輸出( VDAC) 被設(shè)為VREF/2, VDAC 是提供給ADC 的基準電壓。然后, 比較判斷VIN 是小于還是大于VDAC.如果, VIN>VDAC, 則比較器輸出邏輯高電平或1, N 位寄存器的MSB 保持為1.相反, 如果VIN < VDAC, 則比較器輸出邏輯低電平, N位寄存器的MSB 清為0.隨后, 逐次逼近控制邏輯移至下一位, 并將該位設(shè)置為高電平, 進行下一次比較。這個過程一直持續(xù)到最低有效位( LSB) .上述操作結(jié)束后就完成了轉(zhuǎn)換, N 位轉(zhuǎn)換結(jié)果儲存在寄存器內(nèi)。

圖1 N位逐次逼近A/ D 轉(zhuǎn)換器的結(jié)構(gòu)圖

圖2 A/ D 轉(zhuǎn)換器的逐次逼近過程

3 數(shù)字校準算法

目前, 工業(yè)界的SARADC 產(chǎn)品以二進制加權(quán)電容陣列、分段電容和RC 混合結(jié)構(gòu)三種結(jié)構(gòu)為主, 精度從10 位到18 位不等。其中, 二進制加權(quán)電容陣列構(gòu)成的SARADC 由于低功耗的優(yōu)勢應(yīng)用更為廣泛。

由于CMOS 工藝的限制, 無源器件的匹配精度不高, 二進制加權(quán)電容陣列SARADC 轉(zhuǎn)換器只能達到12 位精度。利用激光修正等技術(shù), 可以提高無源器件的匹配精度, 但是成本較高, 不適于工業(yè)生產(chǎn)。因此, 提出了各種自校準方法, 以提高無源器件的匹配精度, 從而提高轉(zhuǎn)換精度。如使用失調(diào)子DAC 和校準子DAC 預先對主DAC 的低位充電, 以達到校準的目的; 或使用多位非二進制加權(quán)電容DAC 和自校準算法, 使電容匹配達到較高的精度。

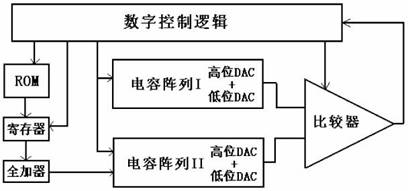

數(shù)字校準技術(shù)的意義即在ADC 正常使用前, 利用ADC 的已有電路對芯片的非線性因素進行測試,通過一定算法并根據(jù)ADC 使用時的時序產(chǎn)生相應(yīng)的校準碼, 加之于存儲器中, 在ADC 工作時通過數(shù)字控制邏輯將所存校準數(shù)據(jù)對應(yīng)加載到電路中, 從而達到校準失配的目的。對于本次SARADC 的設(shè)計, 我們采用結(jié)構(gòu)對稱的兩組18 位電容陣列數(shù)模轉(zhuǎn)換器( DAC) 輸入至比較器的正負輸入端( 準差分結(jié)構(gòu)) , 如圖3, 這種對稱輸入可以使比較器正負兩端輸入負載相等, 另一方面, 兩電容陣列的高位DAC 可對全差分信號進行采樣, 并輸出全差分的參考電壓, 而電容陣列I 的低位作為正常的低位子DAC 使用產(chǎn)生SAR 所需的參考電壓, 電容陣列II的低位則用于測量和校準兩組電容陣列高位的非線性。

圖3 數(shù)字校準算法示意圖

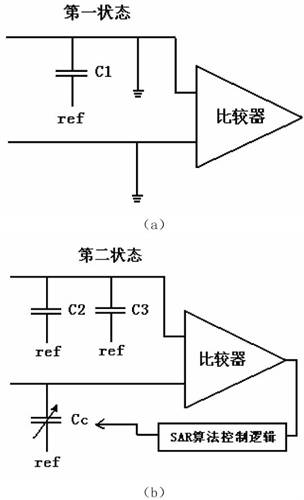

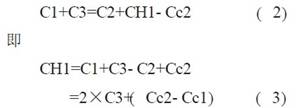

校準碼的產(chǎn)生和使用可以有不同的算法, 中介紹了一種由高位到低位校準方法, 本文設(shè)計了一種由低位到高位依次校準的方法。校準測試時電容陣列工作于兩種狀態(tài): 首先是接入一組電容, 電容陣列輸出接地, 即比較器兩輸入端均為0, 如圖4( a) 所示; 而后接入待測電容, 輸出直接接入比較器兩輸入端產(chǎn)生比較結(jié)果, 如圖4( b) 所示, 根據(jù)比較器的輸出及外部的搜索算法調(diào)整電容陣列II 低位DAC 的輸出從而測得待測電容所對應(yīng)的寄生參數(shù)( 設(shè)計要求此DAC 的精度比正常使用時的DAC 至少高1位) , 通過對此數(shù)據(jù)的處理便可以得到相應(yīng)的校準碼。為實現(xiàn)由低至高的校準, 測試時需要用到電容陣列I 低位的3 組電容C1, C2, C3, 理想情況下它們的權(quán)值應(yīng)與兩組電容陣列低位DAC 的最高位相當,考慮到不匹配問題, 可設(shè)C1≈C2≈C3, 設(shè)電容陣列II 低位DAC 接入的電容值為Cc, 根據(jù)二進制加權(quán)電容陣列性質(zhì)可知Cc 的等效輸出范圍在0 到2 倍C1 之間。初次測試時, 第一狀態(tài)僅接入C1, 第二狀態(tài)接到C2, C3 上, 同時電容陣列II 的可變Cc 接入,如圖4, 通過觀察比較器的輸出, 可知, 當比較器輸出跳變時, 有:

![]()

Cc1 為Cc 當前值, 可通過外部SAR 算法搜索得到。

圖4 ADC校準時分為兩個狀態(tài)

接下來即可對高位DAC 的最低位進行測試和校準, 設(shè)此位電容權(quán)值為CH1, 第一狀態(tài)電容接入C1, C3, 第二狀態(tài)則接入C2, CH1 和Cc, 同理可得:

依上述方法可以推得:

![]()

ΣΔCc 為每位所對應(yīng)Cc 差值與已校準低位Cc 差值的累加和, 將此電容值對應(yīng)的二進制碼用有符號數(shù)表示即所需校準碼, 隨后可以通過一次性燒寫電路存儲到ROM中, 完成SARADC 的校準測試。

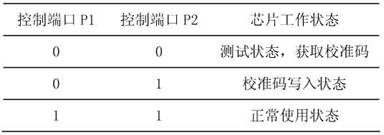

數(shù)字校準的具體實現(xiàn)方法, 可通過添加芯片狀態(tài)控制端口實現(xiàn)。如表1 中所示, 測試時將兩個控制端口接地, 應(yīng)用上述算法獲得校準碼; 隨后將控制端口P2 接至高電平, 此時將所需的校準碼寫入到芯片的ROM中; ADC 正常使用時, 將兩個控制端口接到數(shù)字電源上即可。各個工作狀態(tài)的具體邏輯電路實現(xiàn), 遵循數(shù)字集成電路設(shè)計規(guī)程, 并需針對不同狀態(tài)對芯片的端口進行配置。

表1 不同的控制端口邏輯實現(xiàn)芯片工作狀態(tài)的切換

4 比較器失調(diào)消除技術(shù)

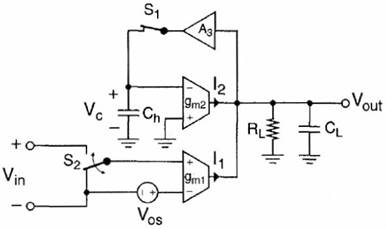

為實現(xiàn)較高的轉(zhuǎn)換速度, 本次設(shè)計采用多級比較器結(jié)構(gòu),由四級低增益放大器和一級鎖存器構(gòu)成, 而高精度的實現(xiàn)需要對比較器進行失調(diào)校準技術(shù)。比較器的失調(diào)電壓是由于電路元件的失配造成的, 這種失配通常是隨機的, 不能預先估計。失調(diào)電壓的存在會影響比較器的精度, 在較高分辨率的ADC 中, 輸入失調(diào)電壓不能太大, 這就要使用失調(diào)校準技術(shù)。失調(diào)校準技術(shù)在MOS 工藝中是適用的,這是因為MOS 器件的輸入電阻近似無限大, 使得晶體管柵極上可以長期貯存電荷, 可以將失調(diào)電壓貯存在電容上, 通過與輸入疊加來消除失調(diào)電壓的影響。本次設(shè)計, 我們采用在每一級放大器加入輔助輸入端的方法, 消除比較器的失調(diào)。

圖5 利用輔助輸入端消除失調(diào)技術(shù)

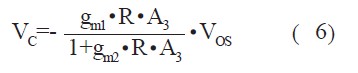

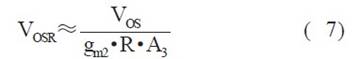

如圖5 所示, 主放大器被設(shè)計成由兩個跨導放大器組成, 由于比較時用于開環(huán), 增益較小, 可用電阻作負載; A3 為反饋環(huán)路上的調(diào)零放大器, 為高增益放大器。消失調(diào)時首先, 開關(guān)S1 閉合, S2 將主運放兩輸入接至共模電平, 此時通過反饋環(huán)路, 輔助運放輸入端上的電容存儲的失調(diào)電壓設(shè)為Vc, 則:

![]()

可得:

當S1 斷開, S2 接入輸入信號時, 比較器正常工作, 由于Vc 的作用, 可以得到此時在比較器輸入端的等效失調(diào)電壓為:

根據(jù)ADC 的精度和電容陣列的校準算法, 并通過調(diào)節(jié)輔助運放和調(diào)零運放的增益使多級比較器的精度達到設(shè)計要求, 本次設(shè)計比較器的精度需高于19 位。圖6 為加入輔助輸入端的低增益跨導放大器的電路設(shè)計, 本次設(shè)計各級前放的增益約為22dB.

調(diào)零放大器采用全差分折疊式共源共柵結(jié)構(gòu), 一方面可實現(xiàn)高增益, 另一方面用于構(gòu)成單位負反饋, 從而可用電容檢測并消除自身的失調(diào)。本次設(shè)計, 該運放增益需要達到70dB 以上, 同時為保證輸出共模電平的穩(wěn)定需加入共模反饋。

圖6 前置跨導放大器的電路實現(xiàn)

5 仿真結(jié)果

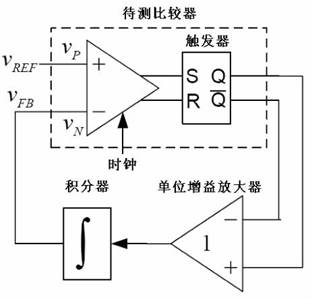

比較器的測試可采用動態(tài)失調(diào)測試平臺( DOTB) 進行,如圖7 所示。此方法運用單位增益放大器、積分器的性質(zhì), 將比較器接入環(huán)路, 通過對測試精度的調(diào)整, 最終得到比較器的等效輸入失調(diào)。

圖7 動態(tài)失調(diào)測試平臺框圖

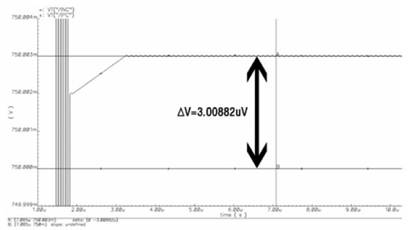

測試結(jié)果( 圖8) 表明: 加入消失調(diào)機制后, 多級比較器等效輸入失調(diào)約為3μV( <4μV) , 從而使比較器的精度達到了20 位。

圖8 單級比較器動態(tài)失調(diào)測試結(jié)果。

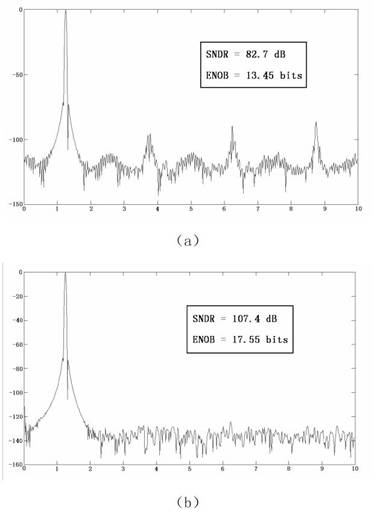

通過對ADC 進行頻譜分析, 測量其動態(tài)性能,即可反映ADC 的精度與線性度,并驗證數(shù)字校準的效果。為避免頻譜泄漏[7], 加入的正弦激勵信號的頻率和采樣頻率應(yīng)滿足如下關(guān)系:

Fin、Fs 分別表示輸入信號頻率和采樣頻率, Npoint為采樣點數(shù), n 為正整數(shù), 且n

圖9 ADC正弦激勵下的頻譜分析( a) 未校準( b) 校準后。

6 結(jié)論

本設(shè)計通過由低到高依次校準電容陣列的方法, 改善了電容DAC 的線性度; 利用輔助輸入端消失調(diào)技術(shù), 將比較器的精度提高到設(shè)計所需的指標。

實現(xiàn)了18bit 的精度要求。采用了多級比較器各級一次性消失調(diào)的結(jié)構(gòu), 提高了ADC 的轉(zhuǎn)換速度; 同時, 電容陣列DAC 的設(shè)計和運用使得較低的功耗成為本次SARADC 設(shè)計的另一優(yōu)點。