簡(jiǎn)介

HPI接口是TI為處理器之間直接互連通訊定義的一種異步接口,大多數(shù)TI DSP芯片上都有HPI接口。HPI接口是從(Slave)端口,接在主機(jī)的擴(kuò)展內(nèi)存總線上,DSP不能通過(guò)HPI向主機(jī)(Host)的訪問(wèn),只能被主機(jī)讀寫。兩個(gè)DSP的HPI接口之間不能通訊。兩個(gè)DSP之間互連,可以將一個(gè)DSP(從)的HPI接到另一個(gè)DSP(主)的擴(kuò)展內(nèi)存接口(EMIF)上[1]。

1. HPI工作模式

不同系列DSP上的HPI接口版本有所不同,區(qū)別體現(xiàn)在DSP對(duì)HPI的控制上,如C6727上的UHPI可通過(guò)寄存器使能與關(guān)閉HPI接口,對(duì)主機(jī)訪問(wèn)DSP內(nèi)存空間的控制,以及對(duì)HPI接口信號(hào)的功能復(fù)用上。但從主機(jī)訪問(wèn)的角度,HPI的工作模式分為:復(fù)用模式(Multiplexed-Mode)和非復(fù)用模式(Non-multiplexed-Mode)。

復(fù)用模式下沒(méi)有地址線,主機(jī)訪問(wèn)DSP的地址信息是以數(shù)據(jù)方式送到HPIA(HPI地址寄存)。從硬件信號(hào)的角度,地址,數(shù)據(jù)信號(hào)是由同一組數(shù)據(jù)線傳遞,所以稱為復(fù)用模式。

非復(fù)用模式的數(shù)據(jù)線與地址線是分開(kāi)的,與內(nèi)存接口連接相似。非復(fù)用模式不需要操作HPIA寄存器,主機(jī)訪問(wèn)的地址信息通過(guò)地址總線直接送給HPI。

所有的HPI接口都支持復(fù)用模式,但不是所有芯片的HPI接口都支持非復(fù)用模式(參考相應(yīng)的芯片手冊(cè)確定是否支持)。除了有無(wú)HPIA的操作區(qū)別外,兩種模式的操作沒(méi)有區(qū)別。因?yàn)榉菑?fù)用模式的操作是復(fù)用模式操作的子集,為方便起見(jiàn),本文以復(fù)用模式展開(kāi)討論。

2. HPI硬件信號(hào)連接

HPI接口復(fù)用模式連線如圖1所示,根據(jù)在應(yīng)用當(dāng)中的必要性分為:必要的,和可選的兩組信號(hào)。可選的信號(hào)以虛線表示。

圖1. HPI接口復(fù)用模式硬件連接

數(shù)據(jù)線HD[0:n]:在復(fù)用模式下,數(shù)據(jù)線的寬度一般為CPU位寬的一半,一個(gè)HPI訪問(wèn)分為高低半字的兩次訪問(wèn),如C5000是16-bit CPU,HPI數(shù)據(jù)線為8位,C6000是32-bit CPU,其HPI數(shù)據(jù)線為16位。C64x系列的HPI支持32位,在32位模式下一個(gè)HPI訪問(wèn)不需要分為高低半字兩次訪問(wèn)組成一個(gè)完整的訪問(wèn)。

HCNTL0/1,HWIL:HCNTL0/1選擇要訪問(wèn)的HPI寄存器,HWIL控制訪問(wèn)寄存器的高低半字,必須先高后低。一個(gè)寄存器的高低半字的兩次訪問(wèn)一定要連續(xù)完成,中間不能插入其它的HPI操作。只有HPIC可以只訪問(wèn)半個(gè)字。

HR/W:指示對(duì)HPI寄存器進(jìn)行讀,還是寫操作。如果主機(jī)的讀,寫信號(hào)是分開(kāi)的,可以利用其中一個(gè)信號(hào),但要注意做上拉或下拉處理以控制其在三態(tài)時(shí)的電平。

HCS,HDS1/2:這三個(gè)信號(hào)根據(jù)圖2的邏輯產(chǎn)生內(nèi)部HSTROBE信號(hào),其邏輯關(guān)系是要求HDS1和HDS2信號(hào)相反,HCS低有效。HSTROB下降沿的時(shí)間點(diǎn)反應(yīng)的是三個(gè)信號(hào)中最后跳變的信號(hào)。HPI在HSTROB的下降沿采樣控制信號(hào)HR/W,HCNTL0/1,HWIL以判斷主機(jī)要對(duì)哪個(gè)寄存器進(jìn)行讀,或者寫操作命令。注意控制信號(hào)在HSTROBE的下降沿之前需要最少5ns的setup穩(wěn)定時(shí)間,而HDS1/2和HCS到HSTROBE信號(hào)內(nèi)部門電路的延時(shí)是皮秒級(jí)的,所以控制信號(hào)的setup時(shí)間需要外部時(shí)序保證。

圖2. HSTROBE信號(hào)產(chǎn)生邏輯

HRDY:HPI的輸出信號(hào),指示當(dāng)前操作狀態(tài),用做硬件流量控制握手信號(hào)。

HINT:通過(guò)HPI,主機(jī)與DSP之間可以互發(fā)中斷。HINT是HPI送給主機(jī)的中斷信號(hào),DSP對(duì)HPIC[HINT]位寫1,HINT信號(hào)線上送出高電平信號(hào),主機(jī)可利用此信號(hào)做為中斷信號(hào)輸入。DSP不能清除HPIC[HINT]狀態(tài),主機(jī)在響應(yīng)中斷后,需要對(duì)HPIC[HINT]位寫1清除狀態(tài),DSP才能再次對(duì)HPIC[HINT]置位發(fā)中斷。主機(jī)通過(guò)寫HPIC[DSPINT]置1給DSP產(chǎn)生中斷,DSP在響應(yīng)中斷后,需要對(duì)HPIC[DSPINT]寫1清除狀態(tài),主機(jī)才能繼續(xù)操作HPIC[DSPINT]給DSP發(fā)中斷。通過(guò)HPI傳輸數(shù)據(jù),結(jié)合互發(fā)中斷做為軟件層的握手信號(hào),可有效提高通訊的效率與靈活性。

ALE:存在于地址,數(shù)據(jù)線復(fù)用的主機(jī)上用來(lái)指示地址信號(hào)周期,這種總線復(fù)用的主機(jī)很少見(jiàn),所以通常將ALE固定上拉處理,只用HSTROBE采樣控制信號(hào)。

BE:Byte Enable信號(hào),這個(gè)信號(hào)只出現(xiàn)在32位的C6000 DSP上。因?yàn)閼?yīng)用當(dāng)中通常都是對(duì)整個(gè)32-bit字進(jìn)行訪問(wèn),所以直接做上拉使能處理。

3.HPI寄存器地址映射

HPI口提供給主機(jī)端訪問(wèn)的寄存器只有4個(gè),通過(guò)HCNTL[1:0]選擇.

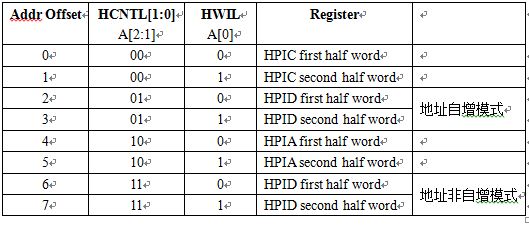

表1. HPI寄存器訪問(wèn)選擇

由于在復(fù)用模式下數(shù)據(jù)線通常只有寄存器寬度的一半,所以一個(gè)完整的數(shù)據(jù)訪問(wèn)由高低半字兩次訪問(wèn)組成,由HWIL信號(hào)控制,HWIL信號(hào)必須是先低后高。通常將HWIL和HCNTL[1:0]接在主機(jī)的地址線上,將4個(gè)寄存器映射為主機(jī)端的8個(gè)內(nèi)存單元,下表中的地址線連接方法將8半字寄存器映射到主機(jī)的8個(gè)連續(xù)的內(nèi)存單元。這里的地址線是用來(lái)選擇HPI的寄存器,與非復(fù)用模式下的地址線直接訪問(wèn)DSP的內(nèi)存空間是完全不同的作用。

表2. HPI寄存器地址映射

4. HPI寄存器功能說(shuō)明

HPIC (HPI Control Register)

HPI控制寄存器HPIC的位圖如表3所示,C6000系列DSP的HPI寄存器是32位的,也只有低16位有效,與C5000系列DSP的HPIC寄存器定義的功能保持一致。不同版本的HPI接口的HPIC位定義的主要不同之處在于軟件握手HRDY位的有無(wú),其它位名稱可能存在細(xì)小差異,但功能定義都是一樣的。

表3. HPI Control Register

主機(jī)在對(duì)HPI進(jìn)行訪問(wèn)前可以通過(guò)HPIC配置字節(jié)序(HWOB)和地址寄存器模式(DUALHPIA)。默認(rèn)的配置為HWOB=0,即先訪問(wèn)高半;DUALHPIA=0,即單地址寄存器模式,讀和寫操作使用同一個(gè)HPIA;通常都采用默認(rèn)的HPIC寄存器配置。

HWOB與硬件信號(hào)HWIL是沒(méi)有聯(lián)系的,HWIL信號(hào)必須保證先低后高分別訪問(wèn)兩個(gè)半字單元。至于先訪問(wèn)一個(gè)字當(dāng)中的高或低半字,是由HWOB控制的。

HPIA (HPI Address Register)

物理上存在HPIAR,HPIAW兩個(gè)地址寄存器。HPIAR是讀操作地址寄存器;HPIAW是寫操作地址寄存器。由HPIC的DUALHPIA位來(lái)決定是采用雙地址寄存器模式還是單地址寄存器模式。如果采用雙地址寄存器模式,在對(duì)HPIA操作之前,通過(guò)設(shè)置HPIC的HPISEL位選擇下一個(gè)要訪問(wèn)的HPIA。通常為了簡(jiǎn)化在讀寫操作轉(zhuǎn)換時(shí)對(duì)HPIC的操作,選用單地址寄存器模式。

HPIA的地址信息在不同系列DSP上有所不同:

在C5000上,數(shù)據(jù)空間,I/O空間只能按16位字尋址,程序空間按字節(jié)尋址。HPI的DMA訪問(wèn)屬于I/O空間,HPIA的值代表16位字地址。如主機(jī)端要訪問(wèn)DSP內(nèi)存字節(jié)地址0x100, 則要往HPIA寫的地址值是0x80。在用HPI啟動(dòng)時(shí),要注意DSP代碼是按字節(jié)地址鏈接的,即代碼段的地址是字節(jié)地址,主機(jī)端要將代碼段的地址信息除以2再送到HPIA。

在C64上,HPIA的值代表字節(jié)地址,但是HPI訪問(wèn)的數(shù)據(jù)是32位的,所以HPI會(huì)忽略HPIA地址值的低兩位。

在C64+的DSP上,HPIA代表32位字地址,HPI會(huì)將字地址左移兩位轉(zhuǎn)換成字節(jié)地址,主機(jī)若要訪問(wèn)DSP字節(jié)地址0x100,則要賦值HPIA為0x40。

HPID (HPI Data Register)

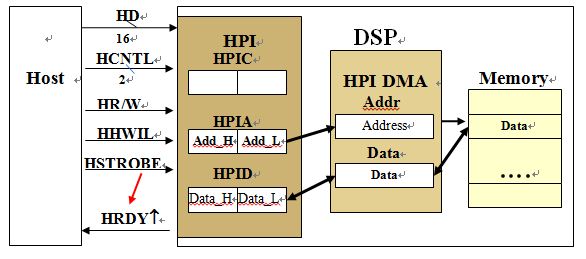

主機(jī)通過(guò)HPI對(duì)DSP的內(nèi)存訪問(wèn)是間接訪問(wèn),主機(jī)只能訪問(wèn)HPID,HPID與DSP內(nèi)存之間是通過(guò)HPI專屬的DMA進(jìn)行數(shù)據(jù)搬運(yùn)的。如圖3所示。

圖3. HPI讀寫數(shù)據(jù)流

HPID的訪問(wèn)分為自增模式和非自增模式。在自增模式下,訪問(wèn)HPID后,HPIA會(huì)自動(dòng)增加指向下一個(gè)字地址,在連續(xù)訪問(wèn)時(shí),自增模式因?yàn)闇p少了主機(jī)對(duì)HPIA的操作,可以增加HPI數(shù)據(jù)訪問(wèn)的吞吐率。非自增模式下訪問(wèn)HPID后,HPIA的值保持不變,主機(jī)需要更新HPIA來(lái)訪問(wèn)下一個(gè)地址。

在寫操作時(shí),主機(jī)把數(shù)據(jù)寫到HPID,HPI將第二個(gè)半字的數(shù)據(jù)通過(guò)HSTROBE的上升沿鎖存到HPID后,將HRDY置為忙狀態(tài),并啟動(dòng)HPI DMA將HPID的內(nèi)容搬到HPIA所指向的內(nèi)存單元,然后清除HRDY指示可以進(jìn)行下一次操作。

在讀操作時(shí),在第一個(gè)HSTROBE的下降沿,HPI采樣到HR/W為讀命令,則將HRDY置為忙狀態(tài),啟動(dòng)HPI DMA將HPIA指向的內(nèi)存單元的數(shù)據(jù)搬到HPID,清除HRDY忙狀態(tài),主機(jī)端方可結(jié)束總線訪問(wèn)周期,鎖存數(shù)據(jù)線上的有效數(shù)據(jù)。

5. HPI操作流程

主機(jī)對(duì)HPI的一次總線訪問(wèn)周期為分三個(gè)階段:主機(jī)發(fā)起訪問(wèn),HPI響應(yīng),主機(jī)結(jié)束訪問(wèn)周期。

A. 主機(jī)發(fā)起訪問(wèn):即對(duì)HPI寄存器的讀,或者寫命令。主機(jī)送出的硬件信號(hào)為HSTROBE(由HCS, HDS1/2產(chǎn)生),HR/W,HCNTL0/1,HWIL,以及HD[0:n]。HPI在HSTROBE的下降沿采樣控制信號(hào)HR/W,HCNTL0/1,HWIL判斷主機(jī)的操作命令。

B. HPI響應(yīng):HPI在HSTROBE的下降沿采樣控制信號(hào),根據(jù)控制信號(hào)做出相應(yīng)的響應(yīng)。如果是寫(HR/W為低)命令,則在HSTROBE的上升沿將數(shù)據(jù)線上的信號(hào)鎖存到HCNTL0/1和HWIL指向的寄存器。如果是讀命令(HR/W為高),如果是讀HPIC,或者HPIA寄存器,HPI將寄存器的值直接送到數(shù)據(jù)總線上;如果讀HPID,HPI先將HRDY置為忙狀態(tài),HPI DMA將數(shù)據(jù)從HPIA指向的內(nèi)存單元讀到HPID,再送到數(shù)據(jù)線上,并清除HRDY忙狀態(tài),在讀HPID后半字時(shí),數(shù)據(jù)從寄存器直接送到數(shù)據(jù)總線上,不會(huì)出現(xiàn)HRDY信號(hào)忙狀態(tài)。

C. 主機(jī)結(jié)束訪問(wèn)周期:對(duì)于寫操作,主機(jī)將數(shù)據(jù)送出后,只要滿足芯片手冊(cè)中HPI對(duì)HCS的最小寬度要求,即可結(jié)束訪問(wèn)周期。對(duì)于讀HPID操作,要等HRDY信號(hào)由忙變?yōu)椴幻Γ鳈C(jī)才能結(jié)束訪問(wèn)周期。

a) 兩次連續(xù)的HPI操作的間隔,在芯片手冊(cè)的HPI時(shí)序參數(shù)表里有要求,最小間隔為兩個(gè)HPI功能模塊時(shí)鐘周期。

6. HPI常見(jiàn)故障案例分析

在HPI應(yīng)用調(diào)試過(guò)程中,常遇到的問(wèn)題分為:寫數(shù)據(jù)不成功,讀數(shù)據(jù)不正確,HRDY常高。這些問(wèn)題通常都是由于時(shí)序不正確造成的,下面結(jié)合實(shí)際應(yīng)用當(dāng)中的案例進(jìn)行分析。

6.1 寫數(shù)據(jù)不成功

案例的硬件連接如下:

硬件連接

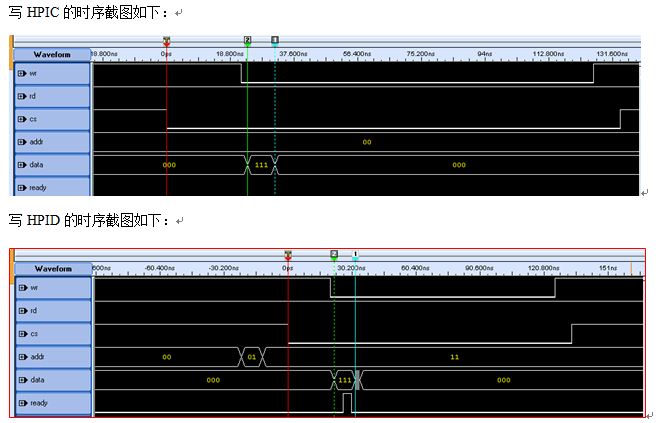

首先關(guān)注核心信號(hào)HSTROBE由DSP_CS,ARM_WR(HDS1),ARM_RD(HDS2)產(chǎn)生,從下面時(shí)序圖可以看出ARM_WR的下降沿是最后產(chǎn)生的,所以寫操作時(shí)HSTROBE的下降沿反應(yīng)的是ARM_WR的下降沿。

寫HPIC的時(shí)序截圖如下:

寫HPIC\HPID的時(shí)序截圖

兩個(gè)時(shí)序圖顯示主機(jī)送出的數(shù)據(jù)111b在HSTROBE(ARM_WR)的下降沿后,很快被改變成其它值000b。在寫HPID的時(shí)序截圖中,第一個(gè)HSTROBE的下降后,HPI送出HRDY信號(hào),然后數(shù)據(jù)線被改變,首先判斷HPI對(duì)主機(jī)的命令做出了響應(yīng),通過(guò)HRDY信號(hào)的出現(xiàn)時(shí)機(jī),說(shuō)明HPI判斷這是一個(gè)讀操作,可以判斷為HSTROBE的下降沿采樣HR/W信號(hào)不正確。

從硬件連接來(lái)看,HSTROBE(HR/W)要采樣HR/W,HCNTL0/1來(lái)判斷主機(jī)命令, HR/W的與HSTROBE為同一信號(hào)源,且同為下降沿,HR/W與HSTROBE的下降沿之間的setup時(shí)間不夠,采樣HR/W的電平狀態(tài)出現(xiàn)誤判,認(rèn)為是高電平讀命令,HPI對(duì)讀命令的響應(yīng)則是在第一個(gè)HSTROBE的下降沿之后送出HRDY信號(hào),并在HRDY之后,HPI送出數(shù)據(jù)到總線上。

對(duì)于該問(wèn)題,需要對(duì)參與HSTROBE邏輯譯碼的HR/W信號(hào)的下降沿做延時(shí)處理,可在邏輯電路如CPLD或FPGA里實(shí)現(xiàn),以確保HSTROBE的下降沿采樣到穩(wěn)定的HR/W電平。

6.2 讀數(shù)據(jù)不正確

通常表現(xiàn)為讀讀HPIC,HPIA正常,但讀HPID不正常,前半字為0,后半字正確,對(duì)同一個(gè)地址讀兩次,第二次的數(shù)據(jù)完全正確。

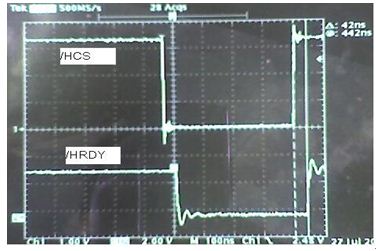

在案例中,用示波器觀察HCS與HRDY之間的時(shí)序關(guān)系,發(fā)現(xiàn)HCS的上升沿在HRDY的上升沿之前,即主機(jī)在HPI數(shù)據(jù)有效之前結(jié)束了訪問(wèn)周期。HRDY的上升沿其實(shí)是因?yàn)镠CS的結(jié)束而拉高的,并非數(shù)據(jù)真正有效。

示波器觀察HCS與HRDY之間的時(shí)序關(guān)系

用戶由于沒(méi)有在硬件上將HRDY與主機(jī)PowerPC的TA信號(hào)互連,沒(méi)有硬件握手機(jī)制,于是從軟件配置上加大主機(jī)的總線訪問(wèn)周期,即增加HCS的寬度,故障現(xiàn)象沒(méi)有變化。

原因分析:讀HPID與HPIC,HPIA時(shí)序不同,讀HPID操作需要HPI DMA從HPIA所指向的地址讀數(shù)據(jù)到HPID,會(huì)有時(shí)間上的延時(shí)。而讀HPIC和HPIA直接從寄存器讀數(shù)據(jù),沒(méi)有延時(shí),所以讀HPIC,HPIA是正確的。在讀HPID時(shí),HPI會(huì)在第一個(gè)HSTROBE的下降沿后將HRDY置位,指示數(shù)據(jù)未準(zhǔn)備好的忙狀態(tài),主機(jī)應(yīng)當(dāng)在總線上插入等待周期,數(shù)據(jù)準(zhǔn)備好后HPI清除HRDY,主機(jī)才可以結(jié)束總線周期,通過(guò)HCS的上升沿將有效數(shù)據(jù)鎖存。

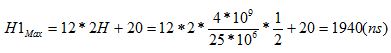

HSTROBE的下降沿到數(shù)據(jù)有效之間的延時(shí)與芯片及HPI接口的工作頻率相關(guān),以C5502,C5501為例,在芯片手冊(cè)中,這個(gè)延時(shí)參數(shù)H1在SYSCLK1與CPU時(shí)鐘的分頻為4時(shí),最大延時(shí)為12*2H+20(ns),H=SYSCLK1/2,在HPI啟動(dòng)期間,PLL沒(méi)有倍頻,處于旁通狀態(tài),系統(tǒng)輸入時(shí)鐘就是CPU的工作時(shí)鐘,SYSCLK1默認(rèn)分頻為CPU時(shí)鐘的4分頻,以輸入時(shí)鐘為25MHz為例,最大延時(shí)為:

延時(shí)計(jì)算

這個(gè)時(shí)間長(zhǎng)度通常超出了主機(jī)端總線周期的軟件配置范圍,所以通過(guò)軟件配置增加HCS的寬度不一定能滿足HRDY的最大延時(shí)要求。在有的DSP芯片手冊(cè)上只提供了HRDY的最小延時(shí),最大延時(shí)與芯片的優(yōu)先級(jí)設(shè)置,及系統(tǒng)配置相關(guān)而不確定,比如與系統(tǒng)中其它主模塊如EDMA同時(shí)訪問(wèn)DDR,那么延時(shí)與HPI的優(yōu)先級(jí),EDMA的優(yōu)先級(jí),EDMA的burst長(zhǎng)度,以及DDR的命令排序等配置相關(guān),這樣通過(guò)延長(zhǎng)主機(jī)的總線訪問(wèn)周期,更加不可靠。

解決辦法:在硬件設(shè)計(jì)之初,一定要利用HRDY硬件握手信號(hào)[2][3]。雖然有的芯片HPIC寄存器提供了HRDY軟件握手方式,只能做為彌補(bǔ)硬件設(shè)計(jì)之初遺漏HRDY硬件握手信號(hào)的權(quán)宜之計(jì),軟件輪循HRDY的辦法會(huì)帶來(lái)額外的開(kāi)銷,降低HPI總線的吞吐率,增加主機(jī)軟件實(shí)現(xiàn)的復(fù)雜度。而且有的芯片HPI不支持HRDY軟件查詢方法,只能通過(guò)硬件HRDY保證數(shù)據(jù)的有效性。

6.3 HRDY常高

有的系統(tǒng)在長(zhǎng)時(shí)間運(yùn)行中偶爾出現(xiàn)HRDY常高,導(dǎo)致主機(jī)端總線訪問(wèn)異常,需要重新上電才能恢復(fù)HPI的正常操作。這種故障是由于HPI狀態(tài)機(jī)出現(xiàn)異常。

從實(shí)際故障定位中總結(jié)出以下幾點(diǎn)原因:

A. HPI的高低半字訪問(wèn)的順序訪問(wèn)被其它HPI訪問(wèn)打斷:在復(fù)用模式下,一個(gè)完整的HPI訪問(wèn)是由高低半字兩次訪問(wèn)組成,需要嚴(yán)格保證,否則會(huì)破壞HPI的狀態(tài)機(jī),從而導(dǎo)致不可預(yù)期的后果。

B. 主機(jī)通過(guò)HPI訪問(wèn)了DSP內(nèi)部的保留空間,或者破壞了DSP的程序,數(shù)據(jù)空間,導(dǎo)致DSP運(yùn)行異常,進(jìn)而導(dǎo)致HPI狀態(tài)機(jī)異常。

C. 主機(jī)的HSTROBE信號(hào)有毛刺,或者信號(hào)完整性不好,如下圖中HCS(些案例HSTROBE是由HCS控制)的上升沿的回勾,都會(huì)導(dǎo)致HPI誤判斷為主機(jī)的新的訪問(wèn)的開(kāi)始,從而打亂了高低半字的訪問(wèn)順序要求,導(dǎo)致HPI狀態(tài)機(jī)的錯(cuò)亂。

HSTROBE信號(hào)

7. 總結(jié)

HPI是一種簡(jiǎn)單的異步接口,只要設(shè)計(jì)中滿足了時(shí)序要求,即可穩(wěn)定工作。在開(kāi)發(fā)當(dāng)中遇到數(shù)據(jù)讀寫不正確,從HSTROBE信號(hào)入手檢查與之相關(guān)的信號(hào)的時(shí)序關(guān)系,便可以找出問(wèn)題原因。另外,信號(hào)完整性是任何系統(tǒng)穩(wěn)定工作的前提。

關(guān)于特定芯片上HPI接口的特有功能本文沒(méi)有針對(duì)討論,如C6727的字地址模式和字節(jié)地址模式可通過(guò)HPIC配置;C6727在HPI啟動(dòng)后ROM bootloader將HPI關(guān)閉,需要軟件重新使能才能使用等;以及不同芯片的HPI啟動(dòng)模式下的跳轉(zhuǎn)方式不同,請(qǐng)參考相應(yīng)芯片的HPI手冊(cè)及bootloader應(yīng)用手冊(cè)。