近年來,隨著通信和多媒體市場的快速增長,數(shù)字系統(tǒng)無論在處理能力還是處理速度上都取得了飛速的發(fā)展,因此對作為模擬信號通向數(shù)字信號橋梁的模數(shù)轉(zhuǎn)換器(ADC)的性能要求也越來越高 [1]。在各種ADC結構中,流水線ADC在速度和精度上能夠達到合理的折衷,因此得到了廣泛應用。在流水線結構ADC中,其前端采樣保持電路是整個系統(tǒng)的關鍵模塊之一,其性能直接決定了整個ADC的性能[2]。

本文對流水線ADC的采樣保持電路的結構以及主要模塊如增益提高型運算放大器電路、共模反饋電路和開關電路進行了分析,并對各個模塊進行了設計,最終設計出一個適合于13 bit 40 MHz流水線ADC的采樣保持電路,仿真結果表明,該采樣保持電路滿足設計要求。

1 采樣保持電路結構

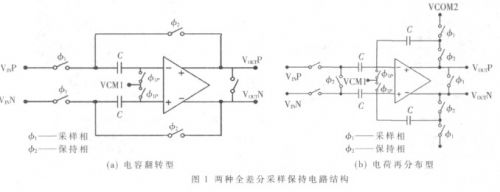

采樣保持電路的結構直接決定了采樣保持電路的精度和速度,圖1為常用的兩種全差分結構:電荷再分布型和電容翻轉(zhuǎn)型。全差分結構能夠很好地消除直流偏置和偶次諧波失真,并抑制來自襯底的共模噪聲。

與電荷再分布型結構相比較,電容翻轉(zhuǎn)型結構的反饋系數(shù)為1,是電荷轉(zhuǎn)移型(在Cs=Cf=C時,反饋系數(shù)為0.5)的兩倍,因此在同樣的閉環(huán)帶寬時,電容翻轉(zhuǎn)式結構所要求的運放單位增益帶寬(GBW)只是電容電荷再分布式GBW的一半,所以電容翻轉(zhuǎn)型結構具有功耗小的優(yōu)點[3]。另外由于電荷再分布型電路需要使用4個電容,但電容翻轉(zhuǎn)型只需要2個電容,在CMOS工藝中,電容需要大的實現(xiàn)面積,電容翻轉(zhuǎn)型結構具有小的實現(xiàn)面積。因此,電容翻轉(zhuǎn)型更適合高速高精度的流水線ADC應用,本文的采樣保持電路采用電容翻轉(zhuǎn)式結構來實現(xiàn)。

2 增益提高型放大器的設計

運算放大器是整個采樣保持電路中最重要的模塊,它的增益和帶寬直接決定了采樣保持電路的精度和速度。但增益和帶寬是相互矛盾的,高增益要求使用多級放大器、小的偏置電流、長溝道器件;而大帶寬則要求使用單級放大器、大的偏置電流、短溝道器件,所以放大器是采樣保持電路設計的一個難點。

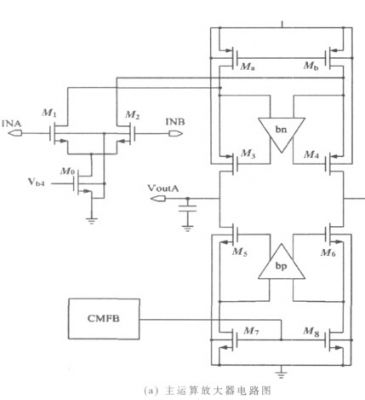

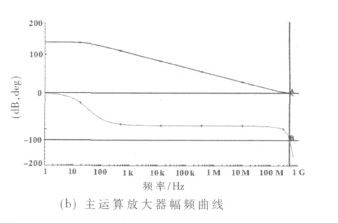

本文主運算放大器采用全差分的折疊式共源共柵結構,并用增益提高技術來提高放大器的增益,達到了高增益和大帶寬的要求[4-5]。主運算放大器電路如圖2 所示,由于NMOS管的遷移率高于PMOS管,在跨導相同的情況下,NMOS管具有較小的面積,從而使得運算放大器具有較小的輸入電容,有利于提高采樣保持電路的反饋系數(shù),所以本文采用了NMOS管作為輸入對管的折疊式共源共柵結構。兩個輔助運算放大器BN和BP分別為NMOS和PMOS管作為輸入對管的折疊式共源共柵放大器。圖2 中的CMFB模塊為主運算放大器的共模反饋電路,由于主運放的輸出擺幅較大,所以采用如圖3(a)所示的開關電容共模反饋電路,開關電容共模反饋不會受輸出擺幅產(chǎn)生限制,并且其只有靜態(tài)功耗。對于兩個輔助運放而言,由于其輸出和輸入范圍很小,所以采用如圖3(b)所示的連續(xù)時間共模反饋電路,這種電路沒有電容,節(jié)省了面積。圖2(b)為主運算放大器在負載電容為6 pF時的頻率特性曲線,其增益為133 dB,帶寬約為478 MHz,相位余度為59.7度。整個放大器(包括偏置電路、輔助運放、共模反饋電路)消耗的平均電流為8.5 mA。

3 采樣開關的設計

采樣開關的性能在采樣保持電路中占有十分重要的地位,對于一個簡單的NMOS開關,開關導通時其導通電阻Ron為:

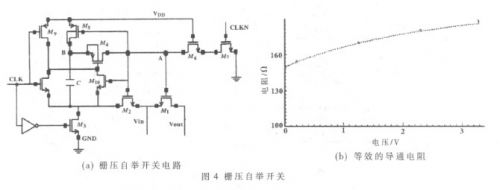

可見,導通Ron是一個與輸入信號Vin相關的非線性電阻,這將在輸出信號中引入諧波失真 [5]。本文采用如圖4(a)所示的柵壓自舉開關,開關的導通電阻隨輸入信號幅值變化的曲線圖如圖4(b)所示,曲線的斜率大約為11 Ω/V,其導通電阻隨輸入信號幅值的變化較小,具有較高的線性度。

4 仿真結果

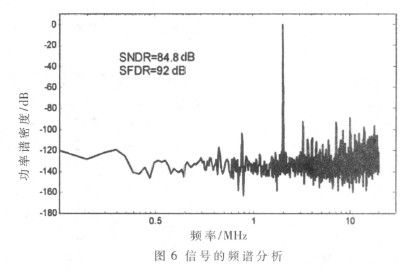

采用TSMC的0.18 μm工藝對電路進行了設計,電源電壓為3.3 V,采樣時鐘為40 MHz,采用Spectre對電路進行了仿真。在采樣保持電路的輸入端加一值為1 V的階躍信號,其瞬態(tài)仿真結果如圖5所示。從圖中分析得出,在保持相結束時刻,采樣保持電路的輸出幅值為1.000 08 V,與理想電壓的誤差為0.08 mV,建立精度達到了0.008%。圖6所示為信號的頻譜分析,輸入峰-峰值為2 V,頻率為1.992 187 5 MHz的正弦信號。對輸出信號進行4 096點的FFT, 結果顯示, 其SNDR為84.8 dB,SFDR為92 dB,有效位數(shù)為13.8 bit,能夠勝任13 bit 40 MHz流水線型ADC對前端采樣保持結構的要求。整個采樣保持電路消耗的平均電流為8.501 mA。

本文設計了一個高速高精度的采樣保持電路,可作為13 bit 40 MHz流水線型ADC的前端模塊。該采樣保持電路為電容翻轉(zhuǎn)結構,采用柵壓自舉開關提高了開關的線性度,其運算為增益提高型的折疊式共源共柵結構,達到了高速高增益的要求。仿真結果表明,整個采樣保持電路的精度和速度滿足了設計要求。