美國空間數(shù)據(jù)系統(tǒng)咨詢委員會(簡稱CCSDS)于2005年推出一套適用于空間領(lǐng)域的圖像壓縮標(biāo)準(zhǔn),標(biāo)準(zhǔn)使用了離散小波變換為核心算法,推薦使用9/7整數(shù)離散小波變換實(shí)現(xiàn)無損圖像壓縮,由于該算法結(jié)構(gòu)簡單,易于硬件設(shè)計實(shí)現(xiàn),因此可以用FPGA來實(shí)現(xiàn)提升小波算法。

1、CCSDS圖像壓縮標(biāo)準(zhǔn)中的小波變換

CCSDS圖像壓縮算法主要包括兩個功能模塊:前一部分是對遙感圖像數(shù)據(jù)進(jìn)行離散小波變換,去除圖像數(shù)據(jù)之間的冗余;后一部分是對去相關(guān)后的圖像數(shù)據(jù)進(jìn)行位平面壓縮編碼,如圖1所示。

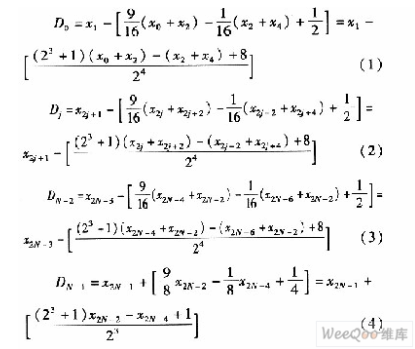

CCSDS標(biāo)準(zhǔn)推薦使用9/7離散小波濾波器對圖像數(shù)據(jù)進(jìn)行變換,即濾波器的低通系數(shù)為9個,濾波器的高通系數(shù)為7個。對于長度為2N待變換圖像的原始數(shù)據(jù)Xk(k=0,1,2,…,2N-1),其整形小波變換公式如式(1)~式(6)所示。

其中,[]為對數(shù)據(jù)進(jìn)行下取整操作;Cj為低通小波系數(shù)輸出;Dj為高通小波系數(shù)輸出。為了避免乘法器運(yùn)算的繁瑣,對公式進(jìn)行了變形,采用加法器和移位操作實(shí)現(xiàn)公式的運(yùn)算,提高了運(yùn)算速度。

2、9/7二維離散小波變換的系統(tǒng)設(shè)計過程

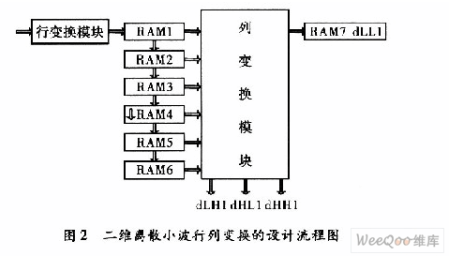

本文在Xilinx公司提供的ISE7.1集成設(shè)計軟件環(huán)境下,采用VHDL語言設(shè)計實(shí)現(xiàn)9/7二維離散小波變換系統(tǒng),首先進(jìn)行小波行變換,行變換后的數(shù)據(jù)按照行數(shù)輸入內(nèi)部RAM緩存,然后對行變換后的數(shù)據(jù)再進(jìn)行列變換,最后將低頻系數(shù)dLLl輸入RAM緩存,其余高頻系數(shù) dLHl,dHLl,dHHl輸出到外掛RAM中緩存,系統(tǒng)設(shè)計流程,如圖2所示。

2.1、行變換過程

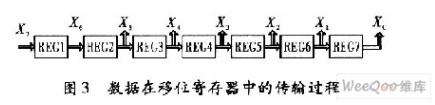

首先,使用7個移位寄存器來實(shí)現(xiàn)對數(shù)據(jù)的讀寫傳輸,每到來一個時鐘控制信號(clk),就往移位寄存器中讀寫一個數(shù)據(jù),數(shù)據(jù)在移位寄存器中的傳輸過程,如圖3所示。

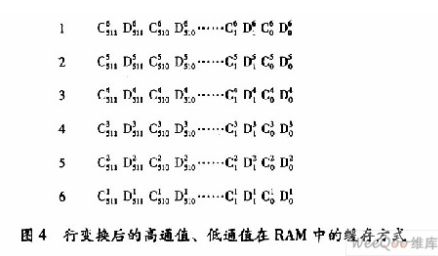

當(dāng)輸入第5個數(shù)據(jù)時,就可以根據(jù)式(1)和式(5)分別計算出第一個高通系數(shù)值D0和第一個低通系數(shù)值C0,下一個時鐘控制信號讀入第6個數(shù)據(jù)時,不進(jìn)行操作,當(dāng)控制讀入第7個數(shù)據(jù)時,根據(jù)式(2)和式(6)分別計算出第2個高通系數(shù)值Dj和第2個低通系數(shù)值Cj,小波行變換后的高通系數(shù)D和低通系數(shù)C采用地址傳輸?shù)姆绞浇徊娲鎯Φ?個內(nèi)部RAM當(dāng)中,如圖4所示。

2.2、列變換過程

由于列變換是針對行變換后的數(shù)據(jù)進(jìn)行的,即對上面6片RAM中存儲的行變換后的數(shù)據(jù)進(jìn)行列變換,為了提高運(yùn)行速度,本文采用基于行的列變換方法,即當(dāng)小波變換進(jìn)行到第5行時,列變換也同時進(jìn)行,第5行行變換結(jié)束時,也完成了針對第5行數(shù)據(jù)的列變換,當(dāng)?shù)?行進(jìn)行小波變換時,不進(jìn)行列變換操作,直到第 7行小波行變化數(shù)據(jù)輸入時,再同時進(jìn)行列變換計算操作,依次完成小波列變換。對于列小波變換后的低頻數(shù)據(jù)dLLl,要輸入RAM緩存以進(jìn)行下一級變換,對于其他的高頻數(shù)據(jù)(dLHl,dHLl,dHHl)可以直接輸出到片外存儲器中。

下面是設(shè)計的一級二維小波變換的集成模塊,如圖5所示。

3、仿真與綜合

為了驗(yàn)證本文設(shè)計系統(tǒng)的性能,使用Modlesim6.3仿真軟件對系統(tǒng)進(jìn)行了仿真測試,下面是采用大小為1 024×1 024,圖像數(shù)據(jù)為8位的測試圖像進(jìn)行測試仿真的部分波形圖。

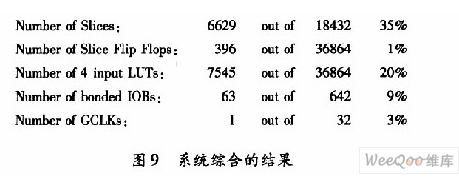

在Xilinx提供的ISE7.1仿真軟件下搭建測試平臺,對設(shè)計系統(tǒng)進(jìn)行綜合,結(jié)果如圖9所示。

設(shè)計系統(tǒng)時鐘頻率可達(dá)到54 MHz,滿足對圖像數(shù)據(jù)的實(shí)時處理要求。

4、結(jié)束語

本文主要討論了基于FPGA的快速9/7整形離散小波變換系統(tǒng)設(shè)計,該結(jié)構(gòu)采用內(nèi)部RAM的循環(huán)覆蓋的存儲方式,使對存儲器的需求量減小,從而減小了硬件功耗,同時采用基于行的列變換方式,提高了的系統(tǒng)運(yùn)行,可實(shí)現(xiàn)對遙感傳輸圖像的快速實(shí)時處理。