ADC的一個重要趨勢是轉(zhuǎn)向更高的分辨率。這一趨勢影響著一系列的應(yīng)用,包括工廠自動化、溫度檢測,以及數(shù)據(jù)采集。對更高分辨率的需求使設(shè)計者們從傳統(tǒng)的12位SAR(逐次逼近寄存器)ADC,轉(zhuǎn)向分辨率達24位的Δ-Σ ADC。所有ADC都有某種程度的噪聲,包括輸入相關(guān)噪聲以及量化噪聲,前者是ADC本身固有的噪聲,后者則是在ADC轉(zhuǎn)換時出現(xiàn)的噪聲。噪聲、ENOB(有效位數(shù))、有效分辨率、無噪聲分辨率等指標基本上定義了一款A(yù)DC的精度。

因此,了解有關(guān)噪聲的性能指標要比從SAR轉(zhuǎn)向Δ-Σ ADC更加困難。鑒于當前對更高分辨率的需求,設(shè)計者必須更好地了解ADC噪聲、ENOB、有效分辨率,以及信噪比。

更高分辨率

過去,一只12位SAR ADC通常就足以測量各種信號與電壓輸入。如果某個應(yīng)用需要更精細的測量,設(shè)計者可以在ADC前加一個增益級或PGA(可編程增益放大器)。對于16位設(shè)計,設(shè)計者的選擇仍然主要是SARADC,但也包含了某些Δ-Σ ADC。但對16位以上的設(shè)計,Δ-Σ ADC正在變得更加適用。SAR ADC現(xiàn)在有18位的極限,而Δ-Σ ADC正將自己的空間擴充到18位、20位和24位。ADC的價格在過去10年有不小的下降,使用也變得更簡單,獲得了更廣泛的理解。

有效分辨率

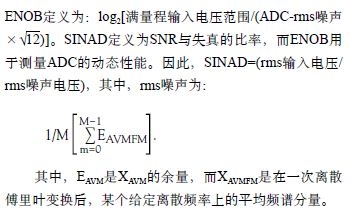

下式定義了有效分辨率的位數(shù): 有效分辨率=log2(滿量程輸入電壓范圍/ADC-rms噪聲),或更簡單地,有效分辨率=log2(VIN/VRMSNOISE)。不要將有效分辨率與ENOB相混淆。測量ENOB的最常用方法是對ADC的一個正弦波輸入做快速傅里葉變換分析。IEEE標準1057將

有效分辨率與無噪聲分辨率測量的是ADC在基礎(chǔ)dc的噪聲性能,它不是頻譜失真中的因素,包括總諧波失真和無寄生動態(tài)范圍。一旦知道了ADC的噪聲與輸入范圍,對有效分辨率和無噪聲分辨率的計算就變得簡單了。

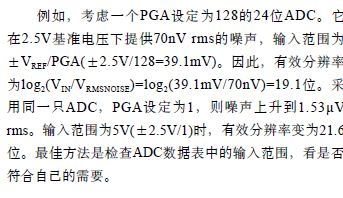

ADC的輸入電壓范圍取決于基準電壓。如果ADC包含有一個PGA,則還要把PGA考慮到電壓范圍內(nèi)。有些Δ-Σ ADC包括了用于提高小信號增益的PGA。帶PGA的最新ADC通常都標示噪聲小于100nV rms。雖然這個噪聲數(shù)字看似比老款A(yù)DC有吸引力,但它通常采用的是一個小輸入范圍,根據(jù)基準電壓,小的輸入范圍才能最終放大以適配一個較寬的ADC有效范圍。因此,這些ADC的有效分辨率與無噪聲分辨率可能弱于那些不帶PGA的ADC。

無噪聲分辨率

無噪聲分辨率采用的是峰峰電壓噪聲,而不是rms噪聲。下式定義了無噪聲分辨率的位數(shù):無噪聲分辨率=log2(滿量程輸入電壓范圍/ADC的峰峰噪聲)。無噪聲分辨率=log2(VIN/V-p-p噪聲)。可以用實驗室中的5位半或6位半數(shù)字萬用表來看待無噪聲或無閃爍分辨率。如果顯示的最后一位數(shù)穩(wěn)定且不閃爍,則數(shù)據(jù)輸出字就高于系統(tǒng)的噪聲水平。以6.6的波峰因數(shù)為例,峰峰噪聲是rms噪聲的6.6倍。因此,有效分辨率要比無噪聲分辨率高2.7位。采用相同的噪聲與基準值,無噪聲分辨率為18.9位。

無噪聲計數(shù)

無噪聲計數(shù)是精密系統(tǒng)用于評估ADC性能的另一個指標,尤其是在稱重天平等應(yīng)用中,它可能需要50000個無噪聲計數(shù)。這個值的計算方法是將無噪聲分辨率轉(zhuǎn)換為2N因數(shù)的計數(shù)。例如,采用式210,一個理想10位ADC有1024個無噪聲計數(shù)。一個理想的12位 ADC有4096個無噪聲計數(shù)。同樣,采用相同的無噪聲分辨率值,該例可得218.9,合489178個無噪聲計數(shù)。

Δ-ΣADC的過采樣

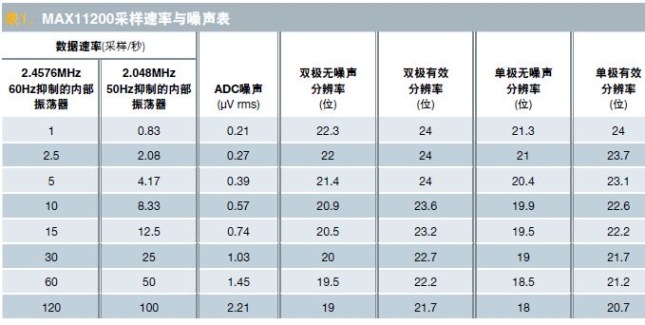

Δ-Σ ADC采用一種過采樣結(jié)構(gòu),這意味著ADC的內(nèi)部振蕩器/時鐘頻率高于輸出數(shù)據(jù)(或吞吐量)速率。有些Δ-Σ ADC可以改變輸出數(shù)據(jù)的速率,使設(shè)計者能夠優(yōu)化采樣,在最差噪聲情況下獲得較高速度,或用更多的過濾和噪聲整形(將噪聲推入測量區(qū)以外的頻段)而獲得較低速度和更好的噪聲性能。很多新的Δ-Σ ADC都以表格形式提供有效分辨率和無噪聲分辨率值,從而易于比較權(quán)衡。

表1給出了一個ADC的例子,包括雙極模式和單極輸入模式下的數(shù)據(jù)速率、噪聲、無噪聲分辨率,以及有效分辨率。24位的MAX11200 ADC既可以測雙極輸入,也可以測單極輸入。它的工作電壓為2.7V~3.6V,基準電壓最高可以偏置到電源電壓。雙極值基于±3.6V的最大輸入范圍,而單極測量則基于0V~3.6V的輸入范圍。

設(shè)計者可以通過軟件,對MAX11200內(nèi)部振蕩器編程,在較低的數(shù)據(jù)速率設(shè)置下為60Hz抑制的2.4576MHz,或在較低數(shù)據(jù)速率下50Hz抑制的2.048MHz。無論哪種數(shù)據(jù)速率,ADC噪聲都相同。因此,獲得的無噪聲分辨率與有效分辨率值都是一樣的。你可以為一個55Hz陷波濾波器采用外接振蕩器,可同時在50Hz與60Hz獲得好的抑制效果。

有效的雙極分辨率最大為24位,因為輸出的數(shù)據(jù)字長為24位。在三個最低的數(shù)據(jù)速率設(shè)置下,ADC的噪聲水平足夠的低,如果ADC要在串行接口上輸出24位以上數(shù)據(jù),則有效分辨率優(yōu)于24位。除非有數(shù)據(jù)輸出字的限制,否則有效分辨率總是比無噪聲分辨率好2.7 位。噪聲整形使Δ-Σ ADC能夠?qū)崿F(xiàn)低噪聲與高精度。

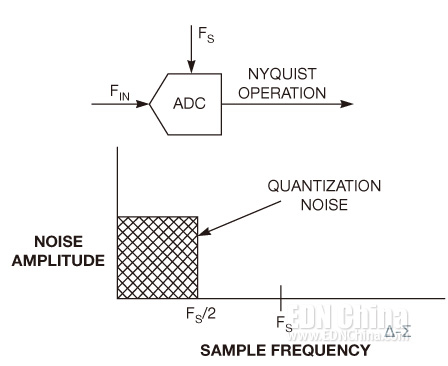

噪聲整形、過濾

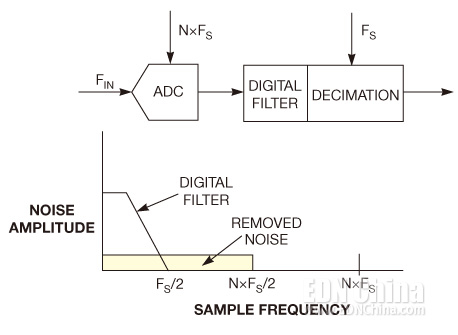

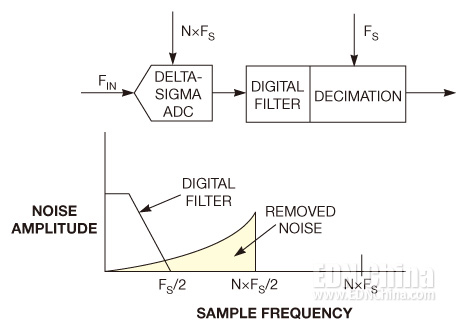

圖1是一個標準ADC的量化噪聲,圖2詳細描述了一只ADC,包括過采樣、數(shù)字濾波器,以及抽取。大多數(shù)采用過采樣的ADC核心是Δ-Σ單元。N倍過采樣會在較寬的頻帶上散播噪聲,而數(shù)字濾波器可消除大部分噪聲。圖3詳解了一個Δ-Σ調(diào)制器,它在圖2的相同塊中增加了噪聲整形。將噪聲推至不對稱的較高頻率,可使噪聲位于最低頻帶。這種技術(shù)使Δ-Σ ADC制造商能夠?qū)崿F(xiàn)優(yōu)于1μV rms的噪聲值。

圖1,一個標準ADC的噪聲性能弱于Δ-Σ ADC器件。

圖2,一個采用N倍過采樣、數(shù)字濾波器和抽取的ADC改進了噪聲性能。

圖3,在一個采用N倍過采樣、噪聲整形、數(shù)字濾波器、抽取的ADC中,ADC輸入頻帶內(nèi)的噪聲(黃色)大大降低。

有了過采樣能力和固有的低噪聲,Δ-Σ ADC成為需要較高分辨率的系統(tǒng)的最佳設(shè)計選擇。隨著設(shè)計者必須處理的信號越來越小,選擇正確ADC的關(guān)鍵就變?yōu)橐獪蚀_地理解ADC噪聲、有效分辨率、ENOB,以及無噪聲分辨率。