在數(shù)字電路設(shè)計(jì)中,時(shí)鐘信號(hào)是一種在高態(tài)與低態(tài)之間振蕩的信號(hào),決定著電路的性能。在應(yīng)用中,邏輯可能在上升沿、下降沿觸發(fā),或同時(shí)在上升沿和下降沿觸發(fā)。

由于溢出給定時(shí)鐘域的案例極多,故有必要插入緩沖器樹(shù)來(lái)充足地驅(qū)動(dòng)邏輯。時(shí)鐘樹(shù)通常帶有布線工程師必須滿足的延遲、歪曲率、最小功率及信號(hào)完整性 要求。

當(dāng)電路從前工序設(shè)計(jì)人員轉(zhuǎn)移到后工序布線工程師時(shí),可以認(rèn)為時(shí)鐘概述與圖表是必須溝通的最關(guān)鍵信息。多年以來(lái),由于溝通失誤,數(shù)以小時(shí)、天甚至是星期計(jì)的設(shè)計(jì)工作淪為白費(fèi),需要包括時(shí)鐘樹(shù)在內(nèi)的全套重新合成。在布線之前,采用極佳的時(shí)鐘來(lái)用于合成及時(shí)序約束。約束的時(shí)鐘定義可能出現(xiàn)在模塊的頂層焊盤(pán)或引腳;

可能出現(xiàn)在宏的輸出,如鎖延遲環(huán)(DLL) 或鎖相環(huán)(PLL);或者作為產(chǎn)生的時(shí)鐘出現(xiàn)在除法寄存器上。這些時(shí)鐘定義可能是也可能不是布線工程師需要定義時(shí)鐘樹(shù)根以在不同工作模式之間獲得最優(yōu)延遲 及平衡歪曲率的領(lǐng)域。

前工序及布線工程師之間圍繞這些信息的高級(jí)別信息溝通以及理解布線工程師怎樣運(yùn)用這些信息,將大幅優(yōu)化物理設(shè)計(jì)流程的CTS過(guò)程。

有效CTS的設(shè)計(jì)技巧

下面的某些技巧在業(yè)界已經(jīng)使用多年,但基于過(guò)去幾年的經(jīng)驗(yàn),仍然值得重復(fù)運(yùn)用。

為時(shí)鐘樹(shù)根使用中到大強(qiáng)度的驅(qū)動(dòng)器。這就使時(shí)鐘樹(shù)能有恰當(dāng)?shù)钠瘘c(diǎn)。但不要使用庫(kù)中最大的驅(qū)動(dòng)強(qiáng)度,如果信號(hào)完整性(SI)分析或片上變化(VOC)分析未出現(xiàn)問(wèn)題,能夠在隨后的設(shè)計(jì)中用到。

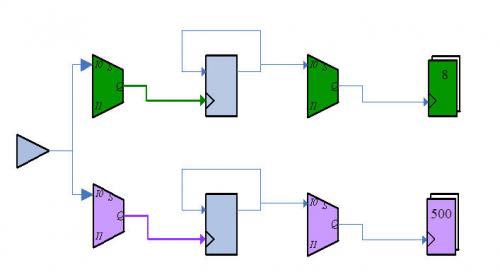

如果時(shí)鐘除法寄存器及其同步寄存器要在單獨(dú)測(cè)試模式中工作,確保它們被復(fù)用邏輯有針對(duì)性地驅(qū)動(dòng)。這就能夠在測(cè)試模式下在輸入端增加延遲,而不會(huì)影響此功能模式下所產(chǎn)生的時(shí)鐘驅(qū)動(dòng)的其他所有寄存器。(divide-by)寄存器不會(huì)與任何下行寄存器平衡。綠色域的寄存器數(shù)量越少,越會(huì)使時(shí)鐘速度比紫色域中的時(shí)鐘速度快得多。

圖1 寄存器時(shí)鐘除法寄存器

圖2顯示了可能使每簇下行寄存器及除法寄存器能夠通過(guò)復(fù)用的一種輸入擁有極小時(shí)鐘及通過(guò)復(fù)用的另一路輸入擁有平衡時(shí)鐘的復(fù)用機(jī)制。

圖2 下行寄存器及除法寄存器

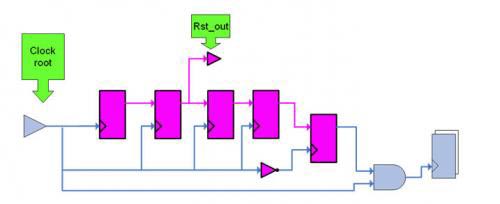

復(fù)用機(jī)制若有需要,則插入專(zhuān)用復(fù)位驅(qū)動(dòng)器。某些情況下將使用幾個(gè)寄存器來(lái)同步復(fù)位。那些寄存器可能并不需要由相同的寄存器來(lái)平衡。

在圖3中,由于未采用集中策略,軟件將嘗試平衡門(mén)控邏輯后的藍(lán)色寄存器,而每個(gè)粉紅色寄存器包含在復(fù)位同步邏輯中。

圖3 平衡門(mén)控邏輯后的寄存器

如果它們?cè)诟髯詫?zhuān)用驅(qū)動(dòng)器中與其他寄存器分開(kāi)了的話,在布線過(guò)程中這種情況就很容易處理。圖4顯示了可以怎樣在設(shè)計(jì)交遞(hand-off)溝通過(guò)程中插入及輕易識(shí)別占位符(place-holder)或排除緩沖器,使布線工程師知道哪里可能會(huì)出現(xiàn)平衡問(wèn)題。

圖4 插入及輕易識(shí)別占位符或排除緩沖器

提供超出預(yù)期的時(shí)鐘圖表及大量時(shí)鐘簡(jiǎn)介。當(dāng)前工序設(shè)計(jì)準(zhǔn)備好提供網(wǎng)表進(jìn)行布線時(shí),他們已經(jīng)非常熟悉設(shè)計(jì)及時(shí)鐘要求。

某些情況下,初始CTS設(shè)計(jì) 會(huì)提示預(yù)布線時(shí)序約束中使用的理想值在實(shí)際物理設(shè)計(jì)中不能實(shí)現(xiàn)的情況。如果提供了精確的時(shí)鐘圖以及帶有時(shí)鐘原理相關(guān)信息的網(wǎng)表交遞,就能夠更快地弄清導(dǎo)致 此狀況的問(wèn)題。

總體圖或是代表設(shè)計(jì)中所有時(shí)鐘(含門(mén)控邏輯)的圖非常有用。這要么是采用畫(huà)圖軟件,要么是使用電路圖捕獲工具等使用軟件產(chǎn)生的圖,甚至還可以是手繪并存儲(chǔ)為PDF文檔或發(fā)送傳真給布線工程師的圖。此圖抵得上嘗試直接獲得時(shí)鐘格式的多次通話或電子郵件溝通過(guò)程中的千言萬(wàn)語(yǔ)。由于圖表可能會(huì)很復(fù)雜繁瑣,就需要提供相應(yīng)的簡(jiǎn)介文檔,包括產(chǎn)生的時(shí)鐘、任何時(shí)鐘門(mén)控或復(fù)用圖案的詳情以及歪曲率平衡和延遲要求等方面的闡釋。