手機(jī)、數(shù)碼相機(jī)、MP3播放器和PDA等手持設(shè)備的設(shè)計(jì)工程師,正不斷地面臨著在降低整個(gè)系統(tǒng)成本的同時(shí)、又要以更小的體積提供更多功能的挑戰(zhàn)。集成電路設(shè)計(jì)工程師通過(guò)在減少硅片空間大小的同時(shí)提高設(shè)備的速度和性能,以此來(lái)推動(dòng)這一趨勢(shì)。為了使功能和芯片體積得到優(yōu)化,IC設(shè)計(jì)工程師要不斷地在他們的設(shè)計(jì)中使功能尺寸最小化。然而,要付出什么代價(jià)呢?IC功能尺寸的減少使得器件更易受到ESD電壓的損害。這種趨勢(shì)對(duì)終端產(chǎn)品的可靠性會(huì)產(chǎn)生不利的影響,并且會(huì)增加故障的可能性。因此,手持設(shè)備的設(shè)計(jì)工程師就要面對(duì)找到一種具有成本效益的ESD解決方案的挑戰(zhàn),這種方案能把電壓箝位到更低水平,以便使那些采用了對(duì)ESD越來(lái)越敏感的IC的終端產(chǎn)品保持高可靠性。

ESD波形

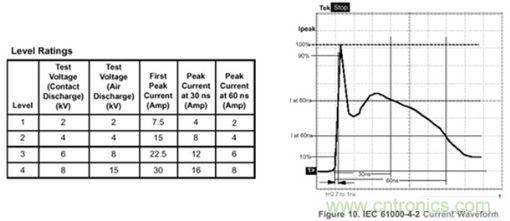

以系統(tǒng)級(jí)的方法來(lái)定義典型的ESD事件所采用的最常見(jiàn)的波形,是以其亞納秒上升時(shí)間和高電流電平(參見(jiàn)圖1)為顯著特征的IEC61000-4-2波形。這種波形的規(guī)范要求采用四級(jí)ESD量級(jí)。大部分設(shè)計(jì)工程師都要求把產(chǎn)品限定到最高級(jí)的8kV的接觸放電或15kV的空氣放電。當(dāng)進(jìn)行元器件級(jí)測(cè)試時(shí),因?yàn)榭諝夥烹姕y(cè)試在這樣的小型元器件上是不能重復(fù)的,接觸放電測(cè)試則是最適合的測(cè)試方式。

ESD方面所需考慮因素

ESD保護(hù)器件的目的是把數(shù)千伏電壓的ESD輸入電壓降低到所保護(hù)的IC所能承受的的安全電壓,并能把電流從IC旁路。雖然所需ESD波形的輸入電壓和電流在過(guò)去的幾年沒(méi)有出現(xiàn)變化,但要求保護(hù)IC的安全電壓電平卻降低了。過(guò)去,IC設(shè)計(jì)在ESD防護(hù)方面更具魯棒性,而且能夠承受更高電壓,因此,在選擇能符合IEC61000-4-2第4級(jí)的要求的保護(hù)二極管時(shí)有充分的選擇余地。而對(duì)于如今ESD更敏感的IC,設(shè)計(jì)工程師就必須不僅要確保保護(hù)器件能夠符合IEC61000-4-2第4級(jí)標(biāo)準(zhǔn),而且還要確保該器件能夠?qū)SD脈沖鉗制到足夠低的電平,從而確保IC不受損壞。在為給定的應(yīng)用選擇最佳保護(hù)器件的時(shí)候,設(shè)計(jì)工程師們必須要考慮到ESD保護(hù)器件能夠把ESD電壓控制到多么低的電平。

圖1:IEC61000-4-2規(guī)范指標(biāo)一覽表

選擇最有效的保護(hù)方案

保護(hù)二極管的關(guān)鍵DC指標(biāo)是擊穿電壓、漏電和電容。大部分?jǐn)?shù)據(jù)頁(yè)也會(huì)說(shuō)明IEC61000-4-2的最大額定電壓,該電壓指的是二極管在該電壓上不會(huì)被ESD沖擊損壞。所存在的問(wèn)題是,大部分?jǐn)?shù)據(jù)頁(yè)中沒(méi)有任何針對(duì)像ESD這樣的高頻率、高瞬態(tài)電流的箝位電壓方面的信息。可是要詳細(xì)說(shuō)明,要在IEC61000-4-2規(guī)范中硬性規(guī)定箝位電壓不是一件簡(jiǎn)單的事情,這是因?yàn)樵撘?guī)范的初衷是用來(lái)檢驗(yàn)系統(tǒng)是否合格,并且頻率是如此高。要把這種規(guī)范來(lái)檢驗(yàn)保護(hù)器件,關(guān)鍵的是不僅要檢查保護(hù)二極管是否合格/不合格,還要檢查它能把ESD電壓箝位到多么低的電平。

比較保護(hù)二極管箝位電壓的最好途徑是采用一臺(tái)示波器抓取保護(hù)二極管兩端在ESD產(chǎn)生期間內(nèi)的實(shí)際電壓波形。在觀察經(jīng)受IEC61000-4-2標(biāo)準(zhǔn)測(cè)試的ESD保護(hù)器件的電壓波形時(shí),通常初始電壓峰值之后緊隨著第二峰值,并且最終電壓將會(huì)穩(wěn)定下來(lái)。初始峰值是由IEC61000-4-2波形的初始電流峰值和由測(cè)試電路中存在的電感所導(dǎo)致的過(guò)沖相結(jié)合所造成的。初始峰值的持續(xù)時(shí)間很短,因此限定了傳輸?shù)絀C的能量。圖中曲線上顯示了保護(hù)器件的箝位性能,其位于第一個(gè)過(guò)沖之后。應(yīng)該重點(diǎn)關(guān)注第二個(gè)峰值,這是因?yàn)樵摲逯档某掷m(xù)時(shí)間較長(zhǎng),被測(cè)IC承受的能量將因此增加。在以下的討論中,箝位電壓被定義為第二峰值的最大電壓。

幾種保護(hù)二極管的比較

為了進(jìn)行公平的比較,所選元器件應(yīng)當(dāng)有相似的封裝尺寸和參數(shù)指標(biāo)。用來(lái)比較的是三只ESD保護(hù)二極管,當(dāng)對(duì)它們的電特性進(jìn)行比較時(shí),認(rèn)為這些器件可以彼此互換。這些器件都是雙向的ESD保護(hù)器件,具有同樣的擊穿電壓(6.8V)、電容(15pf)和封裝外形(1.0×0.6×0.4 mm)。這里所選擇的產(chǎn)品分別是競(jìng)爭(zhēng)對(duì)手1的RSB6.8CS、競(jìng)爭(zhēng)對(duì)手2的PG05DBTFC和安森美半導(dǎo)體的ESD9B5.0ST5G。

當(dāng)對(duì)以上器件的DC性能進(jìn)行比較的時(shí)候,結(jié)果看起來(lái)似乎是相同的(參見(jiàn)圖2所示曲線)。此外,它們都聲稱(chēng)符合IEC61000-4-2第4級(jí)標(biāo)準(zhǔn),這就意味著它們將都經(jīng)受住高達(dá)8kV接觸電壓的ESD沖擊。

圖2:三種ESD器件的DC特性對(duì)比

為了比較每個(gè)器件的箝位性能,利用示波器來(lái)抓取ESD發(fā)生期間的電壓波形。利用完全相同的測(cè)試條件,對(duì)上述器件進(jìn)行并排測(cè)試。圖3中顯示出每個(gè)二極管對(duì)正/負(fù)ESD脈沖的響應(yīng)曲線。所用的輸入脈沖為IEC61000-4-2 level 4的標(biāo)準(zhǔn)接觸電壓(8kV)。

圖3:三種ESD保護(hù)二極管的箝位電壓對(duì)比(示波器屏幕圖)

從圖3所示的圖上可見(jiàn),顯然,與兩個(gè)競(jìng)爭(zhēng)對(duì)手的器件(藍(lán)色波形)相比較,安森美半導(dǎo)體保護(hù)解決方案(黑色波形)可提供更低的ESD脈沖箝位電壓。與KEC的18V和Rohm的23V相比較,安森美的器件將正脈沖箝位在14V。而在負(fù)脈沖期間,這三個(gè)器件之間箝位電壓的差異更加明顯。安森美、競(jìng)爭(zhēng)對(duì)手2和競(jìng)爭(zhēng)對(duì)手1的器件對(duì)負(fù)脈沖的箝位電壓分別是20V、34V和42V。在負(fù)ESD期間這三種器件之間有明顯的區(qū)別,競(jìng)爭(zhēng)對(duì)手2的器件的箝位電壓比安森美的器件高70%,而競(jìng)爭(zhēng)對(duì)手1的器件的箝位電壓則是安森美器件的兩倍之多。通過(guò)競(jìng)爭(zhēng)對(duì)手的保護(hù)器件后的剩余負(fù)脈沖電壓對(duì)那些更容易受到ESD破壞的新IC設(shè)計(jì)有潛在的危險(xiǎn)。然而,安森美的器件卻能在負(fù)脈沖和正脈沖兩個(gè)方向上保持低的箝位電壓,從而將遭受正/負(fù)ESD脈沖的破壞風(fēng)險(xiǎn)都保持在最低水平。

好的保護(hù)器件需要對(duì)正/負(fù)ESD脈沖都能進(jìn)行很好的箝位,以保證終端產(chǎn)品在現(xiàn)實(shí)條件下實(shí)現(xiàn)最高的可靠性。在正/負(fù)兩個(gè)方向上的低箝位電壓確保器件能保護(hù)極敏感的IC,這使得設(shè)計(jì)工程師能利用可以實(shí)現(xiàn)更多功能和更高速度的最新IC技術(shù)。安森美半導(dǎo)體設(shè)計(jì)的保護(hù)器件不僅能夠使IC能夠經(jīng)受ESD沖擊,而且提供了市場(chǎng)上最低的箝位電壓。認(rèn)識(shí)到在選擇ESD保護(hù)器件時(shí)箝位電壓變得日益重要,安森美半導(dǎo)體在最新的保護(hù)器件的數(shù)據(jù)源中提供了類(lèi)似圖3中的鉗位特性。