隨著過去幾十年里掌上智能終端快速發(fā)展,低壓差的線性穩(wěn)壓器(Low Drop-out Regulator,LDO)因其具有低功耗、高的電源抑制比、體積小、電路設(shè)計簡單等優(yōu)點(diǎn)得到大量應(yīng)用。LDO大部分時間工作在低負(fù)載應(yīng)用,因此,其在低負(fù)載情況下的靜態(tài)電流消耗決定著電池的壽命。當(dāng)今的LDO發(fā)展趨勢是低電壓、低靜態(tài)電流來延長電池使用壽命。然而,低靜態(tài)電流會導(dǎo)致不穩(wěn)定性,帶來大的輸出電壓暫態(tài)變化,必須在靜態(tài)電流和輸出暫態(tài)特性進(jìn)行合理的折中。相比于傳統(tǒng)LDO采用分立結(jié)構(gòu)的帶隙基準(zhǔn)電壓源和誤差放大器,本文給出一種創(chuàng)新結(jié)構(gòu)的LDO,將帶隙基準(zhǔn)電壓源和誤差放大器兩個模塊合二為一,因此更容易實現(xiàn)低靜態(tài)電流消耗,低暫態(tài)電壓變化。

1 LDO電路分析

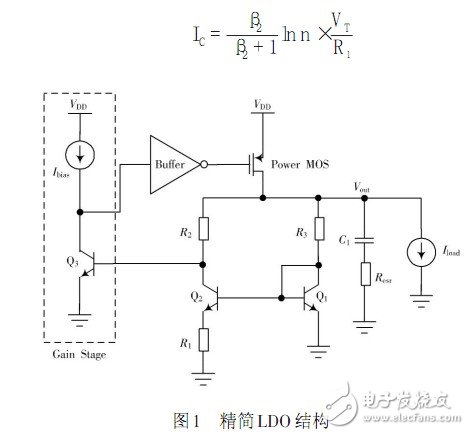

圖1給出精簡結(jié)構(gòu)的LDO,僅僅包括4條主要的電流支路,分別是:增益級、緩沖級和2個PTAT電流源。

相比傳統(tǒng)結(jié)構(gòu)LDO,精簡結(jié)構(gòu)將帶隙基準(zhǔn)電壓源和誤差放大器合二為一,因此在其他性能不變情況下,可將電路靜態(tài)電流消耗減小到原來1 2 左右。

這個電路存在兩個缺點(diǎn):輸出電壓為帶隙基準(zhǔn)電壓不可調(diào);需要使用NPN晶體管,而標(biāo)準(zhǔn)CMOS工藝中并不存在NPN晶體管。由于如今的SoC趨向工作在低電壓環(huán)境,因此這種結(jié)構(gòu)能夠有充足的應(yīng)用場合。第二個問題在單片設(shè)計時候,采用雙阱CMOS工藝,只需增加一道掩膜工藝,費(fèi)用增加不多,因此兩個問題實際應(yīng)用并不明顯。

1.1 帶隙基準(zhǔn)電壓分析

三極管基射級電壓和熱力學(xué)電壓分別具有負(fù)、正溫度系數(shù),因此帶隙基準(zhǔn)電壓的原理是疊加三極管基射級電壓和熱力學(xué)溫度電壓,達(dá)到在室溫下的零溫度系數(shù)。

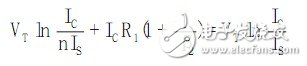

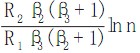

在精簡LDO結(jié)構(gòu)中,晶體管Q3和電阻R2定義帶隙基準(zhǔn)電壓,流過R2為PTAT電流。通過鏡像流過晶體管Q1電流。晶體管Q3偏置到集電極電流。因此,在環(huán)路中,晶體管Q1和Q3將調(diào)整到相同的基射級電壓值。尤其環(huán)路比較高的情況下,這種調(diào)整是相當(dāng)精確的。因此,通過合理設(shè)計電阻R2和R3,晶體管Q1,Q2和Q3有相同的集電極電流。因此:

式中:IS 是三極管飽和電流;β2 是晶體管Q2的電流增益;n 是晶體管Q2和Q1射級面積比。通過式(1)可以得到PTAT電流:

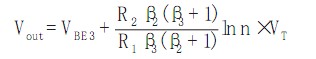

因此通過晶體管Q3的基射級電壓和R2電壓疊加即可得到輸出電壓值:

調(diào)整電阻比值,使VT 系數(shù) 值為17.2,即可得到溫度系數(shù)為零的帶隙基準(zhǔn)電壓。

值為17.2,即可得到溫度系數(shù)為零的帶隙基準(zhǔn)電壓。

1.2 LDO頻率分析

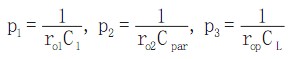

精簡結(jié)構(gòu)LDO中包含三個低頻極點(diǎn),分別處在增益級的輸出,緩沖級的輸出和LDO的輸出節(jié)點(diǎn),分別如下:

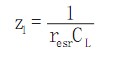

式中:ro1 和C1 分別是增益級輸出電阻和負(fù)載電容;ro2是緩沖級輸出電阻;Cpar 是功率管寄身電容;rop 是LDO輸出級的等效電阻;CL 為輸出負(fù)載補(bǔ)償電容。為了保證LDO有個良好的輸出暫態(tài)特性,CL 取值一般很大,因此極點(diǎn)p3 為LDO環(huán)路的主極點(diǎn)。晶體管Q3集電極電流偏置為PTAT電流,因此增益級的輸出阻抗隨輸出負(fù)載電流和輸入電壓變化不大,同時增益級的負(fù)載電容主要由緩沖級輸入電容決定,所以極點(diǎn)p1 位置相對穩(wěn)定,故可以采用一個左半平面的零點(diǎn)補(bǔ)償。類似如傳統(tǒng)LDO,本文采用一個電阻resr 與輸出補(bǔ)償電容串聯(lián)方式,獲得一個左半平面零點(diǎn):

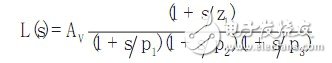

基于上述分析,精簡結(jié)構(gòu)LDO的開環(huán)傳輸函數(shù)為:

式中 .其中:gmQ2 ,gmQ3 和gmp 分別代表晶體管Q2,Q3和功率管的跨導(dǎo);Rπ 3 是晶體管Q3的輸入電阻。當(dāng)p1 和z1 匹配比較精確,LDO環(huán)路只有兩個低頻極點(diǎn)p2 和p3 。因此,為了獲得60°的相位裕度,必須:

.其中:gmQ2 ,gmQ3 和gmp 分別代表晶體管Q2,Q3和功率管的跨導(dǎo);Rπ 3 是晶體管Q3的輸入電阻。當(dāng)p1 和z1 匹配比較精確,LDO環(huán)路只有兩個低頻極點(diǎn)p2 和p3 。因此,為了獲得60°的相位裕度,必須:

2 電路設(shè)計與實現(xiàn)

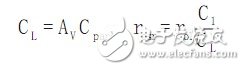

本文所提的低電壓、低靜態(tài)電流的精簡結(jié)構(gòu)的LDO如圖2所示。LDO的輸出級是一個A類共源級電路,包括PMOS功率管M1,三極管Q1、Q2,電阻R1,R2,R3,Resr和輸出負(fù)載補(bǔ)償電容C1.功率管M1有非常大的寬長比來驅(qū)動比較大的負(fù)載電流。因此M1的溝長選取最小的值,達(dá)到盡可能小的寄身電容和尺寸面積。為了獲取好的暫態(tài)輸出特性以及環(huán)路穩(wěn)定,輸出補(bǔ)償電容取5 μF.帶隙基準(zhǔn)電路包括三極管Q1,Q2,Q3和電阻R1,R2,R3.選取Q2的射級面積為Q1和Q3的射級面積8倍,這是Q2面積和R2阻值折中結(jié)果。三極管Q3和晶體管M6構(gòu)成一個共集電極的電路,為環(huán)路提供高增益。緩沖級包括晶體管M2,M3和M4.因為NMOS源跟隨器,在低負(fù)載情況下并不能完全關(guān)斷功率管,PMOS源跟隨器并不適合本電路的1.35低電壓環(huán)境,所以選用了二極管連結(jié)的PMOS負(fù)載共源級電路作為緩沖級。這種結(jié)構(gòu)不僅獲得低的輸出阻抗,同時達(dá)到180°的相位偏移,使整個閉環(huán)環(huán)路構(gòu)成一個負(fù)反饋。M3作用是在低負(fù)載電流的情況是為M4提供一些偏置電流,否則可能出現(xiàn)M4的柵源電壓過低,導(dǎo)致三極管Q3進(jìn)入飽和狀態(tài),降低Q3的電流增益,影響帶隙基準(zhǔn)電壓的精確度。通過Q4和M7構(gòu)成的偏置電路,使得三極管Q1,Q3有相等的集電極電流。晶體管M5,M8和M9構(gòu)成LDO的啟動電路。在剛有電壓輸入情況下,M8和M9構(gòu)成一個反相器輸出一個低電壓信號,使M5導(dǎo)通來啟動整個電路。

3 電路仿真結(jié)果

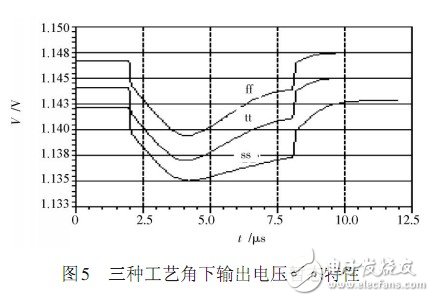

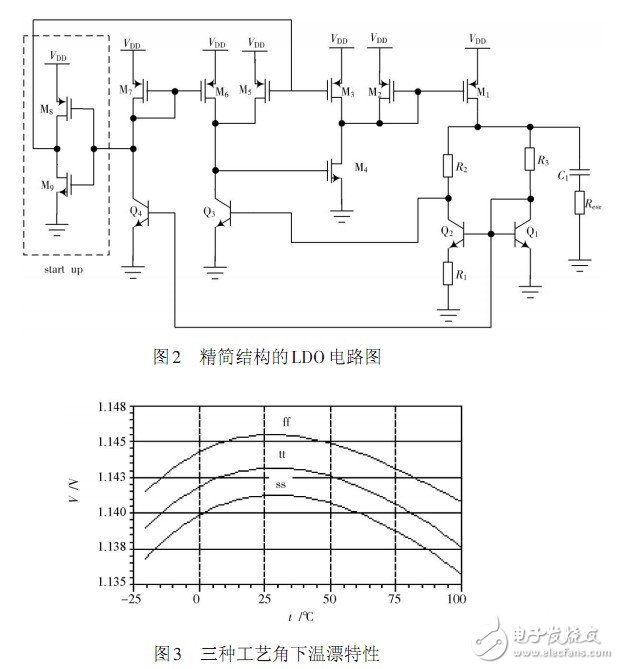

基于CSMC 0.5 μm 雙阱CMOS 工藝仿真模型,采用Cadence仿真軟件對精簡結(jié)構(gòu)LDO進(jìn)行了三個工藝角(tt,ff,ss)下仿真驗證。這個系統(tǒng)設(shè)計指標(biāo)的是讓LDO驅(qū)動最大30 mA的負(fù)載電流,同時保持輸出電壓穩(wěn)定在1.14 V,輸入電壓最小為1.35 V.LDO 的溫漂曲線如圖3所示。

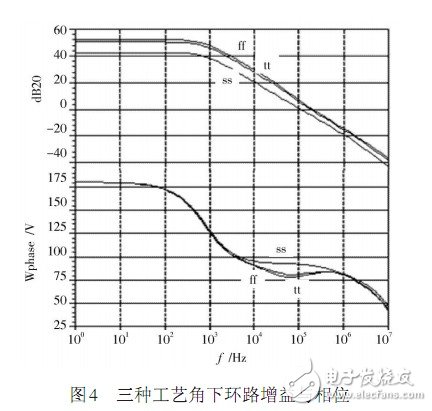

通過采用補(bǔ)償電容外接串聯(lián)電阻的方法,創(chuàng)造一個左半平面的零點(diǎn)來補(bǔ)償一個非主極點(diǎn),讓電路獲得比較好的環(huán)路相位裕度,在三個工藝角下,相位裕度都能達(dá)到70°(見圖4)。

暫態(tài)輸出電壓變化如圖5所示,當(dāng)負(fù)載電流從0~30 mA瞬態(tài)變化時,輸出電壓變化最大僅為9 mV.

4 結(jié)語

本文給出了一種低電壓1.14 V、低靜態(tài)電流1.7 μA 的LDO,通過將帶隙基準(zhǔn)電壓源與誤差放大器合二為一獲得精簡結(jié)構(gòu)的LDO.

因此實現(xiàn)了低靜態(tài)電流消耗,同時獲得較好的暫態(tài)輸出電壓性能,最大暫態(tài)電壓變化僅為9 mV.