汽車電子處于一個充滿噪聲的環(huán)境,因此汽車電子必須具有優(yōu)秀的電磁兼容(EMC)性能。而汽車電子的EMC設(shè)計(jì)中最主要的是微處理器的設(shè)計(jì),作者將結(jié)合實(shí)際設(shè)計(jì)經(jīng)驗(yàn),分析噪聲的產(chǎn)生機(jī)理并提出消除噪聲的方法。

汽車電子常常工作環(huán)境很惡劣:環(huán)境溫度范圍為-40oC到125oC;振動和沖擊經(jīng)常發(fā)生;有很多噪聲源,如刮水器電動機(jī)、燃油泵、火花點(diǎn)火線圈、空調(diào)起動器、交流發(fā)電機(jī)線纜連接的間歇切斷,以及某些無線電子設(shè)備,如手機(jī)和尋呼機(jī)等。

汽車設(shè)計(jì)中一般都有一個高度集成的微控制器,該控制器用來完成大量的計(jì)算并實(shí)現(xiàn)有關(guān)車輛運(yùn)行的控制,包括引擎管理和制動控制等。汽車電子設(shè)計(jì)不僅需要在這種噪聲環(huán)境中實(shí)現(xiàn)對MCU的保護(hù),同時也必須規(guī)范MCU模塊設(shè)計(jì),確保MCU模塊發(fā)射的噪聲滿足相關(guān)的規(guī)范。

在概念上,電磁兼容性(EMC)包含系統(tǒng)本身對噪聲的敏感性以及噪聲發(fā)射兩個部分。噪聲可以通過電磁場的方式傳播從而產(chǎn)生輻射干擾,也可以通過芯片上或者芯片外的寄生效應(yīng)傳導(dǎo)。

在大多數(shù)汽車控制系統(tǒng)設(shè)計(jì)中,EMC變得越來越重要。如果設(shè)計(jì)的系統(tǒng)不干擾其它系統(tǒng),也不受其它系統(tǒng)發(fā)射影響,并且不會干擾系統(tǒng)自身,那么所設(shè)計(jì)的系統(tǒng)就是電磁兼容的。

在美國出售的任何電子設(shè)備和系統(tǒng)都必須符合聯(lián)邦通訊委員會(FCC)制定的EMC標(biāo)準(zhǔn),而美國主要的汽車制造商也都有自己的一套測試規(guī)范來制約其供應(yīng)商。其它的汽車公司通常也都有各自的要求,如:

SAE J1113(汽車器件電磁敏感性測試程序)給出了汽車器件推薦的測試級別以及測試程序。

SAE J 1338則提供關(guān)于整個汽車電磁敏感性如何測試的相關(guān)信息。

SAE J1752/3和IEC 61967的第二和第四部分是專用于IC發(fā)射測試的兩個標(biāo)準(zhǔn)。

歐洲也有自己的標(biāo)準(zhǔn),歐盟EMC指導(dǎo)規(guī)范89/336/EEC于1996年開始生效,從此歐洲汽車工業(yè)引入了一個新的EMC指導(dǎo)標(biāo)準(zhǔn)(95/54/EEC)。

檢查汽車對于電磁輻射的敏感性,應(yīng)該確保整個汽車在20到1000MHz的90%帶寬范圍內(nèi)參考電平限制在24V/米的均方根值以內(nèi),在整個帶寬范圍以內(nèi)的均方根值在20V/米以內(nèi)。在測試過程中要試驗(yàn)駕駛員對方向盤、制動以及引擎速度的直接控制,而且不允許產(chǎn)生可能導(dǎo)致路面上任何其他人混淆的異常,或者駕駛員對汽車直接控制的異常。

由于芯片幾何尺寸不斷減小,以及時鐘速度的不斷增加都會導(dǎo)致器件發(fā)射超過500MHz的時鐘諧波,因此EMC設(shè)計(jì)非常重要。如摩托羅拉公司最新基于e500架構(gòu)的微控制器MPC5500系列,該芯片采用0.1微米工藝技術(shù),時鐘頻率為200MHz。

此外,產(chǎn)品成本的要求迫使生產(chǎn)商設(shè)計(jì)電路板時不使用地層并盡可能減少器件數(shù)量,汽車設(shè)計(jì)工程師將面對非常嚴(yán)格的設(shè)計(jì)約束挑戰(zhàn)。設(shè)計(jì)的電子系統(tǒng)必須高度可靠,即使一百萬輛汽車中有一輛存在一個簡單的故障都是不允許的。沒有考慮EMC設(shè)計(jì)而召回所有汽車的事實(shí)證明這種做法不僅損失巨大,而且影響汽車廠商的聲譽(yù)。

在電磁兼容設(shè)計(jì)中,“受害方”的概念通常指那些由于設(shè)計(jì)缺乏EMC考慮而受到影響的部件。受害部件可能在基于MCU的PCB或者模塊的內(nèi)部,也可能是外部系統(tǒng)。通常的受害部件是汽車免持鑰匙入車

(Keyless-Entry)模塊中的寬帶接收器或者是車庫門開啟裝置接收器,由于接收到MCU發(fā)出的足夠強(qiáng)的噪聲,這些模塊中的接收器會誤認(rèn)為接收到了一個遙控信號。

汽車收音機(jī)通常也是受害部件:MCU可能產(chǎn)生大量的FM波段諧波,嚴(yán)重降低聲音質(zhì)量。分布在汽車中的其它模塊也可能受到類似的影響,基于MCU的模塊產(chǎn)生的發(fā)射噪聲經(jīng)由線纜傳播出去,如果MCU產(chǎn)生足夠強(qiáng)的噪聲對文本和語音進(jìn)行干擾,那么無繩電話和尋呼機(jī)也容易受到干擾。

EMC設(shè)計(jì)

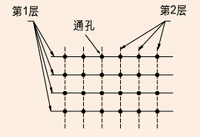

很多EMC設(shè)計(jì)技術(shù)都可以應(yīng)用到電路板和SoC設(shè)計(jì)中。最具共性的部分就是傳輸線效應(yīng),以及布線和電源分布網(wǎng)絡(luò)上的寄生電阻、電容和電感效應(yīng)。當(dāng)然,SoC設(shè)計(jì)中存在許多與芯片自身相關(guān)的技術(shù),涉及基底材料、器件幾何尺寸和封裝等。

首先了解傳輸線效應(yīng)。如果發(fā)送器和接收器之間存在阻抗不匹配,信號將產(chǎn)生反射并且導(dǎo)致電壓振鈴現(xiàn)象,因而降低噪聲容限,增加信號串?dāng)_并通過容性耦合對外產(chǎn)生信號發(fā)射干擾。IC上的傳輸線尺寸通常非常小,因此不會發(fā)射噪聲或者受到輻射噪聲的影響,而電路板上的傳輸線尺寸通常比較大,容易產(chǎn)生這種問題,最常用的解決辦法是使用串聯(lián)終結(jié)器。

在SoC設(shè)計(jì)中,噪聲主要通過寄生電阻和電容來傳導(dǎo),而不是以電磁場的方式輻射。CMOS芯片通過一種外延工藝實(shí)現(xiàn)極低電阻基底的方法來增強(qiáng)抗閉鎖的能力,而基底的底側(cè)為基底噪聲提供了一種有效的傳導(dǎo)路徑,使得很難將噪聲源同敏感節(jié)點(diǎn)在電氣上分隔開來。

許多并行的p+基底觸點(diǎn)(contact)為阻性耦合噪聲提供了一個低阻抗路徑。在n阱和p溝道晶體管p基底的側(cè)壁以及底部之間會形成寄生電容,因而產(chǎn)生容性耦合噪聲,并且在n溝道晶體管的基底和源區(qū)之間形成pn結(jié)(見圖1)。

單個pn結(jié)電容非常小,在一個VLSI的SoC設(shè)計(jì)中并行的電容總和通常是幾個納法,在連接到電源網(wǎng)絡(luò)之前將源區(qū)和基底直接連接可以短路掉這個電容。這種技術(shù)還消除了進(jìn)入基底的瞬時負(fù)電流而導(dǎo)致的體效應(yīng)(body effect)。體效應(yīng)會增加耗盡區(qū),并導(dǎo)致晶體管的Vt變高。同樣的技術(shù)也可以應(yīng)用于n阱p溝道晶體管,以減小容性耦合噪聲。

然而,包含層疊晶體管的數(shù)字電路或者模擬電路通常都需要隔離源區(qū)。在這種情況下,增加Vss到基底或者Vdd到基底的電容能夠降低噪聲瞬態(tài)值。對模擬電路設(shè)計(jì)來說,體效應(yīng)通過改變偏置電流和信號帶寬降低了電路性能,因此需要使用其它解決辦法,如阱隔離。對數(shù)字電路,采用單一的阱最理想,可以降低芯片面積。通過認(rèn)真的設(shè)計(jì)可以對體效應(yīng)進(jìn)行補(bǔ)償。

基底噪聲的另一個來源是碰撞離化(impact-ionization)電流,該噪聲跟工藝技術(shù)有關(guān),當(dāng)NMOS晶體管達(dá)到夾斷(pinch-off

)電壓時就會出現(xiàn)這種情況。碰撞離化會在基底產(chǎn)生空穴電流(正的瞬間電流)。

通常,基底噪聲的頻率范圍可能高達(dá)1GHz,因此必須考慮趨膚效應(yīng)。趨膚效應(yīng)是指導(dǎo)體上隨著深度的增加感應(yīng)系數(shù)增大,在導(dǎo)體的中心位置達(dá)到最大值。趨膚效應(yīng)會導(dǎo)致片上信號的衰減以及信號在芯片p+基底層的失真。為最大程度減小趨膚效應(yīng),要求基底厚度小于150微米,該尺寸遠(yuǎn)遠(yuǎn)小于某些基底允許的最小機(jī)械厚度,然而更薄的基底更易碎。

噪聲源

微控制器內(nèi)部存在四種主要的噪聲源:內(nèi)部總線和節(jié)點(diǎn)同步開關(guān)產(chǎn)生的電源和地線上的電流;輸出管腳信號的變換;振蕩器工作產(chǎn)生的噪聲;開關(guān)電容負(fù)載產(chǎn)生的片上信號假象。

許多設(shè)計(jì)方法可以降低同步開關(guān)噪聲(SSN)。穿透電流是SSN的一個主要來源,所有的時鐘驅(qū)動器、總線驅(qū)動器以及輸出管腳驅(qū)動器都可能受到這種效應(yīng)的影響。這種效應(yīng)發(fā)生在互補(bǔ)類型的反相器中,輸出狀態(tài)發(fā)生變化時p溝道晶體管和n溝道晶體管瞬間同時導(dǎo)通。確保在互補(bǔ)晶體管導(dǎo)通之前關(guān)斷另一個晶體管就可以實(shí)現(xiàn)穿透電流最小,在大電流驅(qū)動器的設(shè)計(jì)中,這可能要求一個前置驅(qū)動器來控制該節(jié)點(diǎn)信號的轉(zhuǎn)換率。

切斷不需要使用模塊的時鐘也可以降低SSN。很明顯,該技術(shù)同具體應(yīng)用十分相關(guān),應(yīng)用該技術(shù)可以提高EMC性能。在類似摩托羅拉的MPC555和565這樣高度集成的微控制器芯片中,所有芯片的外圍模塊都具有這樣的功能。

SSN也會產(chǎn)生輻射干擾,瞬間的電源和地電流會通過器件管腳流向外部的去耦電容。如果該電路(包括邦定線、封裝引線以及PCB線)形成的環(huán)路足夠大,就會產(chǎn)生信號發(fā)射。而環(huán)路中的寄生電感會產(chǎn)生電壓降,將進(jìn)一步產(chǎn)生共模輻射干擾。

共模輻射電場E的強(qiáng)度由下面等式計(jì)算:

E = 1.26 x 10-6 Iw f l/d

E = 1.26 x 10-6 Iw f l/d

這里E的單位是伏特/米,Iw的單位是安培,f是單位為赫茲,l是路徑長度,d是到該路徑的距離,l和d的單位都是米。復(fù)雜設(shè)計(jì)中頻率由特定的應(yīng)用需求來確定,不可能降低,因此SoC設(shè)計(jì)工程師必須認(rèn)真考慮如何通過降低Iw或l來降低電場強(qiáng)度。

處理好時鐘域也能降低SSN。許多優(yōu)秀的SoC設(shè)計(jì)都是同步電路,這樣容易在時鐘上下沿處產(chǎn)生很大的峰值電流。將時鐘驅(qū)動器分布在整個芯片中,而不是采用一個大的驅(qū)動器,這樣可以使瞬態(tài)電流分布開。另外一種可能的辦法是確保時鐘不互相重疊。當(dāng)然必須小心避免由于時序不匹配而產(chǎn)生競爭。更重要的是,時鐘信號應(yīng)該在遠(yuǎn)離敏感的I/O邏輯信號,特別是模擬電路。

當(dāng)前的復(fù)雜嵌入式MCU有許多輸出信號,大多數(shù)輸出信號都必須能夠快速地響應(yīng)電容負(fù)載。這些信號包括時鐘、數(shù)據(jù)、地址和高頻串行通信信號。對內(nèi)部節(jié)點(diǎn)來說,穿透電流和容性負(fù)載都會產(chǎn)生噪聲。應(yīng)用同樣的技術(shù)處理內(nèi)部節(jié)點(diǎn)可以解決輸出管腳驅(qū)動器電路噪聲問題。另外,管腳上信號的快速變換會產(chǎn)生反射引起的輸出信號線上的信號振鈴和串?dāng)_。

將這種類型的噪聲源減到最小有許多解決方案。輸出驅(qū)動器可以設(shè)計(jì)成驅(qū)動強(qiáng)度可以控制,并且可以增加信號轉(zhuǎn)換速率控制電路來限制di/dt。由于大多數(shù)器件測試設(shè)備同最終應(yīng)用相比,測試節(jié)點(diǎn)電容更高,所以通常更愿意指定一個固定值來實(shí)現(xiàn)驅(qū)動強(qiáng)度的控制。例如,假定MPC5XX系列的MCU微控制器芯片的CLKOUT滿驅(qū)動強(qiáng)度是一個90pF的負(fù)載,并且是專為測試目的而設(shè)定。除了因?yàn)闀r序而考慮滿驅(qū)動強(qiáng)度外,最好使用降低的驅(qū)動強(qiáng)度。

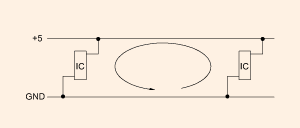

上面介紹的技術(shù)對于降低噪聲有積極的作用,由于瞬態(tài)電流包絡(luò)延長,平均的電流實(shí)際上會增加。在芯片上實(shí)現(xiàn)一個LVDS物理層也可以減小由于輸出管腳上大的瞬態(tài)電流產(chǎn)生的噪聲,這種方式依靠差模電流源來驅(qū)動低阻抗的外部負(fù)載(圖2)。電壓的擺幅限制在±300mV范圍內(nèi)。

支持這種技術(shù)所需增加的管腳可以通過減少電源管腳來彌補(bǔ),由于這種實(shí)現(xiàn)方式有效地降低了片上瞬態(tài)電流,因而輸出驅(qū)動器通過電源基本上維持一個恒定的直流電流,而傳統(tǒng)驅(qū)動器中的瞬態(tài)電流則會在電容性負(fù)載上產(chǎn)生大的電壓擺幅。

在振蕩器設(shè)計(jì)中有兩個方面會影響到EMC:輸入和輸出信號波形的形狀會產(chǎn)生影響;通過頻率抖動來實(shí)現(xiàn)頻譜展寬并降低其窄帶功率的能力。

振蕩器從本質(zhì)上屬于模擬電路,因而對工藝、溫度、電壓和負(fù)載效應(yīng)比SoC中的數(shù)字電路更敏感。使用自動增益控制(AGC)電路形式的反饋來限制振蕩器信號幅度可以消除大部分這些效應(yīng)。AGC的另外一種替代實(shí)現(xiàn)就是雙模式振蕩器,可以在高電流模式和低電流模式之間切換。初始狀態(tài)下,電源接通時使用高電流模式確保較短的啟動時間,然后切換到低電流模式確保最小噪聲。

在集成了作為振蕩器電路一部分的鎖相環(huán)的SoC設(shè)計(jì)中,可以利用頻率抖動在很小的范圍內(nèi)改變時鐘頻率,這樣隨著頻率在一個范圍上展開,可以減少基本能量。整個系統(tǒng)設(shè)計(jì)必須仔細(xì)考慮確保這種改變的比率以及頻率范圍不會影響最終應(yīng)用中關(guān)鍵器件的時序。而在類似CAN、異步SCI和定時的I/O功能等廣泛應(yīng)用于汽車的串行通信中不能采取該方式。芯片上的開關(guān)噪聲表明其自身就是期望信號輸出的一個阻尼振蕩,這是電感與芯片上負(fù)載電容串聯(lián)組合而產(chǎn)生的結(jié)果。對一個典型的片上總線來說,負(fù)載是一個連接到許多三態(tài)緩沖器的長的PCB布線,該負(fù)載的主體是電容,包括柵極,pn結(jié)以及互聯(lián)電容。

消除電感或者降低di/dt可以減小或者消除噪聲。只有當(dāng)噪聲幅度大到會引起連接節(jié)錯誤開關(guān)時,才需要認(rèn)真考慮設(shè)計(jì)中的噪聲問題。

降低對于外部噪聲源的敏感性包括對外部器件以及內(nèi)部設(shè)計(jì)的考慮。外部的瞬態(tài)電流會引起管腳上的兩種情況:電壓變化會導(dǎo)致容性耦合的電流進(jìn)入器件;超出電源范圍的電壓最終會通過電阻路徑將電流傳導(dǎo)到器件中。

汽車電子設(shè)計(jì)中,通常用外部RC濾波器來限制瞬態(tài)電壓擺幅和注入電流。必須小心,確保外部器件值考慮到漏電流效應(yīng),尤其是模擬輸入時。值得注意的是,MCU和外圍IC的I/O管腳通常多達(dá)200個,這種解決方案所需的額外成本和電路板空間使工程師在系統(tǒng)設(shè)計(jì)中不愿意采用。最好的解決辦法是實(shí)現(xiàn)在芯片上的高度集成。

硬件和軟件技術(shù)可以協(xié)同實(shí)現(xiàn)EMC性能要求。例如,許多MCU都具有在外部總線上輸出內(nèi)部訪問的能力,通常情況下這些都是不可見的。這種方式對于調(diào)試非常有用,但是在一些設(shè)計(jì)不當(dāng)?shù)南到y(tǒng)中可能會產(chǎn)生外部的總線競爭,從而使相關(guān)噪聲增加。

在過去的工作中我曾遇到芯片上A/D變換器讀取值不正確的類似問題,該問題看上去似乎噪聲在某種程度上干擾了測量或者是變換。通過了解系統(tǒng)的硬件結(jié)構(gòu)圖,從表面上了解A/D變換器的輸入部分似乎一切都很正常,但是我注意到外部的EPROM以某種方式實(shí)現(xiàn)解碼,而這種解碼方式在某些非常特殊的情況下可能會引起總線競爭,這種競爭不會影響程序的任何運(yùn)行,但是會產(chǎn)生足夠的噪聲,因此會出現(xiàn)A/D變換偶然的錯誤。通過改變解碼邏輯就迅速解決了這個問題。