文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2014)08-0007-03

紅外成像跟蹤系統(tǒng)通過(guò)紅外探測(cè)器獲得目標(biāo)的紅外圖像,然后對(duì)紅外圖像進(jìn)行預(yù)處理和潛在目標(biāo)檢測(cè),最后利用一定的算法對(duì)目標(biāo)進(jìn)行跟蹤。在實(shí)際系統(tǒng)設(shè)計(jì)中,一塊電路板往往難以完成所有功能,電路板與電路板之間需要進(jìn)行高速圖像傳輸和通信,因此設(shè)計(jì)一個(gè)傳輸速率快、可靠性高的圖像傳輸與通信平臺(tái)是紅外成像跟蹤系統(tǒng)的關(guān)鍵技術(shù)[1]。

由于并行總線在印制電路板上占空間量大,布線時(shí)很難保證每條線路長(zhǎng)度、電氣特征一致,兩條數(shù)據(jù)線間容易產(chǎn)生串?dāng)_等,因此隨著電子系統(tǒng)對(duì)速度以及精度要求的提高,高速串行數(shù)據(jù)通信模式正在逐步取代傳統(tǒng)的并行總線式結(jié)構(gòu)[2]。

串行傳輸?shù)难杆侔l(fā)展得力于差分信號(hào)技術(shù)的發(fā)展。在嵌入式應(yīng)用方面,主流的FPGA 中都已對(duì)差分信號(hào)提供了硬件支持,如Xilinx公司的Virtex系列FPGA中,相鄰的兩個(gè)I/O口都以差分信號(hào)對(duì)形式出現(xiàn)。從Virtex2 Pro系列開(kāi)始,更是在片上集成了固化的Rocket I/O模塊,以提供超高速的串行通信支持[3]。并且Xilinx公司針對(duì)高速傳輸開(kāi)發(fā)了一種可裁剪的輕量級(jí)鏈路層協(xié)議——Aurora協(xié)議,可以在相應(yīng)的器件上通過(guò)制定IP核生成[3]。

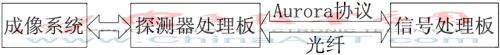

本文在基于Aurora IP核的基礎(chǔ)上構(gòu)建了一個(gè)圖像高速傳輸和通信平臺(tái),其總體設(shè)計(jì)框架如圖1所示。

圖1 高速圖像傳輸與通信平臺(tái)框架

探測(cè)器處理板與信號(hào)處理板在基于Aurora協(xié)議的基礎(chǔ)上通過(guò)光纖進(jìn)行圖像傳輸和通信。

1 高速圖像傳輸和通信平臺(tái)設(shè)計(jì)

1.1 硬件平臺(tái)搭建

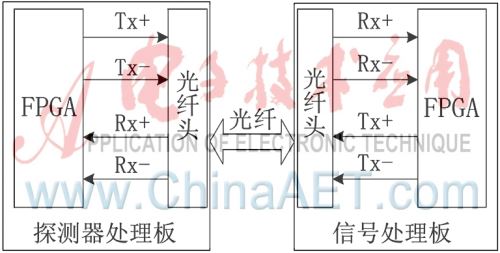

搭建高速圖像傳輸和通信平臺(tái)需要兩塊處理板,每塊處理板均需包含一片F(xiàn)PGA和一個(gè)光纖模塊。光纖模塊采用了中航光電的單光纖雙向收發(fā)一體光模塊OEA01-Dxx-326-613-01Y;FPGA采用了Xilinx公司的Virtex-5系列的XC5VLX50T-FF665,并采用100 MHz的時(shí)鐘模塊對(duì)Rocket I/O模塊提供參考時(shí)鐘,用一個(gè)XCF32P的PROM以主串模式對(duì)FPGA進(jìn)行配置[4-5];兩個(gè)光纖頭之間通過(guò)光纖相連。硬件平臺(tái)如圖2所示。

圖2 硬件平臺(tái)框圖

1.2 Aurora IP核的定制及生成

在Xilinx提供的CORE Generator工具中生成Aurora IP核[6]。其中通道數(shù)目設(shè)置為1,通道的寬度設(shè)置為2 B,數(shù)據(jù)速率為1.25 Gb/s,參考時(shí)鐘為100 MHz;為了使兩個(gè)處理板可以同時(shí)進(jìn)行數(shù)據(jù)收發(fā),數(shù)據(jù)流模式采用雙工模式;由于本紅外系統(tǒng)傳輸?shù)募t外圖像數(shù)據(jù)以幀為單位,傳輸過(guò)程中需要完整的幀有效信號(hào),故數(shù)據(jù)接口采取幀模式;因?yàn)樗O(shè)計(jì)平臺(tái)需要完成通信,需要用戶(hù)添加流控制信息,所以流控制模式采用UFC模式。

定制完成后,生成Aurora IP核,所生成的IP核主要包括以下功能模塊:

(1)用戶(hù)接口模塊(User Interface):用于提供用戶(hù)接口,處理來(lái)自用戶(hù)接口的控制信息。該模塊負(fù)責(zé)與Aurora核8 B/10 B模塊的接口,負(fù)責(zé)來(lái)自8 B/10 B編解碼模塊的數(shù)據(jù)讀寫(xiě)。數(shù)據(jù)端口的寬度取決于GTP/GTX的收發(fā)器的個(gè)數(shù)和寬度。

(2)用戶(hù)流控制模塊(User Flow Control Interface):幀模式下可選的一種流控制模式,該模塊可以在正常傳輸?shù)臄?shù)據(jù)流中添加控制信息,進(jìn)一步提高傳輸效率。本文中用作兩塊處理板通信的方式。

(3)時(shí)鐘模塊(Clock Interface):包括時(shí)鐘生成模塊和時(shí)鐘接口模塊,用于生成整個(gè)系統(tǒng)所需的時(shí)鐘。該模塊主要由PLL(時(shí)鐘延遲鎖相環(huán))和BUFG(全局時(shí)鐘緩沖器)構(gòu)成。PLL和BUFG構(gòu)成時(shí)鐘產(chǎn)生模塊,生成GTP收發(fā)器內(nèi)所需的各種時(shí)鐘。

(4)時(shí)鐘補(bǔ)償模塊(Clock Compensation Interface):該模塊內(nèi)嵌于數(shù)據(jù)傳輸模塊中,對(duì)整個(gè)Aurora模塊提供時(shí)鐘補(bǔ)償。由于信道兩端設(shè)備的參考時(shí)鐘必然存在或多或少的差異,時(shí)鐘相位偏差不可避免,為了保證接收端能正確地恢復(fù)數(shù)據(jù),時(shí)鐘補(bǔ)償模塊必不可少。接收端根據(jù)接收數(shù)據(jù)流內(nèi)嵌的時(shí)鐘補(bǔ)償信息對(duì)自身參考時(shí)鐘進(jìn)行修正,以降低誤碼。

(5)GTP/GTX接口模塊(Transceiver Interface):吉比特收發(fā)器模塊,用于控制數(shù)據(jù)的收發(fā)。該模塊為Aurora協(xié)議中與物理層接口模塊,是Aurora模塊中最重要的模塊之一[7]。不過(guò)ISE軟件生成Aurora 例程之后,該接口模塊自動(dòng)生成,普通的使用中幾乎不需要修改該模塊。

在生成Aurora IP核后,必須對(duì)Aurora IP核進(jìn)行正確配置才能正常使用,Xilinx的CORE Generator工具在生成一個(gè)Aurora IP核的同時(shí)還會(huì)生成一個(gè)示例工程,工程中包含了一些與Aurora IP核各功能模塊相對(duì)應(yīng)的配置模塊,包括時(shí)鐘配置模塊(clock_module)、時(shí)鐘補(bǔ)償配置模塊(standardard_cc_module)、復(fù)位配置模塊(reset_logic)、幀發(fā)送配置模塊(frame_gen)、幀接收配置模塊(frame_check)。示例工程可以直接使用,但是需要進(jìn)行修改才可以完成自己所需要的功能,一般需要修改工程中的幀發(fā)送配置模塊、幀接收配置模塊和時(shí)鐘補(bǔ)償配置模塊。

1.3 圖像發(fā)送接收配置及UFC通信設(shè)置

紅外探測(cè)器接收到的圖像為640×512個(gè)像素,在Aurora的幀傳輸模式下,每幀圖像中的一行有640個(gè)字,用512幀可將圖像傳輸完畢。與此相對(duì)應(yīng),圖像接收模塊處于一直等待接收模式下,每次接收一幀,即為圖像對(duì)應(yīng)的一行。

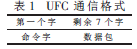

通過(guò)配置用戶(hù)流控制模塊來(lái)進(jìn)行兩個(gè)處理板之間的指令傳輸,發(fā)送UFC信息無(wú)需等待一幀數(shù)據(jù)發(fā)送完畢,可以先發(fā)送請(qǐng)求,請(qǐng)求被許可之后就可以立即發(fā)送。UFC信息最多可以一次發(fā)送8個(gè)字,即16 B的數(shù)據(jù)。對(duì)這8個(gè)字進(jìn)行定義,用來(lái)進(jìn)行通信,格式定義如表1所示。

按照上述要求修改發(fā)送配置模塊、幀接收配置模塊,實(shí)現(xiàn)圖像發(fā)送和接收。ISE 生成的例程中的時(shí)鐘補(bǔ)償配置模塊由定時(shí)器產(chǎn)生DO_CC 信號(hào),GTP 收發(fā)器模塊根據(jù)DO_CC 信號(hào)的有效長(zhǎng)度來(lái)產(chǎn)生時(shí)鐘補(bǔ)償序列。如果直接使用會(huì)導(dǎo)致TX_DST_RDY_N信號(hào)不定期地?zé)o效,從而會(huì)引起在幀模式傳輸時(shí)不定期中斷,從而導(dǎo)致傳輸效率的下降。在實(shí)際應(yīng)用中,以每幀640個(gè)字的方式進(jìn)行傳輸。為了解決不定期中斷這一問(wèn)題,重新設(shè)計(jì)了DO_CC 模塊。采用方式如下:

(1)對(duì)時(shí)鐘周期USER_CLK進(jìn)行計(jì)數(shù),計(jì)數(shù)到5 000時(shí)做一個(gè)長(zhǎng)度為10個(gè)時(shí)鐘周期的DO_CC,并將計(jì)數(shù)清零。

(2)當(dāng)需要發(fā)送圖像時(shí),在每次發(fā)送一幀640個(gè)字之前做一個(gè)10個(gè)時(shí)鐘周期的DO_CC,并將計(jì)數(shù)清零;

(3)當(dāng)需要發(fā)送一個(gè)UFC通信時(shí),在發(fā)送之前做一個(gè)10個(gè)時(shí)鐘周期的DO_CC,并將計(jì)數(shù)清零。

2 實(shí)驗(yàn)驗(yàn)證

為了驗(yàn)證所設(shè)計(jì)的通信平臺(tái),設(shè)計(jì)了一個(gè)實(shí)驗(yàn)驗(yàn)證方案,方案如下:

(1)探測(cè)器處理板將接收到的熱紅外圖像發(fā)送到信號(hào)處理板,圖像大小為513×640,以Aurora的幀模式,一幀發(fā)送一行,前512行為圖像數(shù)據(jù)。第513行為附加信息,513行的前兩個(gè)字為固定字符,用來(lái)作為圖像起始信號(hào)。在信號(hào)處理板上設(shè)置檢驗(yàn)邏輯,根據(jù)在513行中設(shè)置的圖像起始信號(hào),計(jì)算兩個(gè)圖像起始信號(hào)之間的幀起始信號(hào)rx_sof_n_i的個(gè)數(shù),如果個(gè)數(shù)始終為513,則證明沒(méi)有丟行。同理,計(jì)算幀起始rx_sof_n_i和幀結(jié)束信號(hào)rx_eof_n_i之間的USER_CLK的個(gè)數(shù),如果個(gè)數(shù)始終為640,則證明沒(méi)有丟字。

(2)探測(cè)器處理板以UFC方式發(fā)送數(shù)據(jù)包,重復(fù)發(fā)送一萬(wàn)次,在探測(cè)器處理板上將每次接收到的數(shù)據(jù)與發(fā)送數(shù)據(jù)進(jìn)行比對(duì),如果完全相同則計(jì)數(shù)器加1,如果計(jì)數(shù)值能夠達(dá)到10 000,則證明UFC通信沒(méi)有出錯(cuò)。

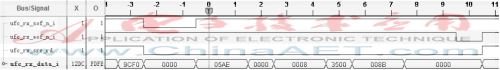

實(shí)驗(yàn)結(jié)果表明,在傳輸圖像時(shí),沒(méi)有出現(xiàn)丟行和丟字的現(xiàn)象;在發(fā)送10 000個(gè)UFC數(shù)據(jù)包時(shí),正確率為100%。圖3和圖4是分別是通過(guò)ChipScope[8]抓取的圖像傳輸信號(hào)和UFC傳輸信號(hào)。

圖3 圖像傳輸信號(hào)

圖4 UFC傳輸信號(hào)

本文在基于Aurora IP核的基礎(chǔ)上構(gòu)建了一個(gè)圖像高速傳輸和通信平臺(tái),使得兩塊處理板之間的圖像傳輸和通信可以通過(guò)一根光纖實(shí)現(xiàn),大大簡(jiǎn)化了系統(tǒng)。通過(guò)實(shí)驗(yàn)驗(yàn)證,所構(gòu)建的圖像高速傳輸和通信平臺(tái)工作性能穩(wěn)定,其中圖像沒(méi)有出現(xiàn)丟行和丟字現(xiàn)象,基于UFC模式傳輸?shù)耐ㄐ胚B續(xù)發(fā)送10 000個(gè)數(shù)據(jù)包時(shí)沒(méi)有出現(xiàn)一個(gè)錯(cuò)誤。目前所設(shè)計(jì)的圖像高速傳輸和通信平臺(tái)已應(yīng)用于紅外成像跟蹤系統(tǒng)、雷達(dá)信號(hào)處理等場(chǎng)合。

參考文獻(xiàn)

[1] 張琳琳,張涌.Aurora協(xié)議在紅外告警系統(tǒng)中的應(yīng)用[J].科學(xué)技術(shù)與工程,2012,12(21):5308-5311.

[2] 陳長(zhǎng)林,邱兆坤.RocketIO及其在高速數(shù)據(jù)傳輸中的應(yīng)用[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用.2010(11):25-28.

[3] Xilinx Inc..RocketIOTM transceiver user guide UG024 (v3.0)

[EB/OL].(2007-02-22)[2014-04-28].http://www.xilinx.com.

[4] Xilinx Inc..Virtex-5 FPGA data sheet:DC and switching characteristics DS202(v5.3)[EB/OL](2010-05-05)[2014-04-28].http://www.xilinx.com.

[5] 岳振,顧海峰,李范鳴.基于Verilog HDL的一種絕對(duì)值編碼器實(shí)時(shí)讀出算法[J].微型機(jī)與應(yīng)用,2013,32(3):29-31.

[6] Xilinx Inc..LogiCORETM IP Aurora 8B/10B v6.1 user guideug766[EB/OL].(2010-09-21)[2014-04-28].http://www.xilinx.com.

[7] Xilinx Inc..Aurora 8B/10B protocol specification SP002 (v2.2)[EB/OL].(2010-04-19)[2014-04-28].http://www.xilinx.com.

[8] Xilinx Inc..ChipScope Pro Tutorial:using an IBERT core with ChipScope Pro Analyzer UG811(v13.1)[EB/OL].(2011-04-01)[2014-04-28].http://www.xilinx.com.

(收稿日期:2014-05-01)

作者簡(jiǎn)介:

岳振,男,1988年生,博士研究生,主要研究方向:紅外圖像處理及FPGA開(kāi)發(fā)等。

李范鳴,男,1969年生,研究員,博士生導(dǎo)師,主要研究方向:紅外光電系統(tǒng)工程及信息與圖像處理技術(shù)。