LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(PSRR)。SGM2007高性能低壓差線性穩(wěn)壓器在10Hz至100kHz頻率范圍內(nèi)的輸出噪聲為30µV(RMS),在1kHz的頻率下電源抑制比(PSRR)高達73dB,它能夠為諸如射頻(RF)接收器和發(fā)送器、壓控振蕩器(VCO)和音頻放大器等對噪聲敏感的模擬電路的供電提供低噪聲、電源紋波抑制比(PSRR)和快速瞬態(tài)響應,它的使能電路兼容TTL電平適合數(shù)字電路供電。SGM2007的輸入電壓在2.5V至5.5V之間,適合藍牙數(shù)碼相機和個人數(shù)字助理(PDA),以及諸如無線和高端音頻產(chǎn)品等單個鋰電池供電或固定3.3V和5V系統(tǒng)。

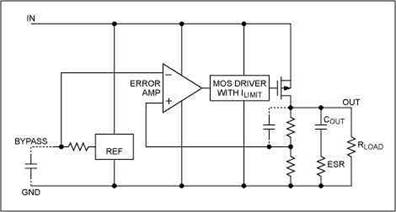

LDO的低壓差線性穩(wěn)壓器的結構主要包括啟動電路、恒流源偏置單元、使能電路、調(diào)整元件、基準源、誤差放大器、反電阻網(wǎng)絡,保護電路等,基本工作原理是這樣的:系統(tǒng)加電,如果使能腳處于高電平時,電路開始啟動,恒流源電路給整個電路提供偏置,基準源電壓快速建立,輸出隨著輸入不斷上升,當輸出即將達到規(guī)定值時,由反饋網(wǎng)絡得到的輸出反饋電壓也接近于基準電壓值,此時誤差放大器將輸出反饋電壓和基準電壓之間的誤差小信號進行放大,再經(jīng)調(diào)整管放大到輸出,從而形成負反饋,保證了輸出電壓穩(wěn)定在規(guī)定值上;同理如果輸入電壓變化或輸出電流變化,這個閉環(huán)回路將使輸出電壓保持不變,即:

Vout=(R1+R2)/R2*Vref

Powersupplyripplerejectionratio(PSRR)是反應LDO輸出對輸入紋波抑制的一個交流參數(shù),輸出和輸入的頻率是一樣的。和噪聲(Nosie)不同,噪聲一般為在10Hz至100kHz頻率范圍內(nèi)一定輸入電壓下其輸出噪聲電壓的均方值,PSRR的單位是dB。

PSRR=20log(△vin/△vout)

大多數(shù)蜂窩電話基帶芯片組需要三組電源:內(nèi)部數(shù)字電路、模擬電路和外設接口電路。基帶處理器(BB)的數(shù)字電路供電電壓的典型值為1.8V至2.6V,一般情況下,Li+電池電壓降至3.2V-3.3V時電話將被關閉,對于為基帶處理器供電的LDO來說至少有500至600mV的壓差,因此對壓差要求不高。另外,數(shù)字電路本身對LDO的輸出噪聲和PSRR的要求也不高,而是要求LDO在輕載條件下具有極低的靜態(tài)電流。

基帶處理器內(nèi)部模擬電路供電電壓典型值是2.4V至3.0V,壓差在200mV至600mV。要求LDO具有較高的低頻(GSM電話為217Hz)紋波抑制能力,消除由RF功率放大器產(chǎn)生的電池電壓紋波。LDO始終保持有效工作狀態(tài),同樣需要較低的靜態(tài)電流指標。

RF電路分為接收和發(fā)送兩部分,供電電壓典型值為2.6V至3.0V,其中低噪聲放大器(LNA)、混頻器、鎖相環(huán)(PLL)、壓控振蕩器(VCO)和中頻(IF)電路需要低噪聲、高PSRR的LDO。實際應用中,VCO、PLL電路的性能直接影響射頻電路指標,如發(fā)射頻譜的純度、接收器的選擇性、模擬收發(fā)器的噪聲、數(shù)字電路的相位誤差等。噪聲會改變振蕩器的相頻和幅頻特性,同時振蕩器環(huán)路也會進一步放大噪聲,可能對載波產(chǎn)生調(diào)制。LDO輸出噪聲受其內(nèi)部設計和外部旁路、補償電路的影響。如圖是線性穩(wěn)壓器的簡單框圖。導致LDO輸出噪聲的主要來源是基準。

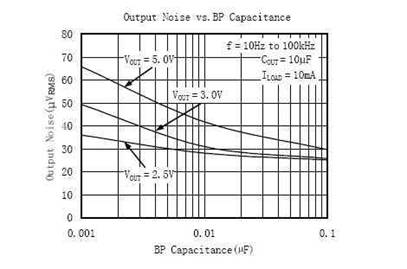

為降低基準噪聲,用于連接基準旁路電容。增大旁路電容能夠使基準噪聲成為產(chǎn)生LDO輸出噪聲的次要因素,有利于減小輸出噪聲。建議使用陶瓷電容的典型值為470pF到0.01µF。也可使用此范圍以外的電容,但會對輸入電源上電時LDO輸出電壓上升的速度產(chǎn)生影響,旁路電容值越大,輸出電壓上升速率越慢。在使用時這點要注意。

影響LDO輸出噪聲的其它因素還有:LDO內(nèi)部極點、零點和輸出極點。增大輸出電容的容量或減輕輸出負載有利于降低高頻輸出噪聲。如圖為旁路電容對SG2001輸出噪聲影響。

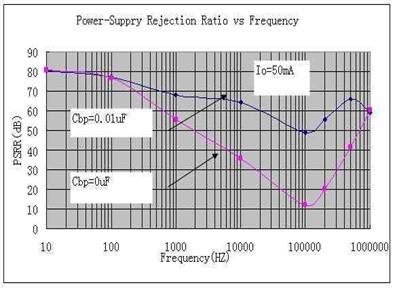

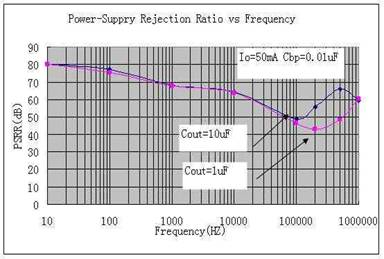

如圖為旁路電容對SGM2007PSRR影響

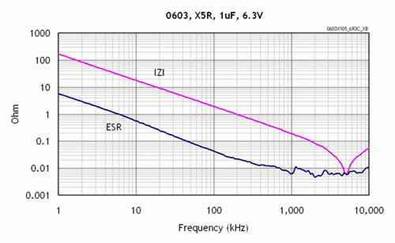

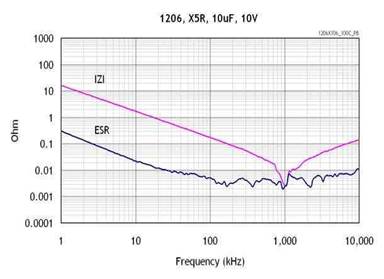

LDO需要增加外部輸入和輸出電容器。利用較低ESR的大電容器一般可以全面提高電源抑制比(PSRR)、噪聲以及瞬態(tài)性能。陶瓷電容器通常是首選,因為它們價格低而且故障模式是斷路,相比之下鉭電容器比較昂貴且其故障模式是短路。輸出電容器的等效串電阻(ESR)會影響其穩(wěn)定性,陶瓷電容器具有較低的ESR,大概為10mΩ量級采用陶瓷電容時,建議使用X5R和X7R電介質(zhì)材料,這是因為它們具有較好的溫度穩(wěn)定性。圖為X5R的ESR和頻率曲線。

如圖為輸出電容對PSRR的影響。大電容器一般在一定頻率范圍內(nèi)會提高電源抑制比(PSRR)

為射頻電路選擇LDO時,要慎重比較噪聲指標,和電源抑制比(PSRR),確保旁路電容、輸出電容和負載條件一致。新型音頻電路,如免提電話、游戲機、MP3及蜂窩電話中的多媒體電路,可能需要300mA-500mA的大電流LDO,LDO要在音頻范圍(20Hz至20kHz)應具有低噪聲、高PSRR特性,以保證良好的音質(zhì)。