FPGA的低功耗設(shè)計(jì)

韓雪,郭文成

來(lái)源:21IC

摘要: 芯片對(duì)功耗的苛刻要求源于產(chǎn)品對(duì)功耗的要求,。集成電路的迅速發(fā)展以及人們對(duì)消費(fèi)類電子產(chǎn)品——特別是便攜式(移動(dòng))電子產(chǎn)品——的需求日新月異,,使得設(shè)計(jì)者對(duì)電池供電的系統(tǒng)已不能只考慮優(yōu)化速度和面積,而必須注意越來(lái)越重要的第三個(gè)方面——功耗,,這樣才能延長(zhǎng)電池的壽命和電子產(chǎn)品的運(yùn)行時(shí)間,。很多設(shè)計(jì)抉擇可以影響系統(tǒng)的功耗,,包括從器件選擇到基于使用頻率的狀態(tài)機(jī)值的選擇等。

Abstract:

Key words :

芯片對(duì)功耗的苛刻要求源于產(chǎn)品對(duì)功耗的要求,。集成電路的迅速發(fā)展以及人們對(duì)消費(fèi)類電子產(chǎn)品——特別是便攜式(移動(dòng))電子產(chǎn)品——的需求日新月異,,使得設(shè)計(jì)者對(duì)電池供電的系統(tǒng)已不能只考慮優(yōu)化速度和面積,而必須注意越來(lái)越重要的第三個(gè)方面——功耗,這樣才能延長(zhǎng)電池的壽命和電子產(chǎn)品的運(yùn)行時(shí)間,。很多設(shè)計(jì)抉擇可以影響系統(tǒng)的功耗,,包括從器件選擇到基于使用頻率的狀態(tài)機(jī)值的選擇等。

1 FPGA功耗的基本概念

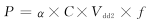

(1) 功耗的組成

功耗一般由兩部分組成:靜態(tài)功耗和動(dòng)態(tài)功耗,。靜態(tài)功耗主要是晶體管的漏電流引起,,由源極到漏極的漏電流以及柵極到襯底的漏電流組成;動(dòng)態(tài)功耗主要由電容充放電引起,,其主要的影響參數(shù)是電壓,、節(jié)點(diǎn)電容和工作頻率,可以用式(1)表示[1],。

(2) 靜態(tài)功耗

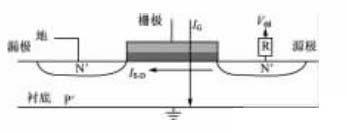

靜態(tài)功耗主要是由漏電流引起,。漏電流是芯片上電時(shí),無(wú)論處于工作狀態(tài)還是處于靜止?fàn)顟B(tài),,都一直存在的電流,,來(lái)源于晶體管的三個(gè)極,如圖1所示,。它分為兩部分,,一部分來(lái)自源極到漏極的泄漏電流ISD,另一部分來(lái)自柵極到襯底的泄漏電流IG,。漏電流與晶體管的溝道長(zhǎng)度和柵氧化物的厚度成反比[2],。

靜態(tài)功耗主要是由漏電流引起,。漏電流是芯片上電時(shí),無(wú)論處于工作狀態(tài)還是處于靜止?fàn)顟B(tài),,都一直存在的電流,,來(lái)源于晶體管的三個(gè)極,如圖1所示,。它分為兩部分,,一部分來(lái)自源極到漏極的泄漏電流ISD,另一部分來(lái)自柵極到襯底的泄漏電流IG,。漏電流與晶體管的溝道長(zhǎng)度和柵氧化物的厚度成反比[2],。

圖1 靜態(tài)功耗的組成

源極到漏極的泄漏電流是泄漏的主要原因。MOS管在關(guān)斷的時(shí)候,,溝道阻抗非常大,,但是只要芯片供電就必然會(huì)存在從源極到漏極的泄漏電流。隨著半導(dǎo)體工藝更加先進(jìn),,晶體管尺寸不斷減小,,溝道長(zhǎng)度也逐漸減小,使得溝道阻抗變小,,從而泄漏電流變得越來(lái)越大,,而且源極到漏極的漏電流隨溫度增加呈指數(shù)增長(zhǎng)。

(3) 動(dòng)態(tài)功耗

動(dòng)態(tài)功耗主要由電容充放電引起,,它與3個(gè)參數(shù)有關(guān):節(jié)點(diǎn)電容,、工作頻率和內(nèi)核電壓,它們與功耗成正比例關(guān)系,。如式(1)所示,節(jié)點(diǎn)電容越大,,工作頻率越高,,內(nèi)核電壓越大,其動(dòng)態(tài)功耗也就越高,。而在 FPGA中動(dòng)態(tài)功耗主要體現(xiàn)為存儲(chǔ)器,、內(nèi)部邏輯,、時(shí)鐘、I/O消耗的功耗,。在一般的設(shè)計(jì)中,,動(dòng)態(tài)功耗占據(jù)了整個(gè)系統(tǒng)功耗的90%以上,所以降低動(dòng)態(tài)功耗是降低整個(gè)系統(tǒng)功耗的關(guān)鍵因素,。

(4) 降低功耗帶來(lái)的好處

① 低功耗的器件可以實(shí)現(xiàn)更低成本的電源供電系統(tǒng),。另外,更簡(jiǎn)單的電源系統(tǒng)意味著更少的元件和更小的PCB面積,,同樣可以降低成本[3],。

② 更低的功耗引起的結(jié)溫更小,因此可以防止熱失控,,可以少用或不用散熱器,,如散熱風(fēng)扇、散熱片等,。

③ 降低功耗可以降低結(jié)溫,,而結(jié)溫的降低可以提高系統(tǒng)的可靠性。另外,,較小的風(fēng)扇或不使用風(fēng)扇可以降低EMI[3],。

④ 延長(zhǎng)器件的使用壽命。器件的工作溫度每降低10 ℃,,使用壽命延長(zhǎng)1倍,。

所以對(duì)于FPGA而言,降低功耗的根本在于直接提高了整個(gè)系統(tǒng)的性能和質(zhì)量,,并減小了體積,,降低了成本,對(duì)產(chǎn)品有著非常大的促進(jìn)作用,。

(5) 如何降低FPGA功耗

FPGA主要的功耗是由靜態(tài)功耗和動(dòng)態(tài)功耗組成,,降低FPGA的功耗就是降低靜態(tài)功耗和動(dòng)態(tài)功耗。

靜態(tài)功耗除了與工藝有關(guān)外,,與溫度也有很大的關(guān)系,。一方面需要半導(dǎo)體公司采用先進(jìn)的低功耗工藝來(lái)設(shè)計(jì)芯片,降低泄漏電流(即選擇低功耗的器件),;另一方面可以通過(guò)降低溫度,、結(jié)構(gòu)化的設(shè)計(jì)來(lái)降低靜態(tài)功耗。

FPGA動(dòng)態(tài)功耗主要體現(xiàn)為存儲(chǔ)器,、內(nèi)部邏輯,、時(shí)鐘、I/O消耗的功耗。

① 選擇適當(dāng)?shù)腎/O標(biāo)準(zhǔn)可以節(jié)省功耗,。I/O功耗主要來(lái)自器件輸出引腳連接的外部負(fù)載電容,、阻抗模式輸出驅(qū)動(dòng)電路以及外部匹配網(wǎng)絡(luò)的充放電電流??蛇x擇較低的驅(qū)動(dòng)強(qiáng)度或較低的電壓標(biāo)準(zhǔn),。當(dāng)系統(tǒng)速度要求使用高功率I/O標(biāo)準(zhǔn)時(shí),可設(shè)置缺省狀態(tài)以降低功耗,。有的I/O標(biāo)準(zhǔn)需要使用上拉電阻才能正常工作,,因此如果該I/O的缺省狀態(tài)為高電平而不是低電平,就可以節(jié)省通過(guò)該終結(jié)電阻的直流功耗,。

② 當(dāng)總線上的數(shù)據(jù)與寄存器相關(guān)時(shí),,經(jīng)常使用片選或時(shí)鐘使能邏輯來(lái)控制寄存器的使能,盡早對(duì)該邏輯進(jìn)行“數(shù)據(jù)使能”,,以阻止數(shù)據(jù)總線與時(shí)鐘使能寄存器組合邏輯之間不必要的轉(zhuǎn)換,。另一種選擇是在電路板上,而不是芯片上,,進(jìn)行這種“數(shù)據(jù)使能”,,以盡可能減小處理器時(shí)鐘周期。也就是使用CPLD從處理器卸載簡(jiǎn)單任務(wù),,以便使其更長(zhǎng)時(shí)間地處于待機(jī)模式[4],。

③ 設(shè)計(jì)中所有吸收功耗的信號(hào)當(dāng)中,時(shí)鐘是罪魁禍?zhǔn)?。雖然時(shí)鐘可能運(yùn)行在 100 MHz,,但從該時(shí)鐘派生出的信號(hào)卻通常運(yùn)行在主時(shí)鐘頻率的較小分量(通常為12%~15%)。此外,,時(shí)鐘的扇出一般也比較高,。這兩個(gè)因素顯示,為了降低功耗,,應(yīng)當(dāng)認(rèn)真研究時(shí)鐘,。首先,如果設(shè)計(jì)的某個(gè)部分可以處于非活動(dòng)狀態(tài),,則可以考慮禁止時(shí)鐘樹翻轉(zhuǎn),,而不是使用時(shí)鐘使能。時(shí)鐘使能將阻止寄存器不必要的翻轉(zhuǎn),,但時(shí)鐘樹仍然會(huì)翻轉(zhuǎn),,消耗功率[4]。其次,,隔離時(shí)鐘以使用最少數(shù)量的信號(hào)區(qū),。不使用的時(shí)鐘樹信號(hào)區(qū)不會(huì)翻轉(zhuǎn),,從而減輕該時(shí)鐘網(wǎng)絡(luò)的負(fù)載。合理的布局可以在不影響實(shí)際設(shè)計(jì)的情況下達(dá)到此目標(biāo),。

④ 根據(jù)預(yù)測(cè)的下一狀態(tài)條件列舉狀態(tài)機(jī),并選擇常態(tài)之間轉(zhuǎn)換位較少的狀態(tài)值,,這樣就能盡可能減少狀態(tài)機(jī)網(wǎng)絡(luò)的轉(zhuǎn)換量(頻率),。確定常態(tài)轉(zhuǎn)換和選擇適當(dāng)?shù)臓顟B(tài)值,是降低功耗且對(duì)設(shè)計(jì)影響較小的一種簡(jiǎn)單方法,。編碼形式越簡(jiǎn)單(如1位有效編碼或格雷碼),,使用的解碼邏輯也會(huì)越少[5]。

⑤ 要計(jì)算覆蓋整個(gè)產(chǎn)品生命周期或預(yù)期電池工作時(shí)間內(nèi)所有狀態(tài)下的功耗,要考慮上電,、待機(jī),、空閑、動(dòng)態(tài)和斷電等多種狀態(tài),,要計(jì)算最壞情況下的靜態(tài)功耗,。

在所有降低功耗的措施中,選擇合適的低功耗器件起決定性的作用,,帶來(lái)的效果是立竿見(jiàn)影的,,而且無(wú)需花費(fèi)大量的時(shí)間、精力和成本采取額外的措施,。所以,,選擇一款低功耗的FPGA器件有助于提高產(chǎn)品性能,降低產(chǎn)品成本,,提高產(chǎn)品的可靠性,。下面介紹Actel公司的低功耗FPGA—— IGLOO。

2 低功耗FPGA——IGLOO

Actel公司的IGLOO源于ProASIC3系列,,保持了ProASIC3原有的所有特性:?jiǎn)涡酒?、高安全性、高可靠性,、高性能,、低功耗、低成本等,,并?duì)低功耗的特性作了加強(qiáng),。IGLOO器件采用Flash*Freeze技術(shù),能夠輕易地進(jìn)入和退出超低功耗模式,,該模式下的功耗僅 5 μW,,同時(shí)可保存SRAM和寄存器中的數(shù)據(jù)。Flash*Freeze技術(shù)通過(guò) I/O和時(shí)鐘管理簡(jiǎn)化了功率管理,,并無(wú)需關(guān)斷電壓,、I/O或系統(tǒng)層面的時(shí)鐘,,進(jìn)入和退出Flash*Freeze模式所需的時(shí)間少于1 μs。 Actel IGLOO系列以Flash可重編程技術(shù)為基礎(chǔ),,支持安全的系統(tǒng)內(nèi)可編程功能,,因此能在制造的最終階段或應(yīng)用現(xiàn)場(chǎng)快速且容易地進(jìn)行升級(jí)或設(shè)計(jì)更新[6]。

IGLOO能夠做到如此低的功耗,,主要是由以下幾個(gè)原因決定,。

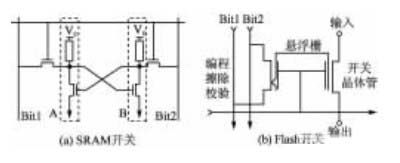

(1) 獨(dú)特的Flash開關(guān)

IGLOO采用了低功耗的Flash開關(guān),如圖2所示,。Flash開關(guān)只需要2個(gè)晶體管,,而SRAM的開關(guān)至少需要4個(gè)以上的晶體管。更少的晶體管具有更小的容性負(fù)載,、更小的漏電流,,從而具有更低的功耗。另外,,F(xiàn)lash技術(shù)的開關(guān)具有非易失性的特點(diǎn),,使得IGLOO無(wú)需配置芯片,從而較SRAM的FPGA少了上電的啟動(dòng)電流和配置電流,。一般SRAM的FPGA啟動(dòng)電流都需要幾百mA甚至幾A,,配置電流也需要幾十mA,不適合用于電池供電的系統(tǒng)[6],。

源極到漏極的泄漏電流是泄漏的主要原因。MOS管在關(guān)斷的時(shí)候,,溝道阻抗非常大,,但是只要芯片供電就必然會(huì)存在從源極到漏極的泄漏電流。隨著半導(dǎo)體工藝更加先進(jìn),,晶體管尺寸不斷減小,,溝道長(zhǎng)度也逐漸減小,使得溝道阻抗變小,,從而泄漏電流變得越來(lái)越大,,而且源極到漏極的漏電流隨溫度增加呈指數(shù)增長(zhǎng)。

(3) 動(dòng)態(tài)功耗

動(dòng)態(tài)功耗主要由電容充放電引起,,它與3個(gè)參數(shù)有關(guān):節(jié)點(diǎn)電容,、工作頻率和內(nèi)核電壓,它們與功耗成正比例關(guān)系,。如式(1)所示,節(jié)點(diǎn)電容越大,,工作頻率越高,,內(nèi)核電壓越大,其動(dòng)態(tài)功耗也就越高,。而在 FPGA中動(dòng)態(tài)功耗主要體現(xiàn)為存儲(chǔ)器,、內(nèi)部邏輯,、時(shí)鐘、I/O消耗的功耗,。在一般的設(shè)計(jì)中,,動(dòng)態(tài)功耗占據(jù)了整個(gè)系統(tǒng)功耗的90%以上,所以降低動(dòng)態(tài)功耗是降低整個(gè)系統(tǒng)功耗的關(guān)鍵因素,。

(4) 降低功耗帶來(lái)的好處

① 低功耗的器件可以實(shí)現(xiàn)更低成本的電源供電系統(tǒng),。另外,更簡(jiǎn)單的電源系統(tǒng)意味著更少的元件和更小的PCB面積,,同樣可以降低成本[3],。

② 更低的功耗引起的結(jié)溫更小,因此可以防止熱失控,,可以少用或不用散熱器,,如散熱風(fēng)扇、散熱片等,。

③ 降低功耗可以降低結(jié)溫,,而結(jié)溫的降低可以提高系統(tǒng)的可靠性。另外,,較小的風(fēng)扇或不使用風(fēng)扇可以降低EMI[3],。

④ 延長(zhǎng)器件的使用壽命。器件的工作溫度每降低10 ℃,,使用壽命延長(zhǎng)1倍,。

所以對(duì)于FPGA而言,降低功耗的根本在于直接提高了整個(gè)系統(tǒng)的性能和質(zhì)量,,并減小了體積,,降低了成本,對(duì)產(chǎn)品有著非常大的促進(jìn)作用,。

(5) 如何降低FPGA功耗

FPGA主要的功耗是由靜態(tài)功耗和動(dòng)態(tài)功耗組成,,降低FPGA的功耗就是降低靜態(tài)功耗和動(dòng)態(tài)功耗。

靜態(tài)功耗除了與工藝有關(guān)外,,與溫度也有很大的關(guān)系,。一方面需要半導(dǎo)體公司采用先進(jìn)的低功耗工藝來(lái)設(shè)計(jì)芯片,降低泄漏電流(即選擇低功耗的器件),;另一方面可以通過(guò)降低溫度,、結(jié)構(gòu)化的設(shè)計(jì)來(lái)降低靜態(tài)功耗。

FPGA動(dòng)態(tài)功耗主要體現(xiàn)為存儲(chǔ)器,、內(nèi)部邏輯,、時(shí)鐘、I/O消耗的功耗。

① 選擇適當(dāng)?shù)腎/O標(biāo)準(zhǔn)可以節(jié)省功耗,。I/O功耗主要來(lái)自器件輸出引腳連接的外部負(fù)載電容,、阻抗模式輸出驅(qū)動(dòng)電路以及外部匹配網(wǎng)絡(luò)的充放電電流??蛇x擇較低的驅(qū)動(dòng)強(qiáng)度或較低的電壓標(biāo)準(zhǔn),。當(dāng)系統(tǒng)速度要求使用高功率I/O標(biāo)準(zhǔn)時(shí),可設(shè)置缺省狀態(tài)以降低功耗,。有的I/O標(biāo)準(zhǔn)需要使用上拉電阻才能正常工作,,因此如果該I/O的缺省狀態(tài)為高電平而不是低電平,就可以節(jié)省通過(guò)該終結(jié)電阻的直流功耗,。

② 當(dāng)總線上的數(shù)據(jù)與寄存器相關(guān)時(shí),,經(jīng)常使用片選或時(shí)鐘使能邏輯來(lái)控制寄存器的使能,盡早對(duì)該邏輯進(jìn)行“數(shù)據(jù)使能”,,以阻止數(shù)據(jù)總線與時(shí)鐘使能寄存器組合邏輯之間不必要的轉(zhuǎn)換,。另一種選擇是在電路板上,而不是芯片上,,進(jìn)行這種“數(shù)據(jù)使能”,,以盡可能減小處理器時(shí)鐘周期。也就是使用CPLD從處理器卸載簡(jiǎn)單任務(wù),,以便使其更長(zhǎng)時(shí)間地處于待機(jī)模式[4],。

③ 設(shè)計(jì)中所有吸收功耗的信號(hào)當(dāng)中,時(shí)鐘是罪魁禍?zhǔn)?。雖然時(shí)鐘可能運(yùn)行在 100 MHz,,但從該時(shí)鐘派生出的信號(hào)卻通常運(yùn)行在主時(shí)鐘頻率的較小分量(通常為12%~15%)。此外,,時(shí)鐘的扇出一般也比較高,。這兩個(gè)因素顯示,為了降低功耗,,應(yīng)當(dāng)認(rèn)真研究時(shí)鐘,。首先,如果設(shè)計(jì)的某個(gè)部分可以處于非活動(dòng)狀態(tài),,則可以考慮禁止時(shí)鐘樹翻轉(zhuǎn),,而不是使用時(shí)鐘使能。時(shí)鐘使能將阻止寄存器不必要的翻轉(zhuǎn),,但時(shí)鐘樹仍然會(huì)翻轉(zhuǎn),,消耗功率[4]。其次,,隔離時(shí)鐘以使用最少數(shù)量的信號(hào)區(qū),。不使用的時(shí)鐘樹信號(hào)區(qū)不會(huì)翻轉(zhuǎn),,從而減輕該時(shí)鐘網(wǎng)絡(luò)的負(fù)載。合理的布局可以在不影響實(shí)際設(shè)計(jì)的情況下達(dá)到此目標(biāo),。

④ 根據(jù)預(yù)測(cè)的下一狀態(tài)條件列舉狀態(tài)機(jī),并選擇常態(tài)之間轉(zhuǎn)換位較少的狀態(tài)值,,這樣就能盡可能減少狀態(tài)機(jī)網(wǎng)絡(luò)的轉(zhuǎn)換量(頻率),。確定常態(tài)轉(zhuǎn)換和選擇適當(dāng)?shù)臓顟B(tài)值,是降低功耗且對(duì)設(shè)計(jì)影響較小的一種簡(jiǎn)單方法,。編碼形式越簡(jiǎn)單(如1位有效編碼或格雷碼),,使用的解碼邏輯也會(huì)越少[5]。

⑤ 要計(jì)算覆蓋整個(gè)產(chǎn)品生命周期或預(yù)期電池工作時(shí)間內(nèi)所有狀態(tài)下的功耗,要考慮上電,、待機(jī),、空閑、動(dòng)態(tài)和斷電等多種狀態(tài),,要計(jì)算最壞情況下的靜態(tài)功耗,。

在所有降低功耗的措施中,選擇合適的低功耗器件起決定性的作用,,帶來(lái)的效果是立竿見(jiàn)影的,,而且無(wú)需花費(fèi)大量的時(shí)間、精力和成本采取額外的措施,。所以,,選擇一款低功耗的FPGA器件有助于提高產(chǎn)品性能,降低產(chǎn)品成本,,提高產(chǎn)品的可靠性,。下面介紹Actel公司的低功耗FPGA—— IGLOO。

2 低功耗FPGA——IGLOO

Actel公司的IGLOO源于ProASIC3系列,,保持了ProASIC3原有的所有特性:?jiǎn)涡酒?、高安全性、高可靠性,、高性能,、低功耗、低成本等,,并?duì)低功耗的特性作了加強(qiáng),。IGLOO器件采用Flash*Freeze技術(shù),能夠輕易地進(jìn)入和退出超低功耗模式,,該模式下的功耗僅 5 μW,,同時(shí)可保存SRAM和寄存器中的數(shù)據(jù)。Flash*Freeze技術(shù)通過(guò) I/O和時(shí)鐘管理簡(jiǎn)化了功率管理,,并無(wú)需關(guān)斷電壓,、I/O或系統(tǒng)層面的時(shí)鐘,,進(jìn)入和退出Flash*Freeze模式所需的時(shí)間少于1 μs。 Actel IGLOO系列以Flash可重編程技術(shù)為基礎(chǔ),,支持安全的系統(tǒng)內(nèi)可編程功能,,因此能在制造的最終階段或應(yīng)用現(xiàn)場(chǎng)快速且容易地進(jìn)行升級(jí)或設(shè)計(jì)更新[6]。

IGLOO能夠做到如此低的功耗,,主要是由以下幾個(gè)原因決定,。

(1) 獨(dú)特的Flash開關(guān)

IGLOO采用了低功耗的Flash開關(guān),如圖2所示,。Flash開關(guān)只需要2個(gè)晶體管,,而SRAM的開關(guān)至少需要4個(gè)以上的晶體管。更少的晶體管具有更小的容性負(fù)載,、更小的漏電流,,從而具有更低的功耗。另外,,F(xiàn)lash技術(shù)的開關(guān)具有非易失性的特點(diǎn),,使得IGLOO無(wú)需配置芯片,從而較SRAM的FPGA少了上電的啟動(dòng)電流和配置電流,。一般SRAM的FPGA啟動(dòng)電流都需要幾百mA甚至幾A,,配置電流也需要幾十mA,不適合用于電池供電的系統(tǒng)[6],。

圖2 Flash開關(guān)和SRAM開關(guān)的對(duì)比

(2) 更低的內(nèi)核電壓

IGLOO的內(nèi)核可以支持1.2 V或1.5 V供電,,1.2 V的內(nèi)核電壓比1.5 V的內(nèi)核電壓可以節(jié)省36%的動(dòng)態(tài)功耗??捎墒剑?)推導(dǎo)出來(lái),,動(dòng)態(tài)功耗與內(nèi)核電壓的平方成正比,所以1.2 V的IGLOO系統(tǒng)比1.5 V內(nèi)核電壓的系統(tǒng)可以節(jié)省更多的功耗,。

(3) 低功耗的Flash*Freeze模式

IGLOO具有一種獨(dú)特的Flash*Freeze模式,。在這種模式下可以讓FPGA進(jìn)入睡眠狀態(tài)。在這種模式下最低的功耗可達(dá) 2 μW(IGLOO的Nano系列),,并且能夠保存RAM和寄存器的狀態(tài),。進(jìn)入和退出這種模式只需要通過(guò)FPGA的Flash*Freeze引腳控制即可,進(jìn)入和退出只需要1 μs,,非常方便,。

(4) 具有低功耗布局布線工具

Actel提供免費(fèi)的開發(fā)環(huán)境——Libero,并充分考慮了低功耗的設(shè)計(jì),,在軟件中增加了功耗驅(qū)動(dòng)的布局布線,。在該方式的驅(qū)動(dòng)下,軟件自動(dòng)以最低功耗的方式來(lái)布局并走線,,類似于PCB繪制時(shí)的布局與走線,。其中影響最大的是時(shí)鐘的走線,,因?yàn)樵诖蟛糠值脑O(shè)計(jì)中時(shí)鐘對(duì)功耗起了關(guān)鍵性的影響。經(jīng)過(guò)功耗驅(qū)動(dòng)的布局布線以后,,時(shí)鐘走線變得更有規(guī)則,,連線也盡量短,從而大大降低了功耗,,通過(guò)該方式最多可以節(jié)省30%的功耗,。

另外,在Libero軟件內(nèi)部集成的Modelsim仿真軟件中,,提供了功率估算工具。它用于分析實(shí)際器件利用率,,并結(jié)合實(shí)際的適配后仿真數(shù)據(jù),,給出實(shí)際功耗數(shù)據(jù),可以在完全不接觸芯片的情況下分析設(shè)計(jì)改變對(duì)總功耗的影響,。

3 小結(jié)

通過(guò)上面的分析,了解了FPGA功率損耗的相關(guān)原理和影響功耗的相關(guān)因素,。設(shè)計(jì)者通過(guò)優(yōu)化自己的設(shè)計(jì)和注意某些具體情況,可以在FPGA設(shè)計(jì)中實(shí)現(xiàn)低功耗。通過(guò)一款具體的FPGA產(chǎn)品了解其低功耗的解決方式,,為設(shè)計(jì)提供了指導(dǎo),。FPGA均可在相應(yīng)的操作環(huán)境下進(jìn)行仿真,從而了解功耗的具體使用情況,,針對(duì)相應(yīng)的情況進(jìn)行修改,。另外,還可采用優(yōu)化的算法來(lái)減少多余和無(wú)意義的開關(guān)活動(dòng),,來(lái)實(shí)現(xiàn)低功耗的解決方案,。

(2) 更低的內(nèi)核電壓

IGLOO的內(nèi)核可以支持1.2 V或1.5 V供電,,1.2 V的內(nèi)核電壓比1.5 V的內(nèi)核電壓可以節(jié)省36%的動(dòng)態(tài)功耗??捎墒剑?)推導(dǎo)出來(lái),,動(dòng)態(tài)功耗與內(nèi)核電壓的平方成正比,所以1.2 V的IGLOO系統(tǒng)比1.5 V內(nèi)核電壓的系統(tǒng)可以節(jié)省更多的功耗,。

(3) 低功耗的Flash*Freeze模式

IGLOO具有一種獨(dú)特的Flash*Freeze模式,。在這種模式下可以讓FPGA進(jìn)入睡眠狀態(tài)。在這種模式下最低的功耗可達(dá) 2 μW(IGLOO的Nano系列),,并且能夠保存RAM和寄存器的狀態(tài),。進(jìn)入和退出這種模式只需要通過(guò)FPGA的Flash*Freeze引腳控制即可,進(jìn)入和退出只需要1 μs,,非常方便,。

(4) 具有低功耗布局布線工具

Actel提供免費(fèi)的開發(fā)環(huán)境——Libero,并充分考慮了低功耗的設(shè)計(jì),,在軟件中增加了功耗驅(qū)動(dòng)的布局布線,。在該方式的驅(qū)動(dòng)下,軟件自動(dòng)以最低功耗的方式來(lái)布局并走線,,類似于PCB繪制時(shí)的布局與走線,。其中影響最大的是時(shí)鐘的走線,,因?yàn)樵诖蟛糠值脑O(shè)計(jì)中時(shí)鐘對(duì)功耗起了關(guān)鍵性的影響。經(jīng)過(guò)功耗驅(qū)動(dòng)的布局布線以后,,時(shí)鐘走線變得更有規(guī)則,,連線也盡量短,從而大大降低了功耗,,通過(guò)該方式最多可以節(jié)省30%的功耗,。

另外,在Libero軟件內(nèi)部集成的Modelsim仿真軟件中,,提供了功率估算工具。它用于分析實(shí)際器件利用率,,并結(jié)合實(shí)際的適配后仿真數(shù)據(jù),,給出實(shí)際功耗數(shù)據(jù),可以在完全不接觸芯片的情況下分析設(shè)計(jì)改變對(duì)總功耗的影響,。

3 小結(jié)

通過(guò)上面的分析,了解了FPGA功率損耗的相關(guān)原理和影響功耗的相關(guān)因素,。設(shè)計(jì)者通過(guò)優(yōu)化自己的設(shè)計(jì)和注意某些具體情況,可以在FPGA設(shè)計(jì)中實(shí)現(xiàn)低功耗。通過(guò)一款具體的FPGA產(chǎn)品了解其低功耗的解決方式,,為設(shè)計(jì)提供了指導(dǎo),。FPGA均可在相應(yīng)的操作環(huán)境下進(jìn)行仿真,從而了解功耗的具體使用情況,,針對(duì)相應(yīng)的情況進(jìn)行修改,。另外,還可采用優(yōu)化的算法來(lái)減少多余和無(wú)意義的開關(guān)活動(dòng),,來(lái)實(shí)現(xiàn)低功耗的解決方案,。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載,。