0 引言

運算放大器是數(shù)據(jù)采樣電路中的關(guān)鍵部分,如流水線模數(shù)轉(zhuǎn)換器等。在此類設(shè)計中,速度和精度是兩個重要因素,而這兩方面的因素都是由運放的各種性能來決定的。

本文設(shè)計的帶共模反饋的兩級高增益運算放大器結(jié)構(gòu)分兩級,第一級為套筒式運算放大器,用以達到高增益的目的;第二級采用共源級電路結(jié)構(gòu),以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。該方案不僅從理論上可滿足高增益、高共模抑制比的要求,而且通過了軟件仿真驗證。結(jié)果顯示,該結(jié)構(gòu)的直流增益可達到80 dB,相位裕度達到80°,增益帶寬為74 MHz。

1 運放結(jié)構(gòu)

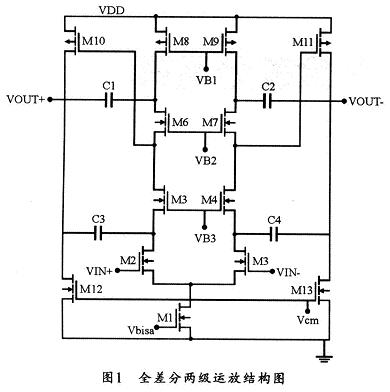

通常所用的運算放大器的結(jié)構(gòu)基本有三種,即簡單兩級運放、折疊共源共柵和套筒式共源共柵。其中兩級結(jié)構(gòu)有大的輸出擺幅,但是頻率特性比較差,一般用米勒補償,可使得相位裕度變小,因而電路的穩(wěn)定性會變差;套筒式的共源共柵結(jié)構(gòu),雖然頻率特性較好,又因為它只有兩條主支路,所以功耗比較小。但是這些都是以減小輸入范圍和輸出擺幅為代價的。因此,為了緩解套筒式結(jié)構(gòu)對輸入電壓范圍的限制,本文提出了折疊式運算放大器結(jié)構(gòu)的思路。折疊式結(jié)構(gòu)比套筒式結(jié)構(gòu)有更大的輸入共模電平范圍,但卻以減小增益和帶寬,增大噪聲和功耗為代價的。考慮到折疊共源共柵輸入級結(jié)構(gòu)的功耗比較大,因此,本文選擇套筒式共源共柵結(jié)構(gòu)作為輸入級,最后選擇了如圖1所示的全差分結(jié)構(gòu)的兩級運放結(jié)構(gòu)。

1.1 主運放結(jié)構(gòu)

全差分運算放大電路對環(huán)境噪聲具有更強的抑制能力。而套筒式結(jié)構(gòu)則具有高增益、低功耗以及頻率特性好等特點。因此,第一級放大結(jié)構(gòu)(即M0~M8)采用套筒式全差分放大器結(jié)構(gòu)作為輸入級。第二級(即M9~M11)為共源結(jié)構(gòu),以改善套筒式結(jié)構(gòu)輸出擺幅小的缺點,同時相應(yīng)提高運算放大器的開環(huán)增益。但是,隨著級數(shù)的增加,必然會增加電路的零極點,這對系統(tǒng)穩(wěn)定性的要求更高。因此,必須引入補償電容C3來補償額外的極點,使電路的相位裕度能滿足要求,并使性能穩(wěn)定。另外,圖1申的VB1用于提供尾電流鏡偏置,VB2和VB3分別用于為PMOS和NMOS提供靜態(tài)直流偏置,這三個偏置電壓均提供有偏置電路。

對該運算放大器進行小信號分析,可以計算出第一級套筒式全差分結(jié)構(gòu)的放大倍AV1,公式為:

A v1≈g2[(gm4τ2τ4)·(gm6τ6τs)]

其中,gm2、gm4、gm6分別表示M2、M4、M6的跨導(dǎo),r2、r4、r6、r8分別表示M2、M4、M6、M8管的輸出電阻。

第二級共源級放大結(jié)構(gòu)的單端放大倍AV2可用下式計算:

AV2=-gM10r10

其中,gM10、r10分別表示M10管的跨導(dǎo)和輸出電阻。因此,整個米勒補償型運算放大器的開環(huán)增益A v可以用第一級和第二級的放大倍數(shù)之積來表示:

A v="A" v1A v2

1.2 共模反饋電路

由于本設(shè)計采用的是全差分結(jié)構(gòu),所以,為了通過穩(wěn)定直流來穩(wěn)定輸出共模電壓,保證輸出級工作于線性區(qū),通常需要一個共模反饋(CMFB" title="CMFB">CMFB)電路。共模反饋電路一般有兩種類型。一種為連續(xù)時間式,另一種為開關(guān)電容式。本設(shè)計采用的是開關(guān)電容式結(jié)構(gòu),圖2所示是開關(guān)電容式共模反饋電路。其中S1~S6為開關(guān),C1~C4是共模反饋電容,Vout+和Vout-是運放的輸出電壓,ψ1和ψ2是兩相不交疊的時鐘信號。VCM是理想共模輸出電壓,Vb1是理想的共模偏置電壓,Vb2是實際的共模偏置電壓,即運放中電流源的控制電壓。實際中,S1~S6的開關(guān)都是由NMOS管實現(xiàn)的。

1.3 偏置電路

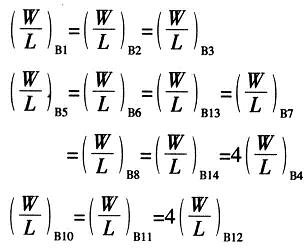

偏置電路主要用于提供折疊共源共柵放大器及共模反饋的偏置電壓。本文采用如圖3所示的寬擺幅電流源偏置電路結(jié)構(gòu)。在共源共柵輸入級中,通常需要三個電壓偏置。為了使輸入級的動態(tài)范圍大一些,圖3中的寬擺幅電流源用來產(chǎn)生所需要的三個偏置電壓。根據(jù)寬擺幅電流源的設(shè)計要求,設(shè)計時必須滿足以下關(guān)系式:

2 電路仿真結(jié)果

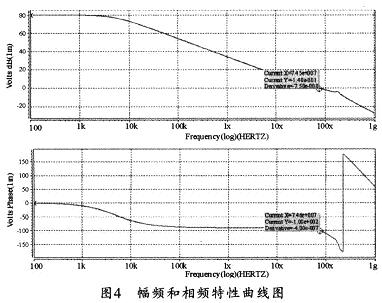

采用HSPICE電路仿真工具,并利用上華0.6μm CMOS" title="CMOS">CMOS工藝模型參數(shù),可對電路進行仿真,仿真結(jié)果顯示:該運放的開環(huán)直流增益為80 dB,相位裕度80度,單位增益帶寬74 MHz。圖4為其幅頻及相頻特性曲線。由圖4可見,電路功耗為1.9 mW;差動輸出范圍為-2.48~2.5 V;電源電壓為2.5 V。

3 結(jié)束語

本文給出了一種低電壓全差分套筒式運算放大器的設(shè)計方法,同時對該設(shè)計方法進行了仿真,從仿真結(jié)果可以看出,在保證高增益、低功耗的同時,該設(shè)計還可以滿足20 MHz流水線模數(shù)轉(zhuǎn)換器中運放的設(shè)計要求。