便攜式無(wú)線(xiàn)接收機(jī)的主要挑戰(zhàn)是在降低功耗的同時(shí),使其動(dòng)態(tài)范圍最大化。帶有一對(duì)時(shí)間連續(xù),低通模數(shù)轉(zhuǎn)換器(ADC)的直接變頻接收機(jī)的功耗很低,但是它也容易造成諸如正交性不很好、DC偏移和低頻失真等問(wèn)題,從而限制了產(chǎn)品的動(dòng)態(tài)范圍。另一方面,一個(gè)二次變頻超外差接收機(jī)就沒(méi)有這些限制,但通常由于其復(fù)雜性增加,以及需要對(duì)較高的中頻(IF)信號(hào)進(jìn)行數(shù)字化,它的耗電量相對(duì)增大。本文介紹了一種頻率范圍在10~300MHz,帶寬 333KHz,動(dòng)態(tài)范圍為90dB的混頻器和時(shí)間連續(xù)帶通SD ADC組件。電路的耗電量為50mW,這說(shuō)明低功耗高性能的二次變頻超外差式接收機(jī)是可以實(shí)現(xiàn)的。

圖1對(duì)

圖2

圖1對(duì)將一個(gè)中頻信號(hào)進(jìn)行數(shù)字化的兩種方法進(jìn)行對(duì)比。第一種方法需要幾種大功率的模塊,即,可變?cè)鲆娣糯笃?VGA),抗混疊濾波器(AAF)和ADC,而第二種方法將此模塊用一個(gè)帶LC諧振電路的帶通SD ADC所替代。借助時(shí)間連續(xù)環(huán)路濾波器,帶通SD ADC對(duì)固有混疊進(jìn)行保護(hù),省去了AAF。由于ADC的輸入噪聲較低,且它的電流型輸入能提供較強(qiáng)的信號(hào),所以它的動(dòng)態(tài)范圍較寬,因此,

也省去了VGA。通過(guò)將這兩個(gè)高耗電模塊納入到ADC中,第二種簡(jiǎn)單的拓?fù)浣Y(jié)構(gòu)具有節(jié)電優(yōu)勢(shì)。

圖2是較詳細(xì)的ADC結(jié)構(gòu)。鑒于上述討論,低噪放(LNA)加混頻器的跨導(dǎo)視為gm=10mA/V。低噪放加混頻器的輸出電流2mApp直接作為ADC的輸入,而沒(méi)有經(jīng)過(guò)不必要的I-V或V-I轉(zhuǎn)換。8個(gè)元件的電流型DAC(IDAC)的電流減去反饋數(shù)字輸出電流,生成一個(gè)驅(qū)動(dòng)LC諧振電路的誤差電流。LC諧振電路由兩個(gè)外部5.6mH的電感和一個(gè)電容組成。通過(guò)一個(gè)9位片上電容陣列將電容值微調(diào)到所需值的1%以?xún)?nèi)。LC諧振電路在相關(guān)頻帶內(nèi)的有效阻抗為Z=6KW,此阻抗將造成12VPP的電壓擺動(dòng),如果不是來(lái)自于IDAC的反饋,IDAC的反饋只能導(dǎo)致以下的電壓擺動(dòng)。前端電路較大的有效增益為gmZ=60,當(dāng)?shù)驮敕庞休斎胄盘?hào)時(shí),會(huì)使ADC后端的噪聲由減少到只有。由于此噪聲比低噪放/混頻器的輸入噪聲低8dB,因此,ADC的后端對(duì)IC噪聲特性的影響不大。由于LC諧振電路不產(chǎn)生噪聲,加之無(wú)失真和不耗電,因此,LC諧振電路是帶通SD ADC中理想的第一諧振器。

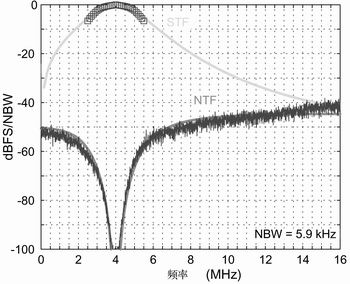

圖3

VGA通常用于當(dāng)信號(hào)較弱時(shí),通過(guò)增益來(lái)降低ADC的輸入噪聲。但是,圖2中的VGA是ADC的一個(gè)內(nèi)部元件,它的主要目的是當(dāng)信號(hào)較弱時(shí)降低功率消耗。為了平衡大信號(hào)的電流,IDAC元件的總電流必須為2mA,但是當(dāng)信號(hào)較弱時(shí),元件的電流可以降低(本方案中降低了1/4),以節(jié)省功耗。全面地改變IADC可以相應(yīng)地改變ADC,使AGC功能得以實(shí)現(xiàn)。全面地降低IDAC可以減小ADC后端的信號(hào)擺動(dòng),并且利用圖中的可變?cè)鲆嬖闺娐返玫阶钣行У难a(bǔ)償。為了保持調(diào)制器的動(dòng)態(tài)范圍,VGA的增益會(huì)隨IDAC的全面波動(dòng)而反向變動(dòng)。VGA作為一個(gè)其gm值可變的模塊,通過(guò)改變非退化雙極結(jié)型晶體管(BJT)差分對(duì)中的拖尾電流來(lái)控制。

ADC的第二個(gè)諧振器也使用了一個(gè)LC諧振電路。圖3中的VGA和有源RC諧振器消耗2mA的電流,并且不需外部元件就能滿(mǎn)足第二級(jí)動(dòng)態(tài)范圍的要求。可編程電容陣列可以實(shí)現(xiàn)RC諧振器的調(diào)諧。