摘 要:二進制翻譯技術是代碼移植技術中的一種重要技術。針對二進制翻譯的應用,提出在ARM嵌入式平臺下實現(xiàn)X86 t0 ARM二進制翻譯系統(tǒng)。通過對ARM嵌入式平臺的研究,介紹二進制翻譯模塊的功能,著重論述SOC架構的設計,并分析Multi-layer總線結構的特點及優(yōu)化。該SOC系統(tǒng)實現(xiàn)了將部分X86指令翻譯為ARM指令并由ARM處理器執(zhí)行目標代碼的功能。該設計為在硬件上實現(xiàn)二進制翻譯提供了參考。

關鍵詞:ARM;嵌入式;二進制翻譯;SoC

二進制翻譯也是一種編譯技術,它與傳統(tǒng)編譯器的差別在于其編譯處理對象不同。傳統(tǒng)編譯器處理的是某一種高級語言,經(jīng)過編譯處理生成某種機器的目標代碼。

二進制翻譯是一種直接翻譯可執(zhí)行二進制程序的技術,能夠把一種處理器上的二進制程序翻譯到另外一種處理器上執(zhí)行。它使得不同處理器之間的二進制程序可以很容易的相互移植,擴大了硬件/軟件的適用范圍,有助于打破處理器和支持軟件之間的相互扼制的局面。二進制翻譯技術的優(yōu)點為:不需要重編譯源碼就可以實現(xiàn)軟件從舊平臺到新平臺的移植;快速為新機器提供軟件,包括移植操作系統(tǒng)和編譯器;充分利用新機器的特性優(yōu)化代碼;減少培訓費用,因為使用的是相同的軟件,所以不必在新平臺上重新培訓員工;降低了多平臺軟件的費用。

1 SOC架構設計

1.1 處理器的確定

通用處理器與硬件邏輯是SoC設計的主流架構。在一些需要大量數(shù)據(jù)處理的應用中,這樣的架構并不能滿足要求。實際上,由于不同的任務在很大程度上互相獨立運行,可以將具有內在執(zhí)行并行性的任務分解為緊密聯(lián)系的子任務,不同的內核可以執(zhí)行不同的子任務,多核架構在1個周期內可以執(zhí)行多個指令。這種并行處理使得整個系統(tǒng)的性能與使用單核處理器串行處理相同任務相比,有了很大改進。另外,多核架構設計可以復用現(xiàn)有的單核處理器作為處理器核心,從而可以縮短設計和驗證周期,節(jié)省開發(fā)成本,符合SoC設計的基本思路。多核架構是未來SoC發(fā)展的一個趨勢。

該設計采用雙核架構,采用當代流行的處理能力較好的ARM處理器ARM7TDMI-S和ARM926EJ-S,ARM內核最大的優(yōu)勢在于高速度、低功耗。

ARM7TDMl-s具有3級流水線結構,支持Win-dows CE,Linux等操作系統(tǒng)。ARM926EJ-S是ARM公司在2000年推出的功能最強大的ARM9處理器,實現(xiàn)5級流水,它與外部通信接口為雙AHB總線結構,即指令AHB總線和數(shù)據(jù)AHB總線。該設計中ARMTDMI-S主要負責控制、操作系統(tǒng)平臺和任務的調度。ARM926EJ-S則主要負責各種任務的執(zhí)行。

1.2 使用的總線標準

由于SoC中集成了大量的IP核,設計的關鍵在于如何實現(xiàn)各IP模塊之間的互連。目前,SoC中IP核的互連一般采用總線結構,通過消息通信。

采用ARM公司的AHB與APB為片上總線。AMBA總線體系結構是當前SoC體系設計結構設計的開放標準,由于AMBA被越來越多的公司采用,已迅速成為SoC結構和IP庫開發(fā)的標準。

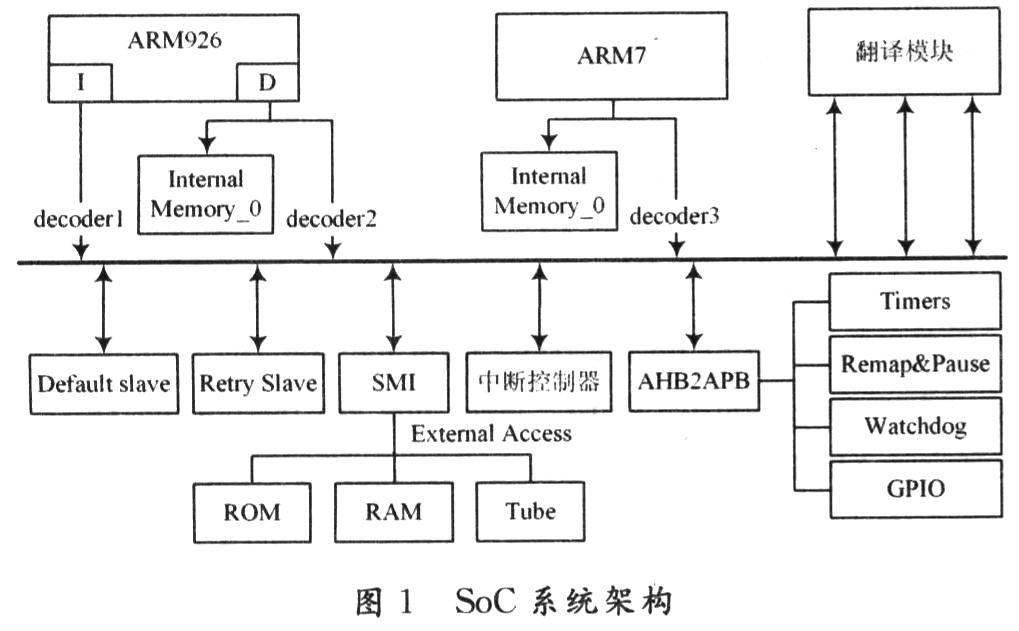

在具體實現(xiàn)時,采用AHB加APB的兩級總線結構。AHB用來支持高速設備,支持多主從設備。多個主設備之間通過仲裁機制保證優(yōu)先級,從設備通過地址譯碼機制被選中,并響應主設備發(fā)起的總線事務。APB用支持基于寄存器訪問的低速設備。AHB與APB兩條總線通過總線橋連接在一起,實現(xiàn)兩條總線之間的協(xié)議轉換。圖1為SoC的系統(tǒng)結構框圖。

1.3 各IP在系統(tǒng)中的功能

除了兩個處理器外,SoC中各IP核功能如下:翻譯模塊:實現(xiàn)將X86指令翻譯成為ARM指令的功能。

SMI:外部存儲與微處理器之間的橋梁,支持RoM作為系統(tǒng)的非易失性存儲介質,支持片外SRAM作為系統(tǒng)的外圍高速存儲。

中斷控制器:用來支持系統(tǒng)內部與外部的中斷控制,如中斷電平/邊沿觸發(fā)、中斷電平極性與中斷使能等。

Internal Memory:片內SRAM,大小為1 KB,但可以通過修改Verilog的描述來改變其大小。

Default Slave:用于當master訪問未定義的地址空間時,給出一個應答信號。

Retry Slave:是一個可以產(chǎn)生重試回應及等待命令的slave范例,若需要類似的模組,可以利用它來完成。

Watchdog:保證系統(tǒng)安全的監(jiān)控模塊,軟件需在預定的時間內訪問相應的寄存器,否則硬件將產(chǎn)生內部信號自動復位。

GPIO控制器:用來支持擴展外設,拓寬SoC的使用范圍。

Remap&Pause:主要分成兩個處理單元,前者負責控管地址是否重新對應的機制,后者負責管理系統(tǒng)的省電模式。

Timer:定時器,支持捕獲、Matchout輸出、外部時鐘驅動。

2 X86到ARM二進制翻譯模塊

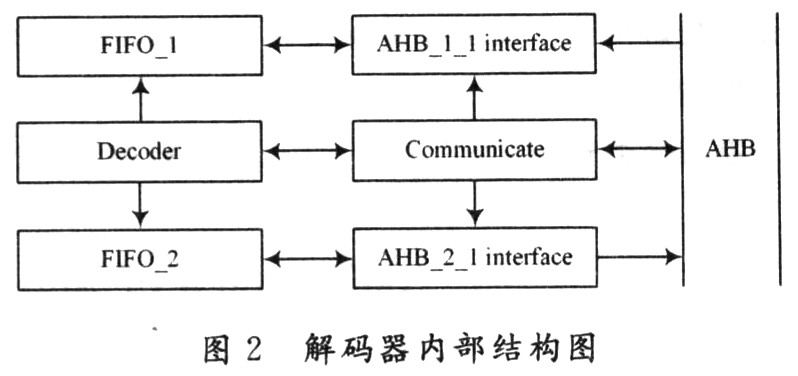

該設計使用的翻譯模塊通過編寫Verilog HDL實現(xiàn),能將部分X86指令翻譯成ARM指令,實現(xiàn)了某些X86應用程序到ARM架構的移植。圖2為解碼器內部結構圖。

該翻譯模塊首先從ROM中取出X86指令,翻譯成ARM指令后存人RAM中,所有指令翻譯完成后,翻譯模塊產(chǎn)生一個終端,使處理器執(zhí)行RAM中的指令。即所有指令先翻譯完成,處理器才執(zhí)行,該翻譯過程屬于靜態(tài)二進制翻譯。其中Decoder是整個解碼模塊的核心,負責翻譯指令。Decoder模塊采用有限狀態(tài)機控制數(shù)據(jù)通路的方式實現(xiàn).根據(jù)指令的功能和尋址方式進行狀態(tài)分類,然后輸出ARM指令。例如,把寄存器尋址的算術指令可分為一類:

ADD EAX,EBX

SUB EAX,EBX

因為這些指令的尋址方式一樣,功能近似,只是操作碼不一樣,可以歸并為一個狀態(tài),在某一狀態(tài)內建立映射關系翻譯成為ARM指令。

考慮到AHB總線可能處于比較忙碌的狀態(tài),對于X86指令和翻譯出的ARM指令分別設置2個FIFO。FIFO1和FIFO2各自有2個存儲器,其中一個存儲指令,另一個存儲與指令對應的地址。對FIFO進行操作會同時對指令和地址進行操作,以保持指令和地址的對應。

此外,ARM核需要向解碼模塊發(fā)送信號,通過設置Communicate模塊中的寄存器控制指令譯碼器的工作:

設置X86指令的起始地址;設置X86指令的終止地址;設置ARM指令的初始存放地址;設置ARM指令復雜指令段的初始地址;設置使指令解碼器開始工作的標志寄存器,高電平表示工作;判斷指令解碼是否結束,結束后向ARM核發(fā)送中斷;ARM核接收中斷信號后,將標志寄存器置低,翻譯模塊結束本次工作。

本文的SoC系統(tǒng)中沒有使用DMA對X86指令和ARM指令進行存取,而是由翻譯模塊主動進行讀和寫。因而有2個Master總線接口,通過AHB _1_1interface讀取X86指令,由AHB_2_1 interface將ARM指令寫入RAM中。Communicate模塊與總線的通信接口為Slave口,用于接收ARM核發(fā)送的4個地址,一旦接收到這4個地址,翻譯模塊中的start_flag信號置高,表示開始工作。

3 片上總線結構

在ARM SoC體系結構中,有Master和Slave這兩個重要的概念。Master是ARM SoC體系結構中的主單元,他可以向總線發(fā)出請求并且對傳輸進行初始化,例如對存儲器進行讀/寫操作,典型的Master可以是CPU,DSP,DMA。Slave是ARM SoC體系結構中的從單元,典型的Slave為片上或者片外存儲器,它們都有自己惟一的地址范圍。Master發(fā)起讀/寫操作時,在初始化中會給出讀/寫操作的地址,而地址譯碼器則根據(jù)這個地址決定哪個Slave被Master選中,然后相應的Slave做出相應。

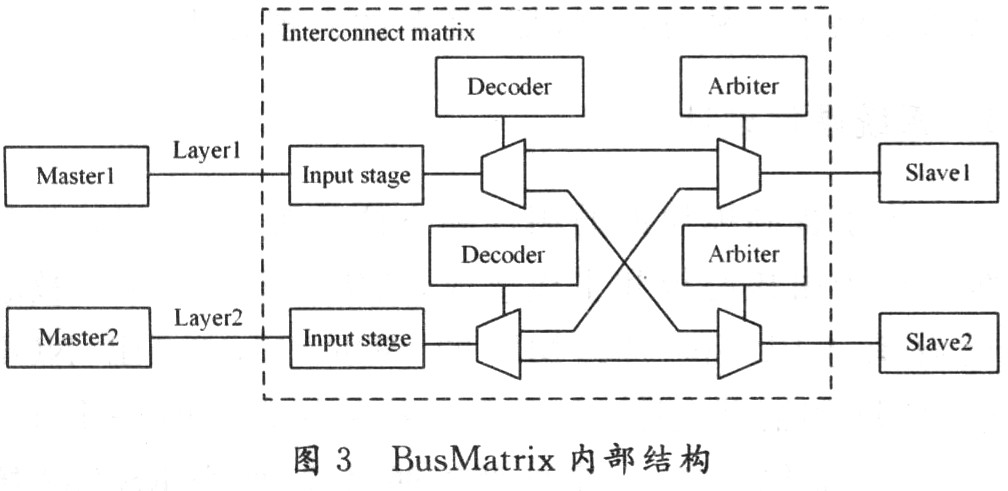

在AHB系統(tǒng)中,若有2個Master常需要AccessBus,則系統(tǒng)的Performance必定會下降。為了解決這個問題。ARM提出了Multi-layer AHB,其基本構想是2個Master走不同的Bus去訪問Slave,如果訪問的Slave不同,則兩個Master可以同步的進行Transfer。若彼此訪問一個Slave,則根據(jù)優(yōu)先級去判斷要先處理誰的Transfer。

該總線結構使用了Multi_layerbus switch(BusMatrix)模塊。AHB BusMatrix的設計可以分為3個部分:輸入級、譯碼級和輸出級。圖3為該設計所使用的結構,其中,輸入和輸出的個數(shù)可以根據(jù)系統(tǒng)的Master和Slave靈活調整。

可以看出,每個Layer都有一個譯碼器來決定Master要訪問哪一個Slave,通過多路選擇器實Master和Slave之間的Transfer。。每個Slave口都有自己的仲裁器,該仲裁器使用固定優(yōu)先級,最高優(yōu)先級的Layer可以優(yōu)先訪問對應的Slave。

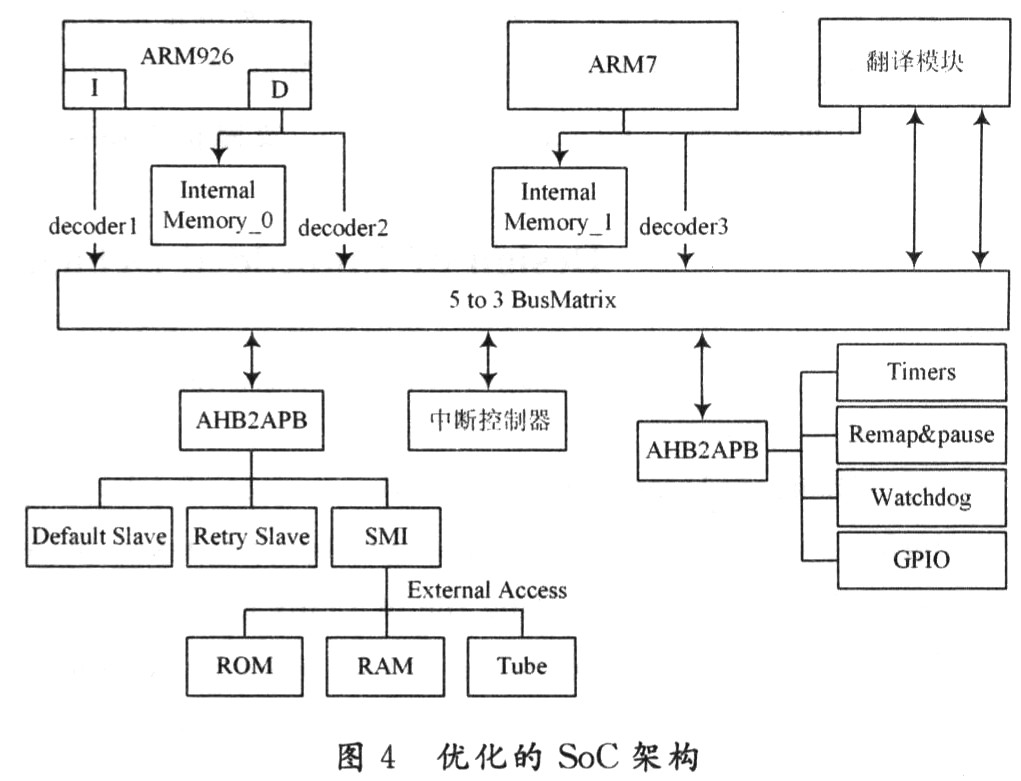

隨著系統(tǒng)中Master和Slave的增多,Busmatrix模塊的復雜度也會明顯增加,如果按照系統(tǒng)所有的Mas-ter和Slave的個數(shù)來確定輸入/輸出口的個數(shù),Busma-trix將會非常復雜,因此對系統(tǒng)結構進行優(yōu)化變得非常必要。根據(jù)系統(tǒng)工作情況可以發(fā)現(xiàn),翻譯模塊的Slave端口僅被ARM7核訪問,即向翻譯模塊存取指令所需的地址,控制其工作,該Slave可以看作是ARM7核私有的,而不被其他Master訪問。有些Slave只有在特殊情況下才被訪問,因此可以將多個Slave看作一個Slave掛在BusMatrix上。優(yōu)化后的SoC硬件架構如圖4所示。

4 結 語

這里給出了一種具有X86到ARM二進制翻譯和執(zhí)行功能的SoC系統(tǒng)。利用Multi-layer bus SWitch(BusMatrix)模塊實現(xiàn)Multi-layer。總線結構,在多個核不訪問同一個Slave時,可以同時執(zhí)行各自功能,有效提高系統(tǒng)的性能,且該總線結構的可擴展性強。同時根據(jù)系統(tǒng)工作的特點,對總線結構進行了優(yōu)化,減小了總線的復雜度。