1引言

IEEE1394是一種高速串行總線,它最初是由Apple公司與20世紀80年代中期開發(fā)的FireWire總線。1995年,IEEE制定并頒布了IEEE 1394-1995標準,并在2000年推出了IEEE 1394a標準,可以支持100Mbps、200Mbps和400Mbps的傳輸速率。在最新的IEEE1394B標準中,支持的傳輸速率提高到了800Mbps、1.6Gbps和3.2Gbps。IEEE1394總線以其高傳輸速率的特點已經(jīng)在視頻傳輸、網(wǎng)絡互聯(lián)及計算機外設等領域有了廣泛的應用[1]。目前在航空[2]及航天應用中對大量數(shù)據(jù)的高速實時傳輸要求不斷提高,IEEE1394具有數(shù)據(jù)傳輸速率高、支持等時傳輸?shù)忍攸c,因而成為未來星載數(shù)據(jù)總線的選擇之一。

在星載應用中,由于任務的多樣性,對星載總線接口的需求多種多樣。譬如部分載荷本身沒有集成1394接口卻需要用1394總線來傳輸數(shù)據(jù);或者幾個載荷需要共用一個1394總線接口;或者是載荷自身沒有帶微控制器等控制單元。并且各種載荷對外的數(shù)據(jù)接口也是各不相同的。這時就需要一種體積小,簡單并且易于擴充接口能的智能終端配合載荷一起工作。由于IEEE1394總線協(xié)議比較復雜,實際應用中大多數(shù)采用專用的1394總線芯片,面向?qū)S孟到y(tǒng)的1394芯片都支持微處理器接口。常見的1394總線設計采用的是微處理器加上1394總線芯片及外圍邏輯芯片,這種設計方案需要的芯片數(shù)量多,接口設備體積大,擴充接口功能實現(xiàn)起來比較復雜。

針對IEEE1394星載應用的實際需要,本文基于MC8051軟核,提出一種簡單、低功耗、小型化和易于擴展的IEEE1394智能終端設計方案,克服了以往1394總線接口硬件電路復雜、使用芯片多、體積大等缺點,并且可以很方便地擴展接口的其他功能。

2 系統(tǒng)實現(xiàn)方案

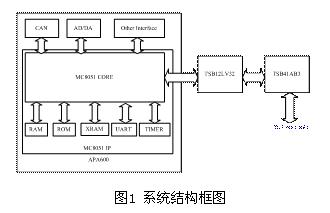

整個1934接口系統(tǒng)的框圖如圖1所示。采用的是Actel公司基于FLASH技術的ProASIC Plus系列FPGA芯片APA600。它具有單芯片上電即用、高性能和低功耗等特點[2]。由于上電即用,減小了電路板體積,有助于簡化電路設計。在方案試驗中使用的是TI公司的鏈路層芯片TSB12LV32[3]和物理層芯片TSB41AB[4]。TSB12LV32是一款高性能的通用IEEE1394a鏈路層芯片,用于在主控制器和1394物理層芯片以及連接到鏈路層DM口的外部設備之間的數(shù)據(jù)傳輸。它兼容IEEE1394-1995和P1394a標準,支持400、200和100Mbps的傳輸速率。提供可選的具有多種操作模式的8位/16位微控制器接口,最大支持60MHz。芯片內(nèi)部分別內(nèi)置了2K字節(jié)大小的通用接口FIFO和異步傳輸FIFO,用于微控制器接口和物理層接口之間的數(shù)據(jù)包傳送,8位/16位數(shù)據(jù)移動端口支持25MHZ下的等時、異步和數(shù)據(jù)流包的發(fā)送和接收。TSB41AB3是一款三端口兼容IEEE 1394-1995和P1394a標準400Mbps的物理層芯片.

在FPGA中整合了開源的兼容標準8051的微控制器IP核MC8051,將程序存儲器、程序存儲器、外部數(shù)據(jù)存儲器以及UART和定時器都集成在一片F(xiàn)PGA中。可以根據(jù)任務需要很方便地在FPGA內(nèi)定制其他所需要的接口和邏輯單元,譬如AD/DA控制,CAN總線等。

通過上述三個部分可以構成面向特定應用的完整的1394總線接口系統(tǒng)。

3 基于MC8051 IP的1394總線接口設計

3.1 Oregano Systems MC8051 IP Core¬[5]

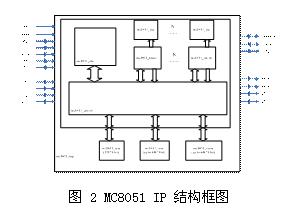

Oregano Systems公司發(fā)布的MC8051 IP Core是一個基于GUN LGPL的開源IP Core。它完全兼容標準的8051控制器,并且對其體系結(jié)構作了改進,在使用相同時鐘頻率情況下,將指令的執(zhí)行時間下降到1到4個時鐘周期,因此速度得到了十幾倍的提升,并且降低了功耗。MC8051模型是可綜合RTL風格,完全的同步設計,具有單一時鐘網(wǎng)絡,通過調(diào)整和修改VHDL代碼可以輕松地擴展其功能。具有128字節(jié)的片內(nèi)RAM,最高可以支持64K的ROM和RAM,并且集成了UART、定時器、中斷和4組8位的I/O口。

3.2 MC8051設計要點

3.2.1 MC8051參數(shù)配置

MC8051提供了參數(shù)化設計,通過修改VHDL中的參數(shù)值可以很輕易的修改內(nèi)部模型,例如UART個數(shù),Timer個數(shù),選擇乘法器等。在本應用系統(tǒng)中不需要涉及乘除法運算,因此在配置文件mc8051_p.vhd中將常數(shù)C_IMPL_MUL, C_IMPL_DIV以及C_IMPL_DA的設置為0。

3.2.2時鐘和RAM設計

MC8051 IP核在Actel的APA600上綜合得到的最高時鐘頻率為15MHZ左右,為了使用于調(diào)試的串口波特率誤差最小,用Actel Libero內(nèi)的SmartGen產(chǎn)生11.0592MHz的時鐘作為系統(tǒng)時鐘。

MC8051所需要的內(nèi)部RAM和RAM都應該調(diào)用器件的底層單元來實現(xiàn)。以128字節(jié)的內(nèi)部RAM為例。用SmartGen產(chǎn)生一個128*8大小的雙口RAM ram128_8.vhd,然后在mc8051_ram.vhd中例化。

3.2.3 ROM設計

MC8051完全兼容標準8051芯片,可采用KEIL uVision開發(fā)環(huán)境,建立工程文件時候Select Device選擇 Oregano Systems的8051 IP Core, 然后編譯寫好的51程序,產(chǎn)生HEX文件。需要從HEX文件中得到程序數(shù)據(jù),這里簡單介紹一下HEX文件格式。HEX文件是由任意數(shù)量的十六進制記錄組成的,每個記錄包含5個域,他們以下面的格式排列[6]:

:llaaaatt[dd…]cc

HEX文件都是由冒號開頭的,ll是數(shù)據(jù)長度域,表示記錄中數(shù)據(jù)字節(jié)的個數(shù);aaaa為地址域,標識記錄中數(shù)據(jù)字節(jié)的開始地址;tt是記錄類型域,51程序產(chǎn)生的hex文件只有兩種記錄類型,包括數(shù)據(jù)記錄(00)和文件結(jié)束記錄(01);dd是數(shù)據(jù)域,表示一個字節(jié)的數(shù)據(jù)

選用的Actel APA系列FPGA沒有底層的ROM單元,因此用VHDL設計實現(xiàn)ROM。通過了解了HEX文件的格式,編寫了從HEX文件讀取數(shù)據(jù)和地址信息,然后生成mc8051_rom.vhd文件,其中程序數(shù)據(jù)以常數(shù)的形式存在數(shù)組文件中。

3.2.4 MC8051與TSB32LV32之間的接口

鏈路層芯片微處理器接口包括16位寬的數(shù)據(jù)總線以及7位寬的地址總線。可以通過設置鏈路層芯片的COLDFIRE,M8BIT_SIZ0,MCMODE_SIZE這三個端口的狀態(tài),可以得到微處理器接口的各種不同操作模式,本設計中設置成16位MCS-MCA握手模式。

在系統(tǒng)頂層文件中對MC8051_top進行例化,連接MC8051與1394鏈路層芯片TSB12LV32。

MC8051的4組I/O口都是將輸入和輸出分開的,所以每組都可以配置成輸入和輸出。我們通過MCS和MWR來控制DM 和P1、P2口的連接。

3.3 基于MC8051的1394總線控制實現(xiàn)

MC8051通過TSB12LV32的微控制器接口實現(xiàn)對鏈路層和物理層內(nèi)部寄存器的讀取和設置,其中對鏈路層芯片的寄存器讀寫直接通過微控制器接口操作,而對物理層芯片寄存器讀寫是通過對鏈路層24H的Phy Access Register讀寫實現(xiàn)。

1394芯片部分內(nèi)部寄存器需要在系統(tǒng)上電的時候初始化或者在運行時候進行設置,一些則需要在運行時被監(jiān)視以決定系統(tǒng)狀態(tài),而鏈路層內(nèi)部的異步發(fā)送FIFO和通用接收FIFO也是通過讀寫寄存器來訪問的。因此正確讀寫寄存器是1394接口實現(xiàn)中非常重要的一步。

通過正確設置控制寄存器,DM口控制器寄存器等內(nèi)部寄存器便可以實現(xiàn)1394總線的各種傳輸模式的收發(fā)。

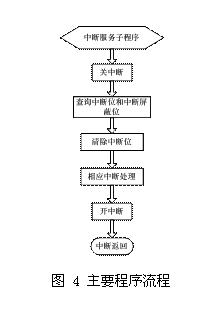

對1394芯片的控制另外一個主要部分是對中斷的響應和處理。將TSB12LV32芯片的INT管腳與MC8051的int0相連,通過int0的下跳沿檢測中斷發(fā)生。TSB12LV32芯片中有兩個寄存器是和中斷相關的。設置10H的中斷屏蔽寄存器中相應的某一位為1,則的0CH中斷寄存器響應位便跳變?yōu)楦唠娖剑瑫r產(chǎn)生相應的中斷。當有中斷發(fā)生的時候,INT管腳變低電平,而清除中斷則需要往中斷寄存器相應位寫入1。因此我們在中斷發(fā)生時候,可以通過讀取中斷寄存器的值查看發(fā)生了哪種中斷,然后做出正確的響應。

主要程序的流程圖如下:

4 結(jié)論

我們根據(jù)本文介紹的方案,設計和研制了基于mc8051的1394總線接口。經(jīng)過測試,1394總線系統(tǒng)工作正常。該總線接口具有集成度高,體積小,傳輸速率高等特點,同時可以根據(jù)實際任務需要很方便的擴充接口功能。本文介紹的方案對與1394總線接口的研究開發(fā)具有借鑒意義。

本文作者創(chuàng)新點:將MC8051軟核應用與星載智能1394終端設計。